本部分,,我們就跟隨作者一起看看Intel StraTIx10 NX和Nvidia在這個領(lǐng)域的利器T4以及V100之間的對比,過程分為芯片級對比以及系統(tǒng)級對比,。

本部分一起先來看看芯片級對比

首先來看下我們的GPU對手——Nvidia T4和V100分別有320個和640個張量核(專門用于AI工作負(fù)載的矩陣乘法引擎)

Nvidia Tesla T4

Nvidia Tesla V100

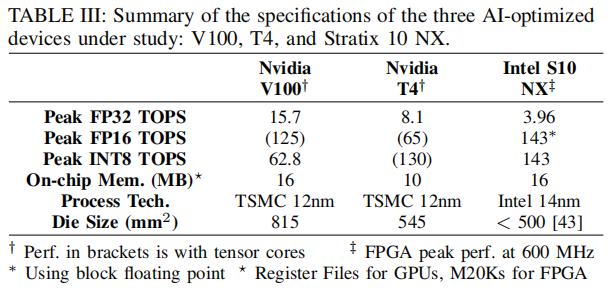

下面表格總結(jié)了與StraTIx10 NX和這些同代工藝GPU的關(guān)鍵指標(biāo)對比,。 就die尺寸來說,V100是Nvidia最大的12nm GPU,幾乎比T4大50%,,而StraTIx10 NX比兩種GPU都小,。

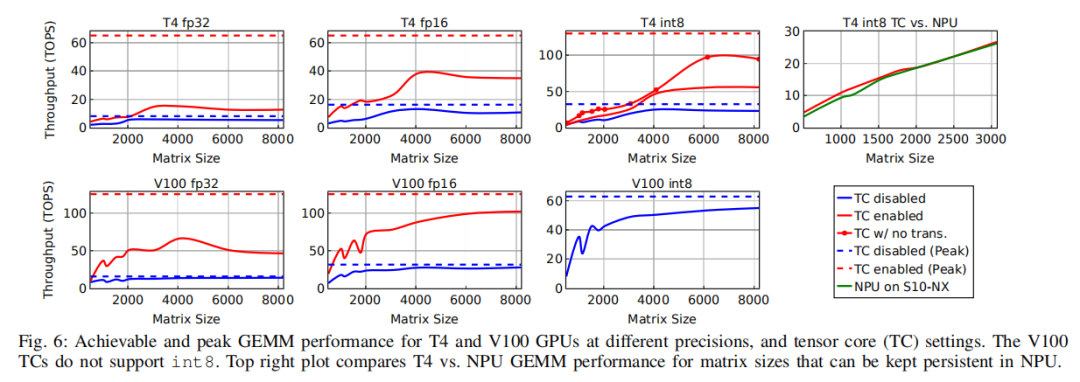

首先,文章使用GPU最擅長處理的工作負(fù)載:通用矩陣乘(GEMM)來跑GPU的benchmark(什么是GEMM請移步https://spaTIal-lang.org/gemm),,為了測量最佳的GPU性能,,對每個器件使用最新的library,這些庫不會出錯,,并且分別在使用和不使用張量核的情況下測試性能,。對于fp32和fp16實驗,分別使用CUDA10.0和10.2的CuBLAS庫進(jìn)行V100和T4,。對于int8,,我們使用CUDA10.2中的cuBLASLt庫,這樣可以比cuBLAS庫獲得更高的int8性能,。文章使用Nvidia的官方(高度優(yōu)化)的cuDNN kernel來處理DL工作負(fù)載,,并且分別對V100和T4使用了從cuDNN7.6.2和7.6.5。 (cuBLAS API,,從cuda6.0開始,;cuBLASLt API,從cuda10.1開始)

cuDNN庫不支持int8計算kernel,,但它們支持將所有模型權(quán)重保存在片上內(nèi)存中,。對于每個工作負(fù)載、問題大小和序列長度,,文章在兩種GPU上運行了所有可能的配置組合,,如精度{fp32、fp16,、int8},、計算樣式{persistent、non-persistent},、張量核心設(shè)置{enable,、disable}。然后,,選擇最佳的性能,,來和Stratix10 NX的NPU進(jìn)行比較。 這里因為是芯片級對比,,所以只考慮了芯核的計算效率,,不包括任何初始化、芯核啟動或主機(jī)-GPU數(shù)據(jù)傳輸開銷,。

下圖給出了T4和V100 GPU上fp32,、fp16和int8精度的GEMM benchmark測試結(jié)果,。結(jié)果表明,相對于張量核禁用情況(藍(lán)線),,啟用張量核(紅線) 可以顯著提高GPU在GEMM上的性能,。

然而,一個普遍的趨勢是,,張量核雖然是為GEMM設(shè)計的,,但在矩陣大小為2048或以下情況時的利用效率明顯不如峰值情況(紅色虛線)。因此要實現(xiàn)高利用率,,除非工作負(fù)載中的矩陣大小非常大,,而這在實際DL工作負(fù)載中并不常見。T4和V100上的張量核都不支持fp32的精度,,而是在執(zhí)行乘法運算之前,,將fp32數(shù)據(jù)轉(zhuǎn)換為fp16。相對于純fp16 GEMM,,這種數(shù)據(jù)轉(zhuǎn)換開銷降低了張量核性能,。另一個有趣的情況是,當(dāng)T4張量核在int8模式下工作時,,它們需要將輸入矩陣從標(biāo)準(zhǔn)的行/列主要格式轉(zhuǎn)換為特定于張量核的布局,。因此,即使在處理非常大的8192×8192矩陣時,,在張量核(沒有標(biāo)記的紅線)上實現(xiàn)的int8性能還不到峰值性能的45%,。

為了更好地理解這種數(shù)據(jù)轉(zhuǎn)換的開銷,文章還進(jìn)行了一個額外的實驗,,在這個實驗中,,對張量核進(jìn)行了特殊布局(帶有標(biāo)記的紅線)。即使不算矩陣布局變化的開銷,,對于4096×4096及以下的矩陣大小,,張量核利用率也小于40%,在6144×6144矩陣中利用率達(dá)到最高為72%,。

下面來看看FPGA上的情況,,上圖(Fig.6)的右上角那張圖比較了Stratix10 NX上的NPU性能與具有int8張量核的T4 GPU的性能。為了公平地比較,,文章禁用了NPU兩個輸入矩陣其中一個的矩陣布局變換,,只保留了對另一個輸入以及輸出矩陣的布局變換(因為NPU以標(biāo)準(zhǔn)格式使用和生成這些矩陣)。

雖然NPU是為矩陣向量運算而設(shè)計的,,但它在GEMM工作負(fù)載上仍然實現(xiàn)了與T4相似的性能,其矩陣大小從512到3072不等(最大的矩陣可以fit進(jìn)片上BRAM),。

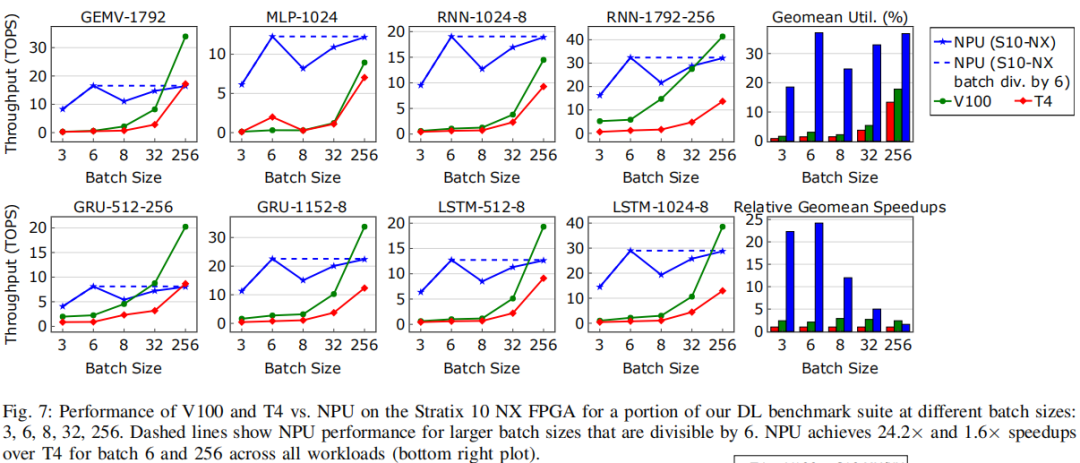

最后,,一起看看頂級FPGA和GPU的PK結(jié)果,。下圖(Fig.7)將文章在Stratix10 NX上增強型NPU的性能與T4和V100的最佳性能進(jìn)行比較。對于比較小的batch-3和batch-6情況,,F(xiàn)PGA性能總是顯著高于兩個GPU,。FPGA在batch-6(其設(shè)計為:雙核batch-3)中表現(xiàn)最好,平均性能分別是T4和V100的24.2x和11.7x,。

與batch-6相比,,F(xiàn)PGA在batch-3上的性能較低,因為兩個核中的一個完全空閑,。然而,,它仍然比T4和V100分別平均快了22.3x和9.3x。在batch size高于6時,,如果batch size不能被6整除,,則NPU可能不能被充分利用。例如,,在batch size為8,、32和256的情況下,NPU最多可以達(dá)到其batch-6性能的67%,、89%和99%,,而batch size為12、36和258(上圖中的虛線所示)可以達(dá)到100%的效率,。在32輸入的中等batch size情況下,,NX仍然比T4具有更好的性能,并且與V100性能相當(dāng),。

即使在比較大的batch size情況下,,NX的性能也比T4高58%,只比die size更大(大將近一倍)的V100低30%,。這些結(jié)果表明,,人工智能優(yōu)化的FPGA在低batch實時推理中不僅可以實現(xiàn)比GPU好一個數(shù)量級的性能,而且可以在放寬延遲約束下的高batch推理中和GPU匹敵,。上圖(Fig.7)中的右下角圖總結(jié)了不同batch size情況下NX相對于CPU的平均加速情況,。

上圖(Fig.7)中的右上角圖顯示了與不同batch大小下的兩個GPU相比,NX的平均利用率,。NX在batch-6中的平均利用率為37.1%,,而T4和V100分別僅為1.5%和3%。GPU張量核并非直接互連,,它們只能接收來自本地核內(nèi)寄存器文件的輸入,。因此,每個GPU張量核都必須發(fā)送它的partial result到全局內(nèi)存中,,并與其他張量核同步,,以結(jié)合這些partial result,。然后GPU從全局內(nèi)存中讀取組合好的矢量來執(zhí)行進(jìn)一步的操作,如激活函數(shù)(activation functions),。

較高的batch size可以攤銷這種同步延遲,,但即使在batch-256情況下,T4和V100的利用率分別只有13.3%和17.8%,。 另一方面,,F(xiàn)PGA在架構(gòu)上也更具優(yōu)勢,其在張量塊之間有專用的用來做減法的互連,, FPGA的可編程布線資源還允許將MVU tile和矢量單元級引擎級聯(lián)起來進(jìn)行直接通信,,減少了像GPU中那樣必須通過內(nèi)存通信的情況。

綜上可以看到,,F(xiàn)PGA依靠架構(gòu)優(yōu)勢和超高的資源利用率,,在AI性能PK上對GPU形成了強勁挑戰(zhàn)。下一篇,,我們再來一起看看從系統(tǒng)角度,,F(xiàn)PGA和GPU的對比情況以及功耗方面的分析。

更多信息可以來這里獲取==>>電子技術(shù)應(yīng)用-AET<<