1965 年,英特爾聯(lián)合創(chuàng)始人戈登·摩爾預(yù)測(cè),芯片上的晶體管數(shù)量大約每?jī)赡攴环杀旧仙群苄 _@一預(yù)測(cè)被稱為摩爾定律,如圖 1 所示。器件上的晶體管或組件越多,每個(gè)器件的成本就會(huì)降低,而每個(gè)器件的性能就會(huì)提高。

圖 1:“將更多組件塞進(jìn)集成電路”的原始圖表

在過(guò)去兩年中,由 COVID-19 大流行引發(fā)的世界數(shù)字化速度飆升,而半導(dǎo)體行業(yè)及其創(chuàng)新促成了這種增強(qiáng)的轉(zhuǎn)型。

英特爾首席執(zhí)行官 Pat Gelsinger 分享道:“技術(shù)對(duì)人類來(lái)說(shuō)從未像現(xiàn)在這樣重要。一切都在變得數(shù)字化,而我們擁有四個(gè)關(guān)鍵的superpowers 。 ” 分別是無(wú)處不在的計(jì)算、云到邊緣的基礎(chǔ)設(shè)施、無(wú)處不在的連接和人工智能——這將超越和改變世界。

目前,我們認(rèn)為對(duì)計(jì)算的需求沒有盡頭,更多的計(jì)算繼續(xù)推動(dòng)行業(yè)進(jìn)行更多創(chuàng)新。例如,世界每天產(chǎn)生近 270,000 PB的數(shù)據(jù)。我們預(yù)計(jì),到本十年末,我們所有人平均將擁有 1 petaflop的計(jì)算量和 1 PB 的數(shù)據(jù),距離不到 1 毫秒。 這種對(duì)計(jì)算能力越來(lái)越強(qiáng)的需求是推動(dòng)行業(yè)保持摩爾定律步伐的動(dòng)力。

40 多年來(lái),英特爾工程師不斷創(chuàng)新,將越來(lái)越多的晶體管擠入更小的芯片上,以保持摩爾定律的步伐。在 2010 年代中后期,業(yè)界曾多次預(yù)測(cè)“摩爾定律已死”。套用一句名言,我覺得摩爾定律消亡的報(bào)道被夸大了。創(chuàng)新并未消亡,我們將一如既往地通過(guò)創(chuàng)新——工藝創(chuàng)新、封裝創(chuàng)新和架構(gòu)創(chuàng)新來(lái)維持摩爾定律。一如既往,這將是一個(gè)挑戰(zhàn)——英特爾將迎接挑戰(zhàn)。

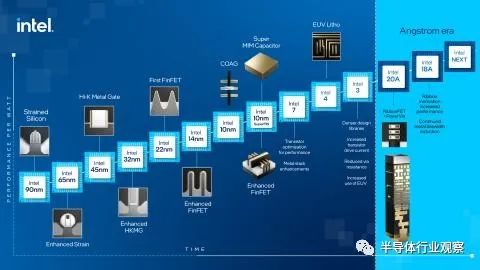

圖 2:隨時(shí)間推移的晶體管創(chuàng)新

今日創(chuàng)新:制程

英特爾在追求摩爾定律的基礎(chǔ)工藝創(chuàng)新方面有著悠久而豐富的歷史,如圖 2 所示。在芯片上的特征縮小到原子尺寸的過(guò)程中,英特爾工程師和科學(xué)家不斷面臨挑戰(zhàn)——然后克服。憑借高 k 金屬柵極技術(shù)、三柵極 3D 晶體管和應(yīng)變硅等發(fā)明,英特爾始終如一地提供突破性技術(shù),以跟上摩爾定律的步伐。到 2000 年代后期,隨著物理尺寸的不斷縮小,業(yè)界意識(shí)到需要其他創(chuàng)新領(lǐng)域來(lái)跟上步伐,包括材料科學(xué)、新工藝架構(gòu)和設(shè)計(jì)技術(shù)協(xié)同優(yōu)化 (DTCO)。

英特爾下一個(gè)偉大的架構(gòu)創(chuàng)新是 RibbonFET,這是我們實(shí)現(xiàn)的環(huán)柵 (GAA) 晶體管,這將與Intel 20A工藝 一起推出。RibbonFET 代表了我們自 FinFET 以來(lái)的第一個(gè)新晶體管架構(gòu)。RibbonFET 在更小的占位面積內(nèi)以相同的驅(qū)動(dòng)電流提供更快的晶體管開關(guān)速度。同時(shí),我們還提供業(yè)界首個(gè)背面供電架構(gòu) PowerVia。以前,電源來(lái)自芯片頂部,并與信號(hào)互連“競(jìng)爭(zhēng)”。通過(guò)分離電源和信號(hào),您可以更有效地使用金屬層,因?yàn)樾枰龀龅臋?quán)衡更少。這會(huì)提高性能。下一代極紫外 (EUV) 光刻技術(shù),即高數(shù)值孔徑或“High NA”,進(jìn)一步提高了分辨率并減少了誤差,通過(guò)增加設(shè)計(jì)規(guī)則的靈活性來(lái)降低流程復(fù)雜性。英特爾與 ASML 和其他生態(tài)系統(tǒng)合作伙伴密切合作,率先將這項(xiàng)技術(shù)投入大批量生產(chǎn)。

這些例子只是開始。在 Intel 20A 和 Intel 18A 引入RibbonFET 和 PowerVia 之后,英特爾新的后續(xù)工藝節(jié)點(diǎn)已經(jīng)在開發(fā)中,這些工藝在功率、性能和密度方面提供了額外的收益。這些收益是通過(guò)多項(xiàng)創(chuàng)新實(shí)現(xiàn)的,包括后端金屬電阻和電容的改進(jìn)、晶體管架構(gòu)和庫(kù)架構(gòu)的改進(jìn)。正如我們?cè)?2021 年 7 月所說(shuō),隨著我們實(shí)施這些創(chuàng)新和其他創(chuàng)新,我們預(yù)計(jì)到 2024 年實(shí)現(xiàn)晶體管性能比,到 2025 年則能實(shí)現(xiàn)領(lǐng)先地位。

圖 3:隨時(shí)間推移的封裝創(chuàng)新

今日創(chuàng)新:封裝

封裝的作用及其對(duì)摩爾定律縮放的貢獻(xiàn)正在演變。直到 2010 年代,封裝的主要作用是在主板和硅片之間路由電源和信號(hào),并保護(hù)硅片。那個(gè)時(shí)代的每一次演變——從引線鍵合和引線框架封裝,到陶瓷基板上的倒裝芯片技術(shù),再到有機(jī)基板的采用和多芯片封裝的引入——都帶來(lái)了連接數(shù)量的增加。這些連接支持硅中的更多功能,這是摩爾定律縮放所需的。封裝是實(shí)現(xiàn)摩爾定律好處的載體。(參見圖 3。)

展望未來(lái),隨著我們進(jìn)入先進(jìn)封裝時(shí)代,我們看到我們的封裝帶來(lái)了晶體管密度的提升。甚至 Gordon 本人也理解封裝的重要性,并在他的原始論文中說(shuō):“用單獨(dú)封裝和互連的較小功能構(gòu)建大型系統(tǒng)可能會(huì)更經(jīng)濟(jì)。” 隨著我們進(jìn)入高級(jí)封裝時(shí)代,這些 2D 和 3D 堆疊技術(shù)為架構(gòu)師和設(shè)計(jì)師提供了進(jìn)一步增加每個(gè)器件的晶體管數(shù)量的工具,并將有助于摩爾定律所需的微縮。

例如,我們的嵌入式多芯片互連橋 (EMIB) 技術(shù)允許設(shè)計(jì)人員再次套用 Gordon 的話——在封裝中“塞入更多晶體管”。這使設(shè)計(jì)人員能夠遠(yuǎn)遠(yuǎn)超過(guò)單片硅的尺寸限制。EMIB 還支持在一個(gè)封裝中使用來(lái)自不同工藝節(jié)點(diǎn)的硅片,從而允許設(shè)計(jì)人員為該特定 IP 選擇最佳工藝節(jié)點(diǎn)。英特爾的 Foveros 技術(shù)建立了業(yè)界第一個(gè)有源邏輯硅堆疊能力,創(chuàng)造了在三維空間中添加邏輯晶體管的能力。這兩項(xiàng)成就都代表了我們?nèi)绾卧诿總€(gè)封裝中提供越來(lái)越多的晶體管的方式發(fā)生了顯著變化。結(jié)合起來(lái),這些技術(shù)可以實(shí)現(xiàn)前所未有的集成水平。例如,老橋,

我們即將推出的 Foveros 演進(jìn)——Foveros Omni 和 Foveros Direct——提供了新的擴(kuò)展、新的互連技術(shù)和新的混合搭配功能。

Foveros Omni 進(jìn)一步將互連間距擴(kuò)大到 25 微米,并增加了多個(gè)基礎(chǔ)芯片的選項(xiàng)。與 EMIB 相比,密度大約增加了 4 倍,同時(shí)也擴(kuò)展了我們混合和匹配基礎(chǔ)瓷磚的能力。

Foveros Direct 引入了無(wú)焊直接銅對(duì)銅鍵合,可實(shí)現(xiàn)低電阻互連和亞 10 微米凸點(diǎn)間距。由此產(chǎn)生的互連能力為功能性芯片分區(qū)開辟了新的視野,這是以前無(wú)法實(shí)現(xiàn)的,并且能夠垂直堆疊多個(gè)有源硅層。隨著這些技術(shù)(和其他技術(shù))進(jìn)入市場(chǎng),會(huì)給芯片設(shè)計(jì)師維持摩爾定律提供支持。

圖 4:主要研究領(lǐng)域

天的創(chuàng)新:組件研究

正如我之前提到的,我相信創(chuàng)新以及最終用戶的需求推動(dòng)了摩爾定律的發(fā)展。英特爾的組件研究專注于三個(gè)關(guān)鍵研究領(lǐng)域(參見圖 4),為未來(lái)更強(qiáng)大的計(jì)算提供基本構(gòu)建模塊。我們正在進(jìn)行一整套研究,這讓我們有信心在未來(lái)十年或更長(zhǎng)時(shí)間內(nèi)保持摩爾定律。推動(dòng)摩爾定律的未來(lái)創(chuàng)新僅限于我們的想象力。

最近,在 2021 年 IEEE 國(guó)際電子設(shè)備會(huì)議 (IEDM) 上,我們概述了未來(lái)創(chuàng)新的幾個(gè)領(lǐng)域。

我們研究的一個(gè)重點(diǎn)是在同一領(lǐng)域提供更多晶體管的擴(kuò)展技術(shù)。這包括創(chuàng)新的光刻技術(shù)進(jìn)步,例如分子定向自組裝 (DSA),以提高線邊緣粗糙度和邊緣放置精度。 我們還研究只有幾個(gè)原子厚的新型材料,以制造更薄的晶體管,從而縮小它們的整體尺寸。

除了這些創(chuàng)新之外,我們正在建立可行的能力,可以將晶體管垂直堆疊在同一塊硅片上,或者使用先進(jìn)的封裝技術(shù)(如混合鍵合和不斷減小的垂直界面間距)作為小芯片。以新材料、晶體管架構(gòu)創(chuàng)新、光刻技術(shù)突破和封裝發(fā)明為自由度,設(shè)計(jì)師只會(huì)受限于他們的想象力。

隨著我們通過(guò)擴(kuò)展實(shí)現(xiàn)更強(qiáng)大的計(jì)算,我們需要為硅帶來(lái)新的功能并擴(kuò)展其極限。通過(guò)集成新材料,我們可以更高效地提供電力并滿足對(duì)內(nèi)存的更大需求。我們還在研究鐵電和反鐵電材料,它們可以根據(jù)不同類型的物理特性保持其電荷狀態(tài),而無(wú)需依賴低泄漏晶體管。我們發(fā)明了一種基于鐵電材料獨(dú)特物理特性的新型存儲(chǔ)器架構(gòu),通過(guò)使用一個(gè)具有多個(gè)并聯(lián)電容器的存取晶體管來(lái)顯著提高位密度。鐵電存儲(chǔ)器是高速緩存和主存儲(chǔ)器之間嵌入式密集存儲(chǔ)器層的有力候選者。

我們也在擁抱量子領(lǐng)域,不僅僅是以量子計(jì)算的形式,而是通過(guò)探索物理和材料科學(xué)中的新概念,這些概念有朝一日可能會(huì)徹底改變世界的計(jì)算方式。摩爾定律的長(zhǎng)期發(fā)展需要克服當(dāng)前基于 CMOS 計(jì)算的功耗要求的指數(shù)增長(zhǎng)。 為了繼續(xù),將需要在環(huán)境室溫下擴(kuò)展在材料(稱為量子材料)中使用量子效應(yīng)的超低功耗解決方案。

在 2021 年的 IEDM 上,我們報(bào)告了超越 CMOS 器件研究的一個(gè)巨大里程碑:磁電自旋軌道邏輯器件的首次功能演示,其讀寫組件在室溫下正常工作。自旋軌道輸出模塊和磁電輸入模塊都集成在器件中,通過(guò)施加的輸入電壓實(shí)現(xiàn)磁化狀態(tài)反轉(zhuǎn)。憑借其實(shí)現(xiàn)更高功能多數(shù)門(與 NAND 和 NOR 相比)的能力,形成超低功耗多數(shù)門的三個(gè) MESO 器件可以實(shí)現(xiàn) 1 位加法器,否則需要 28 個(gè) CMOS 晶體管。

圖 5:摩爾定律每個(gè)器件的晶體管數(shù)量:過(guò)去、現(xiàn)在、未來(lái)

綜上所述

摩爾定律預(yù)測(cè)每個(gè)器件的晶體管數(shù)量將每?jī)赡攴环D柖梢恢笔怯蓜?chuàng)新驅(qū)動(dòng)的。圖 5 展示了我們回顧過(guò)去、現(xiàn)在和未來(lái)時(shí)每個(gè)器件的晶體管數(shù)量。在最初的 40 年里,收益主要來(lái)自我們制程中的創(chuàng)新。

展望未來(lái),收益將來(lái)自工藝和封裝方面的創(chuàng)新。我們的工藝將繼續(xù)實(shí)現(xiàn)歷史性的密度改進(jìn),而我們的 2D 和 3D 堆疊技術(shù)為架構(gòu)師和設(shè)計(jì)師提供更多工具來(lái)增加每個(gè)設(shè)備的晶體管數(shù)量。

當(dāng)我們期待諸如 High NA、RibbonFET、PowerVia、Foveros Omni 和 Direct 等創(chuàng)新技術(shù)時(shí),我們看到創(chuàng)新沒有盡頭,因此摩爾定律也沒有盡頭。

總而言之,當(dāng)我們考慮所有各種工藝和先進(jìn)封裝創(chuàng)新時(shí),有許多選擇可以繼續(xù)按照客戶要求的節(jié)奏將每個(gè)器件的晶體管數(shù)量翻倍。只有當(dāng)創(chuàng)新停止時(shí),摩爾定律才會(huì)停止,而英特爾在工藝、封裝和架構(gòu)方面的創(chuàng)新繼續(xù)有增無(wú)減。

到 2030 年,我們?nèi)匀粓?jiān)定地希望在單個(gè)設(shè)備中提供大約 1 萬(wàn)億個(gè)晶體管。