級結(jié)技術(shù)(superjunction),利用電荷補(bǔ)償?shù)姆绞绞估诰樱‥pitaxial layer)內(nèi)的垂直電場分布均勻,有效減少磊晶層厚度及其造成的通態(tài)電阻。但是采用超級結(jié)技術(shù)的高壓功率晶體,其最大耐壓都在1000V以下。如果要能夠耐更高的電壓,就必須采用碳化硅材料來制造功率晶體。以碳化硅為材料的功率晶體,在碳化硅的高臨界電場強(qiáng)度之下,即使相同耐壓條件之下,其磊晶層的厚度約為硅材料的1/10,進(jìn)而其所造成的通態(tài)電阻能夠有效被降低,達(dá)到高耐壓低通態(tài)電阻的基本要求。

在硅材料的高壓超級結(jié)功率晶體中,磊晶層的通態(tài)電阻占總通態(tài)電阻的90%以上。所以只要減少磊晶層造成的通態(tài)電阻,就能有效降低總通態(tài)電阻值;而碳化硅功率晶體根據(jù)不同耐壓等級,通道電阻(Channel resistance, Rch)占總通態(tài)電阻的比值也有所不同。例如在650V的碳化硅功率晶體中,通道電阻( Channel resistance,Rch)占總通態(tài)電阻達(dá)50%以上,因此要有效降低總通態(tài)電阻最直接的方式就是改善通道電阻值。 由通道電阻的公式,如式(1)可以觀察到,有效降低通道電阻的方法有幾個方向:減少通道長度L、減少門極氧化層厚度dox、提高通道寬度W、提高通道的電子遷移率μch、降低通道導(dǎo)通閾值電壓VT,或者提高驅(qū)動電壓VGS。然而幾種方法又分別有自身的限制。

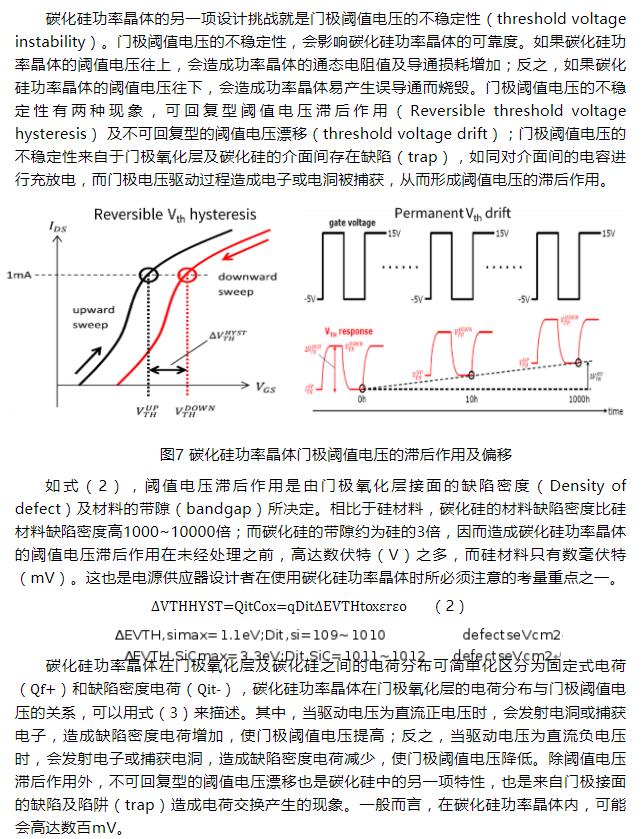

實際上除了少數(shù)應(yīng)用的功率晶體在電路工作時,只有一次的開或關(guān)動作,能以直流電壓驅(qū)動外,大部份交換式電源供應(yīng)器內(nèi)用于主開關(guān)的功率晶體都會采用高頻交流電壓驅(qū)動。從實際測試的結(jié)果來看,當(dāng)在不同的門極閾值電壓之下,會有不同的門極截止電壓設(shè)計要求:提供較低門極閾值電壓的碳化硅功率晶體的供應(yīng)商,會建議截止時采用負(fù)電壓驅(qū)動,以避免橋式相連的功率晶體在上下交互導(dǎo)通及截止時,減少受到寄生電容效應(yīng)及門極回路電感在門極端產(chǎn)生感應(yīng)電壓而產(chǎn)生上下管間的誤導(dǎo)通及燒毀;反之對于具有較高門極閾值電壓的碳化硅功率晶體而言,并不需要采用負(fù)電壓驅(qū)動,使用負(fù)電壓驅(qū)動不僅會增加電路的復(fù)雜度,也會加大門極閾值電壓往上的漂移量,如圖8所示,使用較高的正電壓或負(fù)電壓時,隨著功率晶體使用時間的增加,門極閾值電壓往上漂移的增量會更明顯,進(jìn)而造成功率晶體的通態(tài)電阻值隨著使用時間的累積而慢慢增加。各品牌碳化硅功率晶體的門極閾值電壓的漂移量都有不同的數(shù)值,用戶在選用碳化硅功率晶體時必須先避免過高的正負(fù)電壓對門極閾值電壓帶來的負(fù)面影響。

綜上所述,目前碳化硅功率晶體的發(fā)展主要在于幾個方向:1.降低單位晶粒面積下的通態(tài)電阻;2.提高功率晶體門極可靠度3.在不影響驅(qū)動位準(zhǔn)的大前提下降低驅(qū)動電壓位準(zhǔn)。這些設(shè)計上的挑戰(zhàn),都由碳化硅功率晶體的設(shè)計者來構(gòu)思及突破,而主流的碳化硅功率晶體在結(jié)構(gòu)上分為兩大類,平面式及溝槽式的碳化硅功率晶體,平面式的碳化硅功率晶體受限于晶體缺陷及電子遷移速度,大多采用較低的臨界門極電壓,并建議在橋式電路中采用負(fù)電壓截止驅(qū)動電路 ,用以減少在橋式電路中功率晶體交互驅(qū)動時可能產(chǎn)生的可能的誤導(dǎo)通;反之溝槽式的碳化硅功率晶體,采用具有較高電子遷移速度的晶體平面做為通道,可以設(shè)計較高的臨界門極電壓,并且不需要任何的負(fù)電壓截止驅(qū)動電路。對于碳化硅功率晶體的用戶而言,驅(qū)動電路設(shè)計相對簡單,只需要提高驅(qū)動電壓到合適的電壓值,就能夠享受碳化硅功率晶體帶來的優(yōu)點。