當(dāng)下,雖說(shuō)摩爾定律有些失靈,但制程工藝依然在有條不紊地前行著。5nm節(jié)點(diǎn)工藝已經(jīng)量產(chǎn),臺(tái)積電的3nm也即將實(shí)現(xiàn)風(fēng)險(xiǎn)試產(chǎn),并于2022年實(shí)現(xiàn)量產(chǎn),而該公司的2nm工藝也已經(jīng)排上了試產(chǎn)和量產(chǎn)日程。下一步,就是要攻克1nm制程節(jié)點(diǎn)了,但從目前情況來(lái)看,1nm的研發(fā)還沒(méi)有成熟,還有諸多不確定因素,因此,其試產(chǎn)和量產(chǎn)何時(shí)能夠排上日程,還需要業(yè)界的共同努力。

對(duì)于先進(jìn)制程工藝(這里指10nm以下節(jié)點(diǎn))來(lái)說(shuō),其相對(duì)于較為成熟的制程來(lái)說(shuō),相關(guān)芯片制造的各種因素都是全新的,也是相當(dāng)具有挑戰(zhàn)性的。總體來(lái)看,要想量產(chǎn)出可用的先進(jìn)制程芯片,特別是3nm、2nm和1nm,制造工藝和制造設(shè)備就成為了最具挑戰(zhàn)性的因素,其中,制造工藝大致可分為晶體管架構(gòu)和材料,而制造設(shè)備的核心要素就是EUV光刻機(jī)。而以上這幾項(xiàng)都是頂尖技術(shù),特別是對(duì)于1nm而言,眼下這些技術(shù)還在研究階段,并未成熟,只有解決掉它們,1nm制程的量產(chǎn)才能真正提上日程。

晶體管架構(gòu)

目前,臺(tái)積電和三星都已經(jīng)實(shí)現(xiàn)了7nm和5nm制程的量產(chǎn),相應(yīng)的晶體管仍然采用FinFET架構(gòu),隨著向3nm和2nm的演進(jìn),F(xiàn)inFET已經(jīng)難以滿足需求,gate-all-around(GAA)架構(gòu)應(yīng)運(yùn)而生,其也被稱為nanosheet,而1nm制程對(duì)晶體管架構(gòu)提出了更高的要求。為了將nanosheet器件的可微縮性延伸到1nm節(jié)點(diǎn)處,歐洲研究機(jī)構(gòu)IMEC提出了一種被稱為forksheet的架構(gòu)。在這種架構(gòu)中,sheet由叉形柵極結(jié)構(gòu)控制,在柵極圖案化之前,通過(guò)在pMOS和nMOS器件之間引入介電層來(lái)實(shí)現(xiàn)。這個(gè)介電層從物理上隔離了p柵溝槽和n柵溝槽,使得n-to-p間距比FinFET或nanosheet器件更緊密。通過(guò)仿真,IMEC預(yù)計(jì)forksheet具有理想的面積和性能微縮性,以及更低的寄生電容。

此外,3D“互補(bǔ)FET”(CFET)也是1nm制程的晶體管方案。CFET技術(shù)的一個(gè)顯著特征是與納米片拓?fù)浣Y(jié)構(gòu)具有很強(qiáng)的相似性。CFET的新穎之處在于pFET和nFET納米片的垂直放置。CFET拓?fù)淅昧说湫偷腃MOS邏輯應(yīng)用,其中將公共輸入信號(hào)施加到nFET和pFET器件的柵極。

CFET器件的處理需要特別注意pFET和nFET的形成。用于pFET源/漏極的SiGe的外延生長(zhǎng)用于在溝道中引入壓縮應(yīng)變,以提高空穴遷移率。然后執(zhí)行pFET柵極氧化物和金屬柵極沉積。隨后,nFET源極/漏極節(jié)點(diǎn)的外延Si生長(zhǎng),隨后的柵極氧化物和金屬柵極沉積必須遵守現(xiàn)有pFET器件施加的材料化學(xué)約束。

在VLSI 2020上,IMEC展示了CFET器件的第一個(gè)實(shí)驗(yàn)概念證明,它是在單片工藝中制造的。該團(tuán)隊(duì)設(shè)法克服了這一復(fù)雜工藝方案的關(guān)鍵工藝挑戰(zhàn),即從襯底開(kāi)始,從下到上地加工CFET。在CFET中,對(duì)底層器件(如pFET)進(jìn)行加工后,再進(jìn)行晶圓鍵合,形成頂層器件(如nFET)溝道,然后對(duì)頂層器件進(jìn)行進(jìn)一步加工。CFET為頂層器件中使用的溝道材料提供了更靈活的選擇。

除了IMEC和臺(tái)積電之外,美國(guó)和中國(guó)大陸的相關(guān)研究機(jī)構(gòu)也在進(jìn)行1nm晶體管的研究,并取得了一定的成績(jī)。

例如,今年4月,湖南大學(xué)物理與微電子科學(xué)學(xué)院教授劉淵團(tuán)隊(duì)通過(guò)使用范德華金屬集成的方法,成功實(shí)現(xiàn)了1nm物理溝道長(zhǎng)度的垂直場(chǎng)效應(yīng)晶體管,為半導(dǎo)體器件性能的進(jìn)一步提升提供了新的思路。晶體管的物理溝道長(zhǎng)度,指的是晶體管內(nèi)源極與漏極之間的距離,物理溝道長(zhǎng)度是晶體管的一個(gè)關(guān)鍵性能指標(biāo):溝道長(zhǎng)度越短,性能越好。

與傳統(tǒng)的金屬沉積技術(shù)相比,范德華金屬集成可以實(shí)現(xiàn)原子級(jí)別平整的界面,從而保證超薄原子溝道近乎完美的平整度,進(jìn)而最大限度地減少漏電流的發(fā)生。因此,采用范德華金屬電極的器件,其器件的柵極調(diào)控和開(kāi)關(guān)比有大幅度提高。

劉淵教授團(tuán)隊(duì)發(fā)現(xiàn),具有5 nm溝道長(zhǎng)度的垂直晶體管展示出了三個(gè)數(shù)量級(jí)的開(kāi)關(guān)比,這比常規(guī)蒸鍍電極的器件高出了一個(gè)數(shù)量級(jí)以上。而通過(guò)將溝道長(zhǎng)度縮小到 0.65 nm,單層器件的開(kāi)關(guān)比有所下降,但范德華垂直晶體管依然展現(xiàn)出了本征的 N 型半導(dǎo)體特性,表明了短溝道效應(yīng)在原子尺度下依然沒(méi)有主導(dǎo)器件的性能。盡管在單層極限情況下器件展示出了一定的隧穿電流和短溝道效應(yīng),但他們依然證實(shí),范德華金屬電極可以實(shí)現(xiàn)具有器件功能的亞 1 nm垂直晶體管。

此外,中國(guó)科學(xué)院物理研究所研究團(tuán)隊(duì)構(gòu)建了尺寸小于1nm,由單個(gè)分子構(gòu)成的晶體管器件。其利用可控?zé)g電極的方法構(gòu)造了納米金屬電極對(duì),把單個(gè)酞菁錳分子嵌入其中,門電極對(duì)其中的多個(gè)分子軌道能量進(jìn)行靜電調(diào)控,首次在實(shí)驗(yàn)上報(bào)道了二階近藤效應(yīng)的演化方式,驗(yàn)證了數(shù)字重正化群計(jì)算方法中預(yù)言的線性關(guān)系。

材料

在先進(jìn)制程芯片的制造過(guò)程中,前道工序負(fù)責(zé)制造出相應(yīng)結(jié)構(gòu)的晶體管,而中間工序和后道工序則是將這些獨(dú)立的晶體管連接起來(lái),從而實(shí)現(xiàn)相應(yīng)的芯片功能和性能,這就需要用到各種半導(dǎo)體材料。

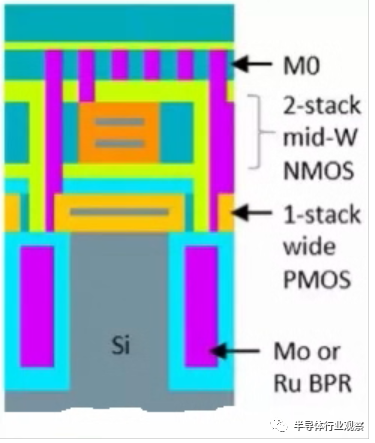

如前文所述,1nm制程需要用到forksheet,CFET晶體管架構(gòu),這些架構(gòu)對(duì)局部互連提出了新的要求,相應(yīng)地,后道工序需要采用新型材料(如釕(Ru)、鉬(Mo)和金屬合金),還需要降低中間工序的接觸電阻。

對(duì)于后道工序而言,金屬線和通孔的電阻和電容仍然是最關(guān)鍵的參數(shù)。解決這個(gè)問(wèn)題的一種方法是采用另一種金屬化結(jié)構(gòu),稱為“零通孔混合高度”。這種方案可以根據(jù)金屬線的應(yīng)用需求,靈活地將電阻換成電容。

對(duì)于中間工序而言,為了進(jìn)一步緩解布線擁擠并滿足新提出的晶體管結(jié)構(gòu)的要求,該工序需要進(jìn)一步創(chuàng)新。例如,在CFET中,需要為接觸柵極提供新的解決方案,現(xiàn)在,這對(duì)于nFET和pFET器件來(lái)說(shuō)是通用的。此外,高縱橫比的通孔把各種構(gòu)件互連起來(lái),這些構(gòu)件現(xiàn)在已經(jīng)擴(kuò)展到三維。但是,這些深通孔的主要寄生電阻需要降低。這可以通過(guò)引入先進(jìn)的觸點(diǎn)來(lái)實(shí)現(xiàn),例如使用釕。

最近,臺(tái)積電取得了一項(xiàng)成果,其與臺(tái)灣大學(xué)和美國(guó)麻省理工學(xué)院(MIT)合作,發(fā)現(xiàn)二維材料結(jié)合半金屬鉍(Bi)能達(dá)到極低的電阻,接近量子極限,可以滿足1nm制程的需求。

過(guò)去,半導(dǎo)體使用三維材料,這次改用二維材料,厚度可小于1nm(1~3層原子的厚度),更逼近固態(tài)半導(dǎo)體材料厚度的極限。而半金屬鉍的材料特性,能消除與二維半導(dǎo)體接面的能量障礙,且半金屬鉍沉積時(shí),也不會(huì)破壞二維材料的原子結(jié)構(gòu)。

1nm制程透過(guò)僅1 ~3層原子厚度的二維材料,電子從源極(source)走以二硫化鉬為材料的電子通道層,上方有柵極(gate)加壓電壓來(lái)控制,再?gòu)穆O(drain)流出,用鉍作為接觸電極的材料,可以大幅降低電阻并提高傳輸電流,讓二維材料成為可取代硅的新型半導(dǎo)體材料。

制造設(shè)備

1nm制程晶體管的制造,對(duì)EUV光刻機(jī)的依賴度很高,而在當(dāng)今全球范圍內(nèi),只有ASML一家公司具備這種設(shè)備的生產(chǎn)能力。

就在2020年底,與ASML有著密切合作關(guān)系的IMEC表示,ASML已經(jīng)完成了作為NXE:5000系列的高NA EUV曝光系統(tǒng)的基本設(shè)計(jì),但計(jì)劃于2022年實(shí)現(xiàn)商業(yè)化。

ASML一直與IMEC合作開(kāi)發(fā)光刻技術(shù),為了使用高NA EUV光刻工具開(kāi)發(fā)光刻工藝,在IMEC校園內(nèi)建立了一個(gè)新的“ IMEC-ASML高NA EUV實(shí)驗(yàn)室”。

除了使用EUV設(shè)備光刻1nm芯片之外,也會(huì)有一些不同的制造理念和方法。例如,早在2017年,美國(guó)布魯克海文國(guó)家實(shí)驗(yàn)室的科研人員就宣布實(shí)現(xiàn)了1nm工藝制造,他們成功制造了尺寸只有1nm的印刷設(shè)備,使用的是電子束印刷工藝而非傳統(tǒng)的光刻印刷技術(shù)。

科研人員使用了電子顯微鏡造出了比普通EBL(電子束印刷)工藝所能做出的更小的尺寸,電子敏感性材料在聚焦電子束的作用下尺寸大大縮小,達(dá)到了可以操縱單個(gè)原子的地步。他們?cè)斐龅倪@個(gè)工具可以極大地改變材料的性能,從導(dǎo)電變成光傳輸以及在這兩種狀態(tài)下交互。

1nm印刷使用的是STEM(掃描投射電子顯微鏡),被隔開(kāi)11nm,這樣一來(lái)每平方毫米就能實(shí)現(xiàn)1萬(wàn)億個(gè)特征點(diǎn)(features)的密度。不過(guò),實(shí)驗(yàn)室研發(fā)的技術(shù)并不代表能很快商業(yè)化,布魯克海文實(shí)驗(yàn)室的1nm工藝跟目前的光刻工藝有很多不同,比如使用的是電子束而非激光光刻,所用的材料也不是硅基半導(dǎo)體而是PMMA(聚甲基丙烯酸甲酯)。

結(jié)語(yǔ)

從實(shí)驗(yàn)室到產(chǎn)線量產(chǎn),1nm制程工藝需要攻克晶體管架構(gòu)、半導(dǎo)體材料,以及制造設(shè)備等幾道難關(guān)。從3nm和2nm的發(fā)展和量產(chǎn)節(jié)奏來(lái)看,或許到2025年,市場(chǎng)上就會(huì)出現(xiàn)1nm制程的樣片了。