前幾天IBM宣布開發(fā)出了世界上首款2納米芯片。此消息一出,立馬全網(wǎng)刷屏。

那么IBM 2納米芯片真的“貨真價實”么?帶著疑問,國外知名科技媒體semiwiki做了詳細(xì)的數(shù)據(jù)分析,最后的結(jié)論是IBM的2納米芯片更接近于臺積電的3納米!

semiwiki的分析原文如下:

作者:Scotten Jones

IBM公告中指出這款2納米芯片具有以下的特征:

在這里IBM的2nm制程號稱在150mm2(指甲蓋大小)的面積中塞入了500億個晶體管,平均每平方毫米為3.3億個。

柵極長度為12nm的44nm接觸式多節(jié)距(CPP)。

基于IBM正在使用水平納米片(HNS)的橫截面,可以使用Gate All Around(GAA)進行GAA的幾種方法。

HNS疊層構(gòu)建在氧化物層之上。

與最先進的7nm芯片相比,性能提高了45%或功耗降低了75%。

EUV圖案用于前端,允許HNS片的寬度在15納米到70納米之間變化。這對于調(diào)整電路的各個區(qū)域以實現(xiàn)低功耗或高性能以及SRAM單元是非常有用的。

這些薄片的厚度為5納米,三層堆疊。

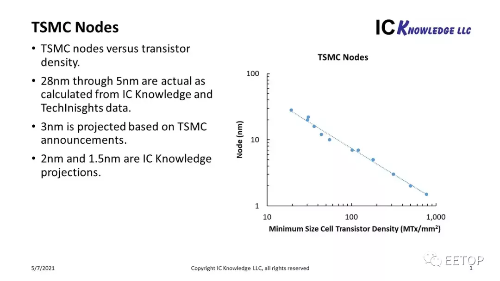

如IBM所說,這真的是“ 2nm”嗎?臺積電是目前生產(chǎn)工藝技術(shù)的領(lǐng)導(dǎo)者。我們繪制了TSMC節(jié)點名稱與晶體管密度的關(guān)系圖,并擬合了0.99 R2值的曲線,見圖1。

圖1. TSMC等效節(jié)點

使用曲線擬合,我們可以將晶體管密度轉(zhuǎn)換為臺積電等效節(jié)點(TEN)。使用曲線擬合,對于IBM宣布的333MTx / mm 2,我們得到2.9nm的臺積電等效節(jié)點。因此,我們認(rèn)為,IBM的這款2納米芯片,嚴(yán)格來說應(yīng)該是3nm節(jié)點,而不是2nm節(jié)點。

為了更詳細(xì)地將IBM公告與之前宣布的3nm工藝和預(yù)計的2nm工藝進行比較,我們需要進行一些估算。

從公告中我們知道CPP為44nm。

我們假設(shè)一個單擴散中斷(SDB),這將導(dǎo)致最密集的工藝。

查看公告中的橫截面,我們沒有看到埋入式電源軌(BPR),BPR是將HNS軌道高度降低到5.0所必需的,所以我們假設(shè)該工藝為6.0。

為了達到333MTx / mm 2,最小金屬間距必須為18nm,這是一個非常具有挑戰(zhàn)性的值,可能需要EUV多重曝光。

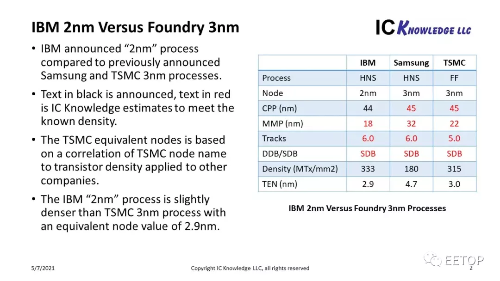

IBM 2nm對比代工廠的3nm

圖2將IBM 2nm設(shè)計與我們對三星和臺積電3nm工藝的估計進行了比較。我們知道三星也在制造HNS,而臺積電則選擇了3nm的FinFET。三星和臺積電都宣布了其3納米工藝相對于5納米工藝的密度改進,因此我們可以知道這三家公司的晶體管密度,并可以計算出這三家公司對應(yīng)的TEN(臺積電等效節(jié)點)。如前所述,IBM的TEN是2.9,而三星的TEN是4.7,臺積電的TEN是3.0,這再次證明了IBM 2納米工藝與臺積電3納米工藝相當(dāng),而三星得3納米則落后于臺積電。

圖2中紅色的數(shù)字是為實現(xiàn)公布的密度而估計的,我們假設(shè)所有公司都是SDB。臺積電的軌道高度最小,因為FinFET在沒有BPR的情況下可以有5.0的軌道高度,但HNS需要BPR來達到5.0,而BPR還沒有準(zhǔn)備好。

圖2. IBM 2nm與代工廠的3nm。

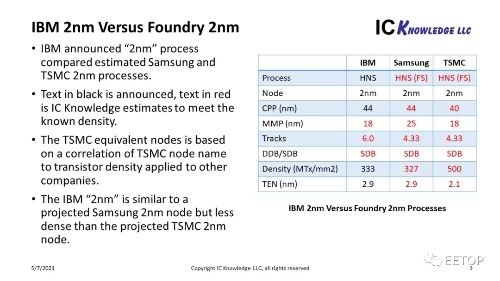

IBM 2nm對比代工廠的 2nm

我們還在圖3中預(yù)測了三星和臺積電的2納米工藝。我們預(yù)測這兩家公司都將使用BPR(BPR目前還沒有準(zhǔn)備好,但當(dāng)三星和臺積電在2023/2024年左右推出2納米工藝時可能會就緒)。我們還假設(shè)三星和臺積電將利用NHS(HNS(FS))架構(gòu)來達到4.33軌道高度,放寬一些其他收縮要求。然后我們根據(jù)公司最近的收縮趨勢預(yù)測出CPP和MMP。

圖3. IBM 2nm與Foundry 2nm。

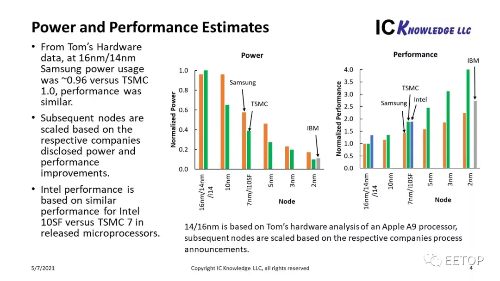

功耗與性能

在今年的ISS上,我估計了三星(Samsung)和臺積電(TSMC)的相對功率和性能,并提供了一些額外的英特爾性能數(shù)據(jù)。各節(jié)點的縮小趨勢是基于各公司公布的功率和性能估計以及14nm/16nm的可用比較。欲了解更多信息,請參見ISS的文章。(https://semiwiki.com/events/294639-iss-2021-scotten-w-jones-logic-leadership-in-the-ppac-era/)

由于IBM將其功率和性能改進與領(lǐng)先的7nm性能進行了比較,因此我可以將IBM的功率和性能放在我先前介紹的相同趨勢圖上,見圖4。

圖4.功率和性能(估計值)

IBM對HNS的使用大大降低了功率,使他們的2納米工藝比三星或臺積電的3納米工藝更省電,盡管我們相信一旦臺積電在2納米工藝中采用HNS,他們的功率將和IBM一樣好甚至更好。就性能而言,我們估計臺積電的3納米工藝的性能將超過IBM的2納米工藝。

正如ISS文章中討論的那樣,這些趨勢僅是估計值,并基于許多假設(shè),但這是我們可以匯總的最佳預(yù)測。

結(jié)論

在分析了IBM的公告后,我們認(rèn)為他們的 “2納米 ”工藝從密度角度看更像臺積電的3納米工藝,功耗更佳,但性能更差。IBM的公告令人印象深刻,目前這還僅僅還屬于實驗室階段,與臺積電的3納米工藝相比,只有在功耗方面有明顯的優(yōu)勢,而臺積電3納米工藝將在今年晚些時候進入風(fēng)險啟動階段,并在明年投產(chǎn)。

我們進一步相信,當(dāng)臺積電工藝在2023/2024左右投入生產(chǎn)時,它將在2nm的密度、功率和性能方面保持領(lǐng)導(dǎo)地位。