據(jù)行業(yè)內(nèi)知名媒體semiwiki報道,當(dāng)前被先進工藝節(jié)點的FinFET器件的下一個繼任者架將是一種被稱為“納米片”器件。

他們指出 ,與平面器件相比,F(xiàn)inFET的柵極橫穿鰭的三個側(cè)面,提供了改進的柵極至溝道靜電控制。而納米片器件的“GAA”特性在器件通道周圍的靜電控制方面則帶來了進一步的改進。這就帶來了更理想的亞閾值斜率或SS(subthreshold slope)。SS與器件柵極輸入電壓的變化有關(guān),該變化導(dǎo)致泄漏電流變化10倍。較小的SS意味著更快的器件開關(guān)速度,并且顯著 地減少了靜態(tài)源極/漏極泄漏電流和泄漏功耗。

另外,納米片裝置提供了更大的設(shè)計靈活性。FinFET器件寬度的拓撲是量化的(Weff?((2 * fin_height)+(fin_thickness))),而納米片器件的寬度由EUV光刻法定義(Weff?nanosheet_perimeter)。

有效的納米片寬度可以通過垂直堆疊多個通道來進一步擴展,而柵極材料完全圍繞著各個納米片。這個設(shè)計的靈活性和改進的設(shè)備特性使該技術(shù)顯得非常有吸引力。

然而,將納米片處理引入生產(chǎn)存在重大挑戰(zhàn)。以下只是其中的一部分:

1、隔離納米片設(shè)備溝通的各個“功能區(qū)”(“ribbons”)

納米片器件被制造在外延層中。水平器件板嵌入其他外延生長層中,例如,由不同組成的外延層(例如SiGe / Si / SiGe / Si / SiGe)夾在中間的硅層。(其中,Si和Ge之間晶體結(jié)構(gòu)的緊密相似性至關(guān)重要。)

納米片裝置“帶”( “ribbons” )的形成需要非常有選擇性的蝕刻工藝。去除上方和下方的外延層,同時不蝕刻剩余的器件溝道。對于多個堆疊的納米片,該蝕刻過程還需要是各向異性的,以使納米片之間的所有犧牲外延層材料被完全去除。

2、圍繞暴露的納米片帶(exposed nanosheet ribbons)的高K柵極氧化物電介質(zhì)需要非常均勻,并具有出色的附著力

氧化物缺陷密度和界面陷阱密度(對于注入的“熱”載流子)必須非常低。(氫氣環(huán)境中的退火步驟通常包含在設(shè)備工藝流程中。)

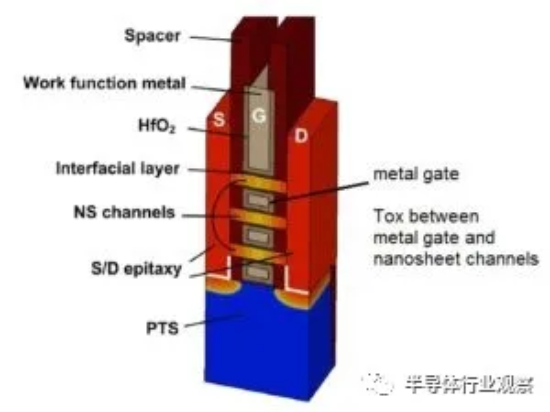

3、同樣,金屬柵材料堆疊需要均勻地沉積在整個結(jié)構(gòu)中,以完全包圍堆疊的sheets

柵極堆疊通常包括初始的金屬氧化物e “workfunction”層(例如TiN),然后是填充柵極體積的金屬(例如鎢)。(原子層沉積(ALD)確實是一項了不起的技術(shù)。)

4、需要在溝道附近制作一個低阻源極/漏極器件節(jié)點,以減小Rs和Rd

使用外延生長步驟(具有高的摻雜劑濃度)來增加溝道附近的S / D體積,該溝道通過側(cè)壁隔離氧化物適當(dāng)?shù)嘏c柵極隔離。(其他FET拓撲結(jié)構(gòu)也使用類似的凸起S / D外延步驟。)此外,S / D摻雜輪廓需要確保與第一級金屬的接觸電阻低。

5、“器件工程”需要在溝道材料中引入很大的應(yīng)變,以提高自由載流子遷移率,從而改善驅(qū)動電流

從平面到FinFET器件拓撲的幾代工藝中,已經(jīng)采用了多種技術(shù)將應(yīng)變引入溝道材料晶體中——拉伸應(yīng)變可提高nMOS電子遷移率,壓縮應(yīng)變可提高pMOS空穴遷移率。“ Stressor”材料介電層被添加到平面設(shè)備的頂部。凸起的S / D外延區(qū)域還將應(yīng)變傳遞到通道。

特別值得關(guān)注的是硅中電子與空穴遷移率之間的差異。

工藝開發(fā)工程師不斷努力提高空穴遷移率,使其更接近電子遷移率。該領(lǐng)域的關(guān)鍵進展是在S / D外延生長步驟中添加了Ge,并最終在pFET通道中添加了Ge –即Si(x)Ge(1-x)晶體結(jié)構(gòu),提供了壓縮應(yīng)變和大大提高了空穴遷移率。(經(jīng)驗豐富的電路設(shè)計經(jīng)驗豐富的人會記得pFET器件寬度是nFET器件寬度的2.5倍至3倍的3年代,以補償空穴與電子遷移率的差異。隨著在SiGe pFET制備過程中引入的應(yīng)變,這種差異已大大減小。)

向厚度非常小的納米片通道的過渡加劇了提供改進的pFET器件特性的難度。

在最近的IEDM會議上,英特爾詳細介紹了其納米片工程技術(shù)如何應(yīng)對這一挑戰(zhàn)的論文。

pFET納米片制造

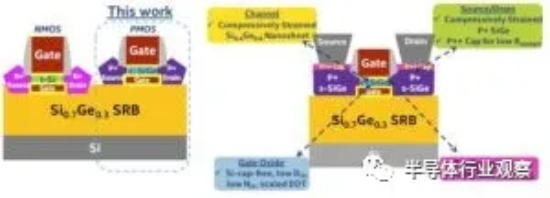

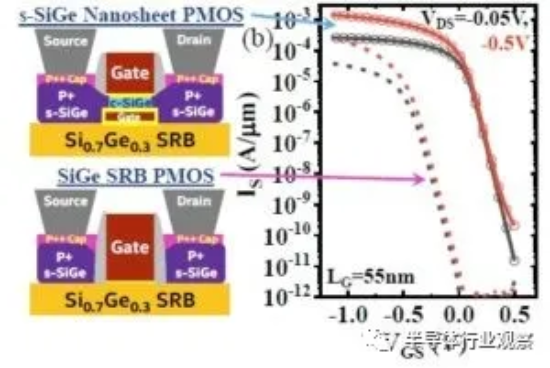

下圖描繪了nFET和pFET納米片的概述。

如上所述,溝道中的壓縮應(yīng)變是高性能設(shè)備的關(guān)鍵。這可以通過以下方式實現(xiàn):

pFET溝道的外延納米片是Si(0.4)Ge(0.6)

提高的S / D外延生長量也是SiGe

納米片正下方的襯底由Si和Si(0.7)Ge(0.3)的“應(yīng)變消除緩沖”(strain relief buffer:SRB)層組成

該緩沖層提供了從塊狀硅襯底的中間晶體轉(zhuǎn)變,并提供了一定程度的附加溝道應(yīng)變。

值得一提的是,Si和Ge的晶格常數(shù)僅相差4.2%,即Si = 0.543nm,Ge = 0.566nm。結(jié)果,Ge / Si比是完全可混溶的。

上圖還說明了其他過程工程約束:

為了降低接觸電阻,需要在S / D區(qū)域上添加高度摻雜的頂層

柵極氧化物需要低的缺陷和陷阱密度(具有非常高的高K材料厚度-例如,通道和隨后的HfO2層的介電層)

從納米片厚度(?5nm)到大的p + S / D節(jié)點的過渡需要詳細的工藝設(shè)計,以使柵極與S / D隔離,并將壓縮應(yīng)變從摻雜的SiGe外延引入pMOS溝道。(有關(guān)此步驟的更多信息,請稍后。)

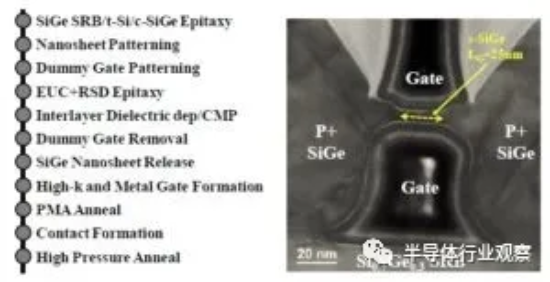

下圖總結(jié)了整個英特爾pMOS納米片制造步驟,并提供了單個納米片器件的TEM截面-NS厚度= 5nm,Lgate = 25nm,寬度= 100nm,EOT氧化物= 9.1埃。

納米片的制造需要幾個獨特的步驟,將保形材料沉積與各向同性和各向異性(定向)蝕刻技術(shù)相結(jié)合。另外,各向同性蝕刻技術(shù)需要對不同的材料組成具有很高的選擇性。

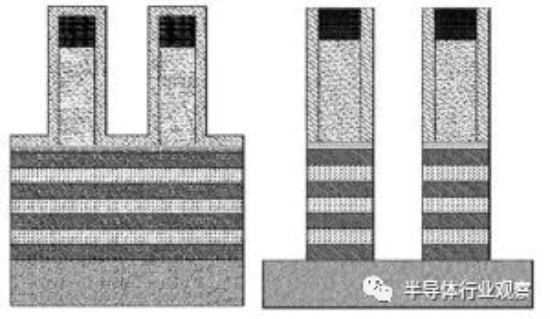

以下來自參考文獻的圖說明了多層堆疊納米片的一般情況的總體流程。而英特爾IEDM討論集中于單個pMOS納米片器件的材料和壓縮溝道應(yīng)變。

起始材料是未摻雜的Si / SiGe外延層的交替層。對“虛擬”頂層?xùn)艠O進行構(gòu)圖,然后共形沉積氧化物并(高度)各向異性蝕刻氧化物和Si / SiGe層,以形成初始納米片堆疊。下一步很關(guān)鍵,如下所示。

選擇性地蝕刻暴露的柵極區(qū)域的側(cè)壁,以提供用于共形氧化物沉積的凹陷體積。對該氧化物的各向異性蝕刻導(dǎo)致堆疊,其中柵極區(qū)域具有橫向間隔氧化物,而溝道的側(cè)壁保持暴露,并用作源/漏外延生長的種子。

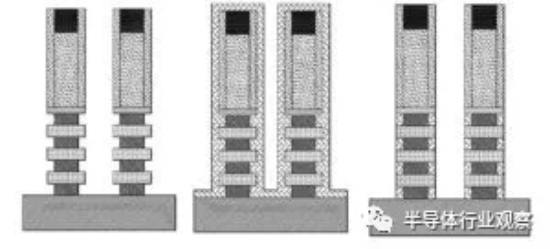

Si中的納米片nMOS器件需要對相鄰的SiGe層進行高度選擇性蝕刻的處理,從而暴露出用于S / D外延生長的Si側(cè)壁。納米片pMOS器件需要高的硅蝕刻速率,從而暴露出用于S / D外延生長的SiGe側(cè)壁。廣泛的工藝研發(fā)(和材料化學(xué))已應(yīng)用于優(yōu)化Si / SiGe“蝕刻速率比”。

在S / D外延生長之后,將虛設(shè)柵極和外延?xùn)艠O層蝕刻掉(再次非常有選擇地蝕刻到現(xiàn)在發(fā)布的納米片溝道“ribbons”上)。在預(yù)清潔之后,將高K柵極氧化物材料沉積在ribbon上,然后沉積(功函數(shù)和低電阻)金屬柵極堆疊,這兩個步驟均使用原子層沉積(ALD)。向下接觸底部的“溝槽”,將其打開并填充金屬,以完成納米片的制造。(在該流程中,為了蝕刻前的表面平面度,也有化學(xué)機械拋光(CMP)步驟。)

附帶一提的是,還應(yīng)該指出,已經(jīng)進行了廣泛的工藝研發(fā),以選擇特定的晶體取向,以優(yōu)化應(yīng)變增強的載流子遷移率,蝕刻速率選擇性和S / D外延生長。

納米片和寄生晶體管

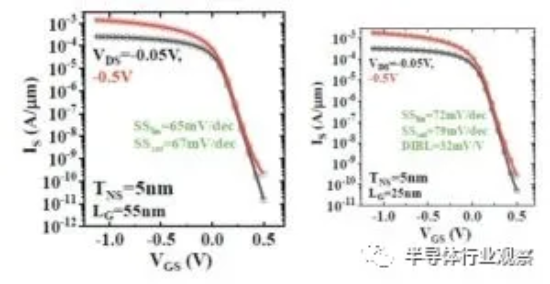

回到其優(yōu)化的壓應(yīng)變pMOS納米片的英特爾演示文稿中,不同設(shè)備的IDS-VGS曲線如下所示(Lgate = 55nm和25nm)。

從全方位柵極配置的優(yōu)異靜電中可以預(yù)期到,為這些器件測量的亞閾值斜率非常出色。(英特爾沒有描述其建立pFET器件閾值電壓的工程方法。)

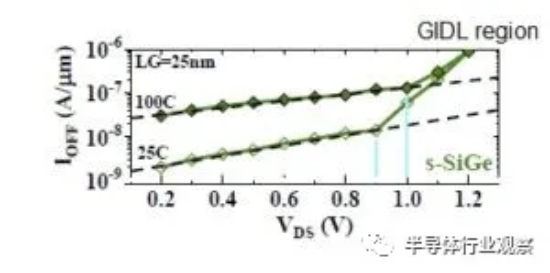

特別令人感興趣的是S / D到基板接口的設(shè)計。納米片結(jié)構(gòu)導(dǎo)致圍繞底部納米片的金屬柵極與襯底之間的寄生晶體管。與納米片的S / D接觸還用作底部寄生晶體管的S / D連接。為了評估這種寄生器件電流的大小,英特爾制造并測量了僅由該寄生晶體管組成的測試工具-實驗結(jié)果如下所示。

該設(shè)備的泄漏電流遠小于納米片的泄漏電流,表明該“sneak” 電流得到了適當(dāng)?shù)囊种啤#檫M一步減小這種寄生電流,可以在S / D觸點下方引入穿通停止摻雜劑區(qū)域。)

VDD優(yōu)化

對于高性能應(yīng)用,設(shè)計人員正在尋求將電源電壓提高到技術(shù)最高水平。這些限制是由于較高電壓下Ioff泄漏的增加所致。溝道中較高的漏極至源極電場會導(dǎo)致漏極引起的勢壘降低(drain-induced barrier lowering:DIBL)電流,而非常高的漏極至柵極場會導(dǎo)致柵極引起的漏極泄漏隧道電流(gate-induced-drain-leakage tunnel current:GIDL)。下圖表明,在GIDL電流呈指數(shù)增長之前(應(yīng)變SiGe,Lgate = 25nm,t_NS = 5nm),VDD = 0.9V對于該技術(shù)是可行的。