臺積電目前被廣泛視為半導(dǎo)體技術(shù)的領(lǐng)導(dǎo)者。但是,這并不是通過做任何值得注意的事情來實(shí)現(xiàn)的:臺積電是從英特爾繼承了這一位置,因?yàn)楹笳呋宋迥陼r(shí)間才推出了其首款10nm產(chǎn)品,而摩爾定律則要求兩年的節(jié)奏。臺積電什么也沒做,只是繼續(xù)遵守上述節(jié)奏。

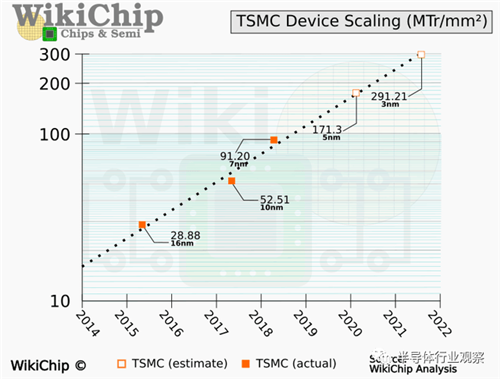

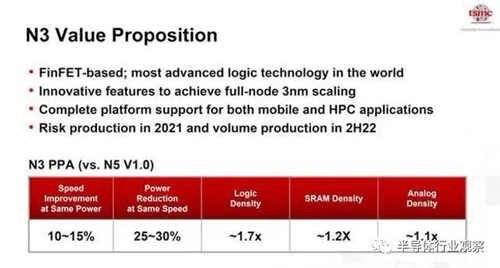

確實(shí),在今年年初的一篇文章中,我已經(jīng)注意到臺積電本身并沒有特別快地發(fā)展,也落后于摩爾定律曲線:臺積電正從5nm過渡(N5 )到3nm(N3)的周期比通常的2.5年更長,而密度的增加也遠(yuǎn)少于摩爾定律所要求的2.0倍:例如,SRAM密度僅提高了1.2倍。為此,我認(rèn)為,這將給英特爾一個(gè)追趕的機(jī)會,但是英特爾隨后推遲了其7納米制程。

最近,有關(guān)2nm的第一份報(bào)告已經(jīng)到來。正如預(yù)期的那樣,這將標(biāo)志著臺積電從FinFET晶體管過渡到全柵晶體管或GAAFET,F(xiàn)inFET晶體管由英特爾于2012年首次引入,然后于2015年由臺積電采用。值得注意的是,臺積電計(jì)劃將回歸兩年更新制程的節(jié)奏,這意味著在使用FinFET十年后,2nm將于2025年初進(jìn)入市場。

問題在于,臺積電剩下的兩個(gè)領(lǐng)先的競爭對手三星和英特爾都計(jì)劃在臺積電之前遷移到GAAFET。這意味著臺積電到2024年可能會從第一跌到第三。

對于投資者來說,這意味著他們不應(yīng)該認(rèn)為臺積電是追求摩爾定律的最后一家晶圓代工廠,因?yàn)楦偁帉⒓觿 ?/p>

一些術(shù)語科普

我將GAAFET(全能柵極)用作其柵極圍繞通道的所有四個(gè)側(cè)面的晶體管的總稱。FinFET圍繞三個(gè)側(cè)面,而平面僅一個(gè)側(cè)面。

三星通常使用術(shù)語MCBFET(多通道橋)或納米片。

三星將其與納米線區(qū)分開來,顧名思義,納米線在幾何形狀上更像是線而不是紙。

nanoribbon則主要由Intel使用,從英特爾研究的圖片來看,這似乎與納米片相似,但可能介于兩者之間。

最后,節(jié)點(diǎn)名稱:TSMC使用Nx,而Samsung和Intel繼續(xù)使用xnm。

臺積電:N5,N3,N2

眾所周知,臺積電已于2020年下半年遷移到N5,與N7相比,遷移速度為兩年。但是,初步發(fā)現(xiàn)表明,雖然節(jié)奏與摩爾定律相當(dāng),但微縮率卻沒有。特別是,Apple A14僅實(shí)現(xiàn)了134MT的密度(每平方毫米1.33億個(gè)晶體管)。與A13的90MT相比,這僅增長了49%。

相比之下,臺積電聲稱N5的微縮率是1.8倍,這將帶來標(biāo)準(zhǔn)密度170MT。但蘋果實(shí)現(xiàn)的這種較低的收縮在很大程度上可以歸因于SRAM(內(nèi)存)的微縮率低得多——僅為1.3倍。

如導(dǎo)言所述,作為臺積電的最后一個(gè)FinFET節(jié)點(diǎn),臺積電的N3將于2023年上半年遵循2.5年的節(jié)奏推出。雖然臺積電本身稱其為全節(jié)點(diǎn)微縮,但沒有任何合理的分析可以真正描述它。邏輯密度縮放比例進(jìn)一步降低至1.7倍,而SRAM僅提高1.2倍。模擬方面則幾乎不會改變。

英特爾十年前的分析表明,SRAM和模擬芯片占Apple芯片的40%至50%,因此盡管有2.5年的節(jié)奏,但現(xiàn)實(shí)世界中的密度預(yù)計(jì)不會超過50%。

最新的信息涉及N2。據(jù)了解,該節(jié)點(diǎn)將移至GAAFET或MBCFET。臺積電計(jì)劃在2023年下半年開始風(fēng)險(xiǎn)生產(chǎn)。與N3相比,這意味著兩年的節(jié)奏。

鑒于這種風(fēng)險(xiǎn),生產(chǎn)滯后了大約12個(gè)月,并且考慮到批量生產(chǎn)落后于產(chǎn)品推出時(shí)間6個(gè)月(例如,N5風(fēng)險(xiǎn)生產(chǎn)于19年上半年開始,隨后iPhone 12于18個(gè)月后推出),這意味著臺積電的N2 GAA工藝將在2025年上半年進(jìn)入市場。

英特爾:7納米,5納米

英特爾在2020年下半年推出了10nm技術(shù),最近又推出了10nm SuperFin技術(shù),英特爾聲稱,該技術(shù)在功耗和性能方面提供了與全節(jié)點(diǎn)躍遷相同的優(yōu)勢。(顯然密度不高。)

英特爾在2020年7月宣布將其7nm的升級時(shí)間推遲6到12個(gè)月,這意味著批量供貨時(shí)間將從2022年轉(zhuǎn)移到2023年。雖然尚不知道7nm的規(guī)格,但英特爾之前曾表示它將是2.0倍或2.4倍收縮:在200-240MT時(shí),它可能比TMSC N5密度高一點(diǎn)。它將仍然是FinFET晶體管。

然而,6月,英特爾首席技術(shù)官確認(rèn)英特爾將“在未來五年內(nèi)”過渡到GAAFET。可以滿足這一承諾的唯一工藝節(jié)點(diǎn)是5nm。從表面上看,這意味著最壞的情況是,英特爾將在2025年推出GAAFET和5nm,與TSMC持平。英特爾也曾表示,5nm將縮小2倍。

問:您能否給我們提供將納米帶/納米線工藝技術(shù)引入大批量生產(chǎn)的時(shí)間表?

答:這不是路線圖討論,所以我會在未來五年內(nèi)含糊其詞。

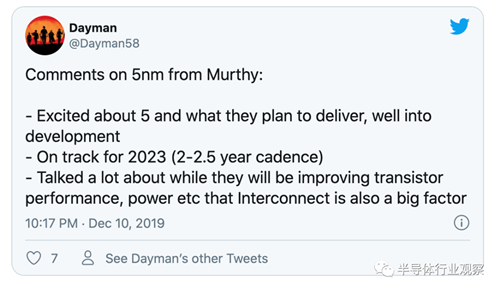

但是,英特爾的路線圖比2025年更具侵略性。英特爾于2019年(在7nm延遲之前)宣布,它打算恢復(fù)到2年的節(jié)奏。直到2029年的路線圖也證實(shí)了這一點(diǎn)。考慮到7nm應(yīng)該在2021年第4季度進(jìn)入市場,這意味著5nm也將在2023年第4季度推出,Murthy確認(rèn):

假設(shè)5nm現(xiàn)在也要推遲6到12個(gè)月(即使從原理上講7nm的延遲不會對5nm的發(fā)展產(chǎn)生任何影響),這仍然意味著5nm將在2024年推出,比臺積電提前一年。

有人可能會說英特爾可能無法實(shí)現(xiàn)其路線圖,但是除非另外證明,否則本文將平等對待每個(gè)供應(yīng)商的路線圖。

英特爾與臺積電

英特爾的10納米制程的標(biāo)準(zhǔn)密度為100MT。雖然顯然無法確定A14在Intel的10nm工藝上將有多大(及其實(shí)際密度),但在過去,Apple的SoC通常都很好地遵循了這一標(biāo)準(zhǔn)化的密度指標(biāo),這使A14的看似低了134MT。為此A14特別值得注意。

因此,假設(shè)A14在Intel的10nm工藝上將達(dá)到100MT,這表明在實(shí)際密度下,TSMC可能僅比Intel高1.35倍。與全節(jié)點(diǎn)的飛躍相比,這更類似于半節(jié)點(diǎn)的優(yōu)勢。

換句話說,英特爾可能并沒有很多人想象的那樣落后。反過來說,臺積電也可能不如設(shè)想的那樣領(lǐng)先。確實(shí),英特爾可能缺乏密度,但它可能會在晶體管(和封裝)技術(shù)的其他領(lǐng)域中得到彌補(bǔ),英特爾在其SuperFin技術(shù)(以及Lakefield 3D堆棧)中強(qiáng)調(diào)了這一點(diǎn)。

同樣,如果N3僅將密度提高50%,則只能實(shí)現(xiàn)比理論上的300MT更接近200MT的水平,后者又可能比5nm接近英特爾的7nm。

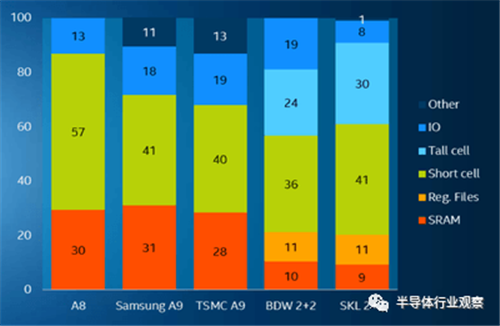

為了證實(shí)這一說法,英特爾和臺積電都需要更多有關(guān)多個(gè)芯片的芯片尺寸和晶體管數(shù)的數(shù)據(jù),但英特爾在2014年左右停止發(fā)布晶體管數(shù):英特爾認(rèn)為,由于其芯片在邏輯單元方面有很大不同,I / O和SRAM(請參見上圖),與Apple晶體管數(shù)量的任何比較都具有誤導(dǎo)性。換句話說,所有英特爾CPU的全芯片密度均明顯低于標(biāo)準(zhǔn)密度。

三星方面的表現(xiàn)

三星目前正在加快其5納米制程。與各種報(bào)道相反,三星今年已做出一些努力向媒體和投資者保證,其5nm工藝沒有任何產(chǎn)量問題。

三星的5nm并不是一個(gè)新節(jié)點(diǎn),而是基于其7nm平臺直接衍生的產(chǎn)品。這樣,它的密度改進(jìn)將是不及臺積電的N5,也不應(yīng)高于英特爾的10nm。

但三星的3nm節(jié)點(diǎn)將標(biāo)志著其下一步的發(fā)展,正如三星很久以前宣布的那樣,這將標(biāo)志著其業(yè)界領(lǐng)先的MCBFET的推出。該節(jié)點(diǎn)似乎有所延遲,因?yàn)樗F(xiàn)在的目標(biāo)是2022年的量產(chǎn)(之前是2021年末)。三星進(jìn)一步聲稱,在新工藝上,晶體管密度縮小了0.65倍或0.55倍,這應(yīng)該使其接近TSMC 5nm而不是3nm的密度。

不過,正如所討論的那樣,臺積電的N3將更像是半節(jié)點(diǎn)收縮,因此三星可能密度稍差,它可能會在技術(shù)和上市時(shí)間上有所彌補(bǔ),這與英特爾不同。

在這方面,三星早期推出的GAAFET與22nm的Intel FinFET類似,后者的密度可與臺積電的平面28nm相提并論。雖然三星將不會擁有密度優(yōu)勢,但在市場上推出這項(xiàng)技術(shù)的領(lǐng)先地位仍然領(lǐng)先于TSMC三年,領(lǐng)先于Intel兩年。無論如何,三星已經(jīng)在2019年宣布它將計(jì)劃在這十年內(nèi)投資超過1000億美元以趕上臺積電。

總結(jié)

目前被視為市場領(lǐng)導(dǎo)者的臺積電可能會在2024年或更早之前失去其工藝技術(shù)的領(lǐng)導(dǎo)地位。

英特爾在2012年推出了FinFET晶體管,該晶體管在同行業(yè)中比其他行業(yè)領(lǐng)先了幾年(這是事物可以相對快速地發(fā)生變化的一個(gè)例子),但現(xiàn)在,這種晶體管已經(jīng)耗盡。因此,必須用GAAFET代替它。盡管這種轉(zhuǎn)變不會像FinFET最初的轉(zhuǎn)變那樣劇烈,但它是一個(gè)重大的轉(zhuǎn)變。就像FinFET一樣,它將標(biāo)志著制程技術(shù)和芯片設(shè)計(jì)新時(shí)代的開始。

這意味著可能在FinFET期間跌落的供應(yīng)商可能有機(jī)會追趕。確實(shí),目前的數(shù)據(jù)表明,臺積電將是最后一次實(shí)現(xiàn)這一轉(zhuǎn)變的廠商,比英特爾落后了一年,三星落后了三年。

考慮到SRAM密度縮放的放慢和3D邏輯堆棧的引入以及其他一些未知因素,GAAFET的引入可能被視為工藝技術(shù)領(lǐng)先地位的(更可靠)指示,我之前已經(jīng)指出過不僅僅是晶體管密度:Intel與臺積電相比:工藝技術(shù)的領(lǐng)導(dǎo)地位遠(yuǎn)勝于晶體管密度。

過去,三星曾為Apple,Nvidia(NVDA)和Qualcomm(QCOM)等公司代工芯片。因此,三星差異化的GAAFET路線圖很有可能會對晶圓代工市場產(chǎn)生實(shí)際影響,而英特爾繼續(xù)從其10nm和7nm延遲中恢復(fù)過來,以尋求重新奪回工藝領(lǐng)先地位。