光刻技術(shù)是使微電子和納米電子器件在過去半個(gè)世紀(jì)中不斷微縮的基礎(chǔ)技術(shù)之一。該過程使用光將圖案從光掩模轉(zhuǎn)移到基板上,然后進(jìn)行一系列化學(xué)處理,將曝光的圖案蝕刻到基板上,或以所需的圖案沉積新材料。

隨著進(jìn)一步的微縮,這種傳統(tǒng)的自上而下的圖案轉(zhuǎn)印過程變得越來越復(fù)雜和昂貴。器件的進(jìn)一步小型化要求對(duì)關(guān)鍵尺寸低于20nm的特征進(jìn)行patterning。除了縮放分辨率外,精確的圖案放置也變得非常具有挑戰(zhàn)性。隨著高縱橫比和復(fù)雜形狀的3D結(jié)構(gòu)的出現(xiàn),有效占用空間的減少也隨之而來。

大約五年前,該行業(yè)開始對(duì)諸如區(qū)域選擇性沉積(area-selective deposition:ASD)和定向自組裝(directed self-assembly:DSA)之類的其他圖案化方法感興趣。這些自下而上的技術(shù)有其自身的優(yōu)點(diǎn)和挑戰(zhàn),但是它們有一個(gè)共同點(diǎn):它們可以提供新穎的解決方案,因此具有巨大的潛力來補(bǔ)充傳統(tǒng)圖案,以用于未來納米電子器件的工業(yè)制造。

DSA:縮小密集的規(guī)則圖案

從歷史上看,通過在光刻系統(tǒng)中應(yīng)用較短波長的光源,可以對(duì)越來越小的和更密集的特征進(jìn)行圖案化。過去這些年,波長已從436nm,405nm,365nm,248nm和193nm減小到最終的13.5nm,也就是我們熟知的極紫外(EUV)光刻。對(duì)于給定的波長,已經(jīng)引入了多種圖案技術(shù)的變化,以進(jìn)一步推動(dòng)分辨率極限。如今,工業(yè)界正在使用例如光刻,平版印刷工藝(涉及兩個(gè)曝光步驟)或自對(duì)準(zhǔn)雙(甚至四)圖案化。后一種技術(shù)依賴于一個(gè)光刻步驟(以創(chuàng)建預(yù)圖案)以及附加的沉積和蝕刻步驟(以實(shí)現(xiàn)原始預(yù)圖案的復(fù)制)。已知這些多圖案化過程非常復(fù)雜且昂貴。

幾年前,DSA已被提出作為一種有前途的互補(bǔ)圖案選擇。DSA基于稱為BCP(block-copolymers )一類分子的自組裝特性。在適當(dāng)?shù)那闆r下,這些材料在涂覆到晶圓上時(shí)會(huì)發(fā)生微相分離(microphase separatio)。這就可以獲取具有5-30nm特征的規(guī)則納米尺寸圖案。可以通過調(diào)節(jié)聚合物的組成及其尺寸來設(shè)計(jì)圖案。通過使用線/間隔或孔的預(yù)圖案,可以進(jìn)一步指導(dǎo)(指導(dǎo))該裝配體,這是半導(dǎo)體行業(yè)感興趣的兩種結(jié)構(gòu)。這樣,最終圖案化的pitch將比template的小得多。由此可見,DSA是一種非常規(guī)的自底向上技術(shù),可以增強(qiáng)圖案的密度和分辨率。

主要優(yōu)點(diǎn)和挑戰(zhàn):

IMEC已經(jīng)確定了其多項(xiàng)優(yōu)點(diǎn),以評(píng)估DSA流程與大批量生產(chǎn)的相關(guān)性。Imec認(rèn)為與傳統(tǒng)的多圖案技術(shù)相比,成本(COO)是DSA的主要優(yōu)勢(shì)。較低的COO可以主要?dú)w因于減少的工藝步驟,并結(jié)合使用傳統(tǒng)的光刻技術(shù)來創(chuàng)建更寬松的預(yù)圖案。英特爾在2019年IEDM會(huì)議上提出的第二個(gè)優(yōu)勢(shì)是輕松控制邊緣放置錯(cuò)誤的能力,這是傳統(tǒng)圖案化方法遇到的主要挑戰(zhàn)之一。使用DSA,可以以非常均勻的方式在整個(gè)圖案化區(qū)域上獲得緊密的pitch。

但是,DSA雖然比傳統(tǒng)的(EUV)光刻簡單,但DSA的設(shè)計(jì)靈活性卻較低。DSA可以輕松打印常規(guī)圖案,但是很難打印非常規(guī)圖案(例如,pitch可變的圖案)。因此,將來的設(shè)計(jì)在采用DSA作為構(gòu)圖技術(shù)時(shí)將不得不接受這一限制。“了解DSA設(shè)計(jì)”將是今后幾年要解決的重要挑戰(zhàn)。

缺陷率:不再是最賣座的產(chǎn)品:

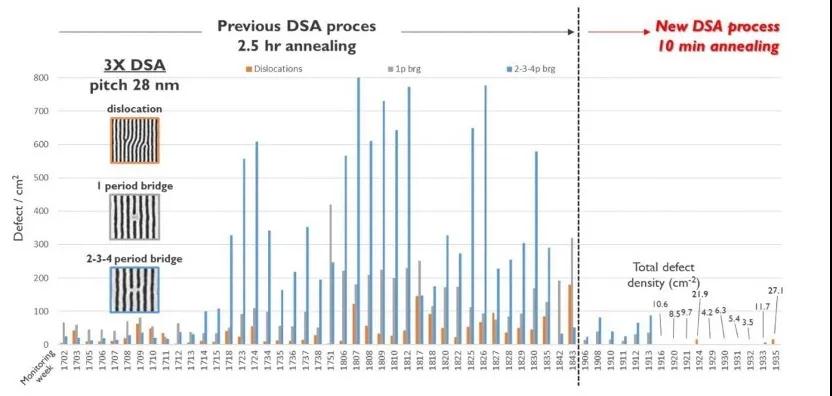

最初,半導(dǎo)體行業(yè)對(duì)DSA并不那么樂觀,因?yàn)榭刂迫毕萋首兊梅浅@щy。為了與工業(yè)制造相關(guān),總?cè)毕菝芏葢?yīng)在1cm -2以下,這在當(dāng)時(shí)很難實(shí)現(xiàn)。在自組裝過程中形成的位錯(cuò)和橋接是造成總?cè)毕莸闹饕颉?/p>

但是,今天,imec很有信心充分控制缺陷率。近年來,imec深入研究了annihilation ,并獲得了有關(guān)如何控制位錯(cuò)和橋接的基本見識(shí)。最終,該團(tuán)隊(duì)能夠?qū)⑼嘶饡r(shí)間從最初的2.5小時(shí)減少到只有10分鐘,從而獲得具有穩(wěn)定且足夠低的缺陷數(shù)的有序狀態(tài)。如果我們使用傳統(tǒng)的電子顯微鏡,則需要一年多的時(shí)間才能發(fā)現(xiàn)缺陷。有了這些見解,imec現(xiàn)在可以為行業(yè)提供一本手冊(cè),其中包含一些主要 knobs ,借助這些 knobs 可以控制DSA流程的缺陷(圖1)。

圖1. 2017年至2019年的DSA缺陷監(jiān)視結(jié)果。

通過提高吞吐量可以實(shí)現(xiàn)更低,更穩(wěn)定的缺陷率。

邁向第二代BCP:

這種穩(wěn)定且低缺陷的DSA工藝是通過使用3倍圖案密度乘法實(shí)現(xiàn)的。可以使用BCP的DSA在84nm間距的預(yù)圖案上成功地圖案化28nm的最終圖案間距,該預(yù)圖案是通過193nm浸沒光刻技術(shù)獲得的。通過使用PS-b-PMMA (polystyrene-block-poly methyl methacrylate) 作為BCP,可以實(shí)現(xiàn)3x圖案致密化。

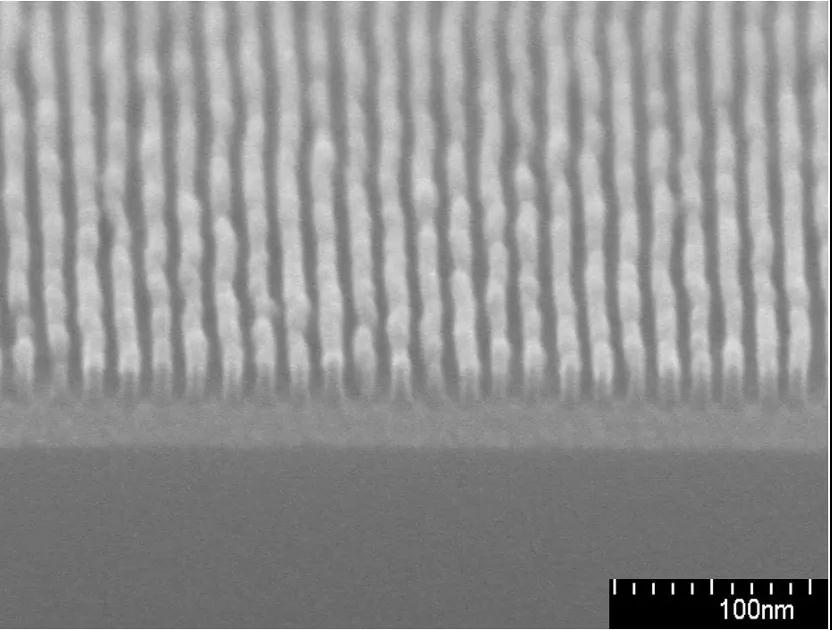

隨著imec朝20nm以下的間距發(fā)展,BCP鏈的長度也應(yīng)減少,以實(shí)現(xiàn)更小的間距。然而,小于間距21nm的PS- b - PMMA聚合物將不再形成透明結(jié)構(gòu),從而使BCP處于混合無序狀態(tài)。為了解決這個(gè)問題,imec現(xiàn)在正在與材料供應(yīng)商和大學(xué)密切合作,轉(zhuǎn)向第二代BCP,即高X BCP。迄今為止,使用PS- b -PMMA獲得的知識(shí)已轉(zhuǎn)移到新一代BCP中,從而導(dǎo)致了良好的自組裝過程(圖2)。

圖2.高χDSA生成的16nm全pitch L / S模式。

(圖片來源:Jan Doise /明尼蘇達(dá)大學(xué)/德克薩斯大學(xué)奧斯汀分校)。

目前,尚在調(diào)查一些剩余的問題。首先,在這種微小的情況下,將圖案轉(zhuǎn)移到底層材料中比想象中更具挑戰(zhàn)性。其次,需要開發(fā)新的計(jì)量技術(shù),以能夠評(píng)估現(xiàn)在尺寸非常小的自組裝結(jié)構(gòu)的缺陷性。

大約10年前,imec開始探索使用DSA作為替代圖案方法的想法。當(dāng)時(shí),DSA主要是一個(gè)學(xué)術(shù)研究領(lǐng)域。基于近年來取得的進(jìn)展,DSA現(xiàn)在在工業(yè)領(lǐng)域引起 了巨大興趣。這種發(fā)展伴隨著大學(xué),材料和設(shè)備供應(yīng)商以及計(jì)量學(xué)家的巨大承諾,即認(rèn)真控制和檢查材料和過程。這個(gè)生態(tài)系統(tǒng)是成功的關(guān)鍵,對(duì)于下一代DSA流程的開發(fā)也是如此。

ASD:僅在需要時(shí)存放材料

對(duì)于區(qū)域選擇性沉積,將根據(jù)預(yù)定義的圖案沉積材料,而不會(huì)在其余表面上發(fā)生沉積。該選擇性沉積可以通過依賴于選擇性表面反應(yīng)的沉積技術(shù)來實(shí)現(xiàn),例如原子層沉積(ALD)和化學(xué)氣相沉積(CVD)。

幾年前,這種自下而上的技術(shù)也引起了半導(dǎo)體行業(yè)的興趣,因?yàn)樗菍?duì)傳統(tǒng)的自上而下的pattering進(jìn)行補(bǔ)充的方法。就像DSA一樣,ASD也有自己的優(yōu)點(diǎn)。與傳統(tǒng)光刻相比,它可以實(shí)現(xiàn)更廣泛的應(yīng)用,例如在復(fù)雜的3D結(jié)構(gòu)中構(gòu)圖特征。ASD的另一個(gè)巨大機(jī)會(huì)是,它原則上只能在需要的地方放置結(jié)構(gòu),并且在水平和垂直方向上都具有原子精度。這樣,對(duì)于某些應(yīng)用,它可能會(huì)成為一種更具可持續(xù)性和成本效益的方法,與自上而下的圖案相比,所需的化學(xué)產(chǎn)品和能源更少。

到目前為止,ASD的工業(yè)用途僅限于半導(dǎo)體的選擇性外延生長和互連結(jié)構(gòu)中納米級(jí)金屬薄層的生長,這主要是因?yàn)閮H對(duì)有限數(shù)量的工藝和材料進(jìn)行了研究。為了擴(kuò)大該技術(shù)的適用性,必須對(duì)表面化學(xué),ALD和CVD工藝的表面依賴性以及前體在這些工藝中的作用有基本的了解。

另外,必須具有控制或減輕非生長區(qū)域缺陷的能力。自2016年以來,每年在ASD研討會(huì)上都會(huì)討論該領(lǐng)域的全球進(jìn)展。在本次研討會(huì)上越來越多的科學(xué)貢獻(xiàn)反映出學(xué)術(shù)界和工業(yè)界對(duì)這一引人入勝的研究領(lǐng)域的興趣日益濃厚。

對(duì)表面化學(xué)和改性的深入了解:Imec成功地探索了幾種材料系統(tǒng),這些系統(tǒng)有望選擇性沉積諸如TiN或Ru之類的材料,這些材料與芯片制造高度相關(guān)。據(jù)證實(shí),例如,OH–等的SiO2 終止電介質(zhì)可以用作用于生長的Ru的生長表面起作用。

圖3. 7.5nm厚的TiN,用ALD選擇性沉積在Si3N4(空間)上。

aC(線)充當(dāng)非增長區(qū)域。

廣泛的潛在應(yīng)用:

對(duì)ASD期間的表面化學(xué)和生長機(jī)理的更深入了解將指導(dǎo)新穎的ASD工藝的設(shè)計(jì),從而實(shí)現(xiàn)更廣泛的應(yīng)用。潛在的應(yīng)用包括例如創(chuàng)建完全自對(duì)準(zhǔn)的通孔。通孔是金屬結(jié)構(gòu),可將芯片后端的不同金屬層電互連。傳統(tǒng)上,通孔的形成始于對(duì)通孔開口進(jìn)行圖案化并將其蝕刻到下層中。然后在通孔中填充金屬(例如釕(Ru))并進(jìn)行過度填充,這意味著金屬沉積持續(xù)到在底層上形成完整的金屬層為止。蝕刻步驟和化學(xué)機(jī)械拋光步驟完成了通孔的形成(圖4)。通過這種方式,如果通孔過大或未對(duì)準(zhǔn),則存在短路或可靠性問題的風(fēng)險(xiǎn)。相反,利用電介質(zhì)上的電介質(zhì)ASD,由于創(chuàng)建了形貌,因此可以放寬通孔的對(duì)準(zhǔn)和過大規(guī)格。

圖4. 8nm厚的電介質(zhì),通過ALD有選擇地沉積在低k上。

被甲基封端的有機(jī)膜功能化的銅線充當(dāng)非生長區(qū)域。

其他潛在的應(yīng)用是色調(diào)反轉(zhuǎn)(tone inversion)過程,通常可以獲得逆的材料圖案。這樣,它們可用于將孔變成柱子,或?qū)⒖臻g變成線。ASD是用于此類應(yīng)用程序的有前途的技術(shù)。使用預(yù)構(gòu)圖的犧牲層作為模板,通過使用區(qū)域選擇性沉積,通過自下而上的填充獲得反面的材料圖案。當(dāng)難以對(duì)材料進(jìn)行傳統(tǒng)的光刻構(gòu)圖時(shí),例如對(duì)于TiN或Ru之類的硬掩模材料,使用ASD進(jìn)行色調(diào)反轉(zhuǎn)可以提供解決方案。此外,由于不需要過量填充和CMP步驟,因此該解決方案比傳統(tǒng)方法需要更少的處理步驟。用于音調(diào)反轉(zhuǎn)的ASD也可以擴(kuò)展到較小的特征尺寸。

對(duì)于極端狹窄的溝槽或孔(例如,互連過孔),甚至高縱橫比的結(jié)構(gòu)(例如,Supervia),或垂直放置在復(fù)雜的3D結(jié)構(gòu)(例如,垂直孔)中,ASD也是一種候選方法。互補(bǔ)場(chǎng)效應(yīng)晶體管(或CFET)。潛在的應(yīng)用不限于此處列出的那些。

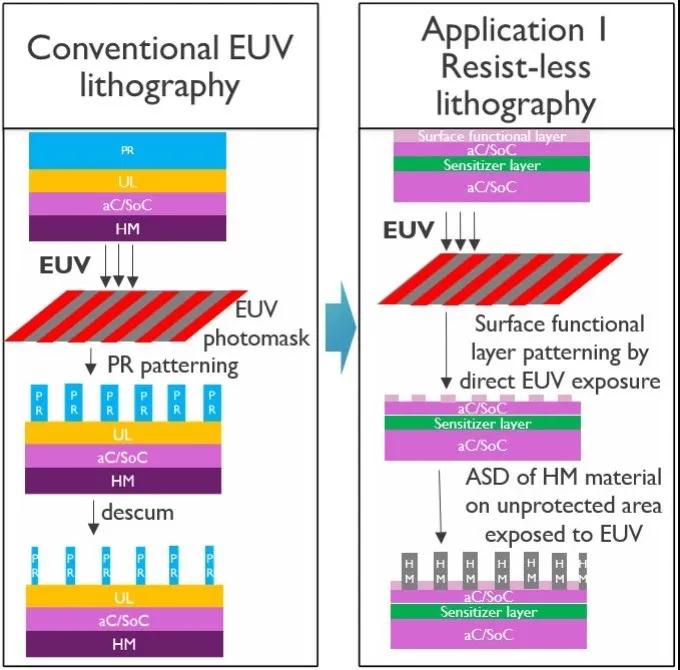

一種破壞性方法,無抗蝕劑光刻:

更具有破壞性的是,imec正在探索ASD作為替代無抗蝕劑光刻方法的潛力,以支持高NA(0.55數(shù)值孔徑(NA))EUV光刻工藝。高NA光刻有望成為下一代EUV光刻工藝,有望推動(dòng)半導(dǎo)體規(guī)模向3nm以下技術(shù)節(jié)點(diǎn)發(fā)展。具有高數(shù)值孔徑光學(xué)器件的EUV光刻通常需要非常薄的光刻膠層,很難均勻地實(shí)現(xiàn)。而且,當(dāng)前的光致抗蝕劑材料具有非常復(fù)雜的化學(xué)組成。當(dāng)暴露在EUV光下時(shí),暴露區(qū)域和未暴露區(qū)域之間的側(cè)壁可能會(huì)顯示出較高的粗糙度,從而導(dǎo)致有效特征尺寸發(fā)生波動(dòng)。

在尋找用于高NA EUV光刻的最佳光刻膠材料的同時(shí),imec正在研究在不使用光刻膠材料的情況下創(chuàng)建光刻圖案化掩模的可行性(圖5)。

圖5.無抗蝕劑的EUV光刻(右)與常規(guī)EUV光刻(左)的概念。

就像傳統(tǒng)的EUV光刻一樣,無抗蝕劑光刻也使用EUV光子發(fā)射。但是在這種情況下,僅頂表面需要暴露在光源下,從而可以減少暴露所需的EUV劑量。

如今,支持ASD的EUV光刻的主要目標(biāo)是與相關(guān)材料的區(qū)域選擇性沉積相結(jié)合,以建立對(duì)表面改性機(jī)制的基本理解。此外,這項(xiàng)工作的基本部分是研究EUV光與改性和未改性材料表面的相互作用。這項(xiàng)研究在很大程度上受到建模工作以及Attolab中即將可用的工具的支持。Attolab是imec和KMLabs的一項(xiàng)聯(lián)合計(jì)劃,最近成立的目的是使研究EUV光子吸收及其后續(xù)過程的時(shí)間跨度達(dá)到前所未有的范圍。

總結(jié)

DSA和ASD都被認(rèn)為是有前途的自下而上的構(gòu)圖方法,可以補(bǔ)充傳統(tǒng)的自上而下的構(gòu)圖方案。當(dāng)圖案化密集的規(guī)則結(jié)構(gòu)時(shí),DSA是一項(xiàng)冠軍技術(shù)。與傳統(tǒng)的圖案化相比,該技術(shù)有望降低擁有成本,并降低邊緣放置誤差。Imec控制缺陷的能力是邁向工業(yè)應(yīng)用的重要一步。另一方面,ASD是一種新穎的方法,它允許以很高的精度僅在需要的地方放置結(jié)構(gòu)。只要能夠充分理解表面化學(xué),表面鈍化和沉積機(jī)理,并控制缺陷率,該技術(shù)就有望在芯片制造領(lǐng)域得到廣泛的應(yīng)用-從色調(diào)反轉(zhuǎn)到無抗蝕劑光刻。