文獻(xiàn)標(biāo)識(shí)碼: A

文章編號(hào): 0258-7998(2014)04-0048-04

隨著數(shù)字化變電站的發(fā)展以及分布式網(wǎng)絡(luò)的廣泛應(yīng)用,對(duì)于系統(tǒng)的時(shí)間同步精度和穩(wěn)定性要求越來(lái)越高[1-2]。本文設(shè)計(jì)實(shí)現(xiàn)了時(shí)鐘對(duì)時(shí)同步的系統(tǒng)方案和軟件實(shí)現(xiàn)過程,其基于ADI公司的BF518高性能DSP,包含支持IEEE-1588協(xié)議的模塊以及具有硬件時(shí)間戳功能的TSYNC模塊[3-4]。

基于IEEE-1588協(xié)議的主從時(shí)鐘通過周期性地交互帶有時(shí)間戳的報(bào)文計(jì)算出時(shí)間偏差和頻率偏差,并采用適當(dāng)?shù)姆椒ㄕ{(diào)整時(shí)鐘的時(shí)間和頻率,從而達(dá)到時(shí)鐘同步的目的。其中報(bào)文攜帶的時(shí)間戳的精度是決定時(shí)鐘對(duì)時(shí)精度的一個(gè)重要因素[5]。

1 系統(tǒng)模塊方案

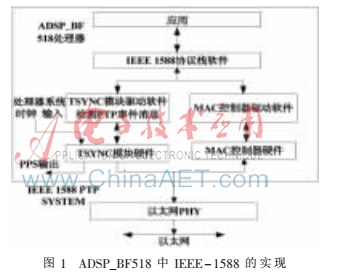

圖1所示是一個(gè)建立在ADSP_BF518處理器中的完整的兼容IEEE-1588 2008版本的系統(tǒng)。處理器的TSYNC模塊探測(cè)傳入和傳出的IEEE-1588消息以及使用硬件標(biāo)記事件消息的時(shí)間戳。IEEE-1588協(xié)議棧完成標(biāo)準(zhǔn)要求的消息交換。TSYNC驅(qū)動(dòng)負(fù)責(zé)讀寫和調(diào)整TSYNC時(shí)鐘,以及使用MAC控制器驅(qū)動(dòng)發(fā)送和接收以太網(wǎng)MAC層(開放式系統(tǒng)互聯(lián)的第二層)消息。同時(shí)也完成控制律和過濾P2P延時(shí)測(cè)量。以太網(wǎng)PHY芯片采用美國(guó)國(guó)家半導(dǎo)體的DP83848,因?yàn)樗哂械偷难訒r(shí)抖動(dòng)特性。采用處理器50 MHz系統(tǒng)時(shí)鐘作為TSYNC模塊的時(shí)鐘源。

2 ADSP_BF518處理器的TSYNC模塊

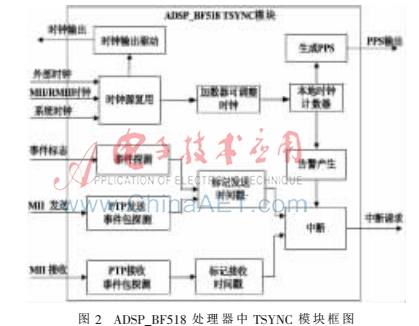

ADSP_BF518擁有一個(gè)內(nèi)置的EMAC模塊,具有支持由額外的TSYNC模塊擴(kuò)展的包含在IEEE-1588標(biāo)準(zhǔn)協(xié)議內(nèi)的EMAC功能的能力;同時(shí)額外的特性是支持以太網(wǎng)中廣泛的IEEE-1588應(yīng)用。圖2所示是TSYNC模塊的框圖。

ADSP_BF518處理器具有如下特性:

(1)包探測(cè):ADSP_BF518處理器能夠探測(cè)和提供硬件時(shí)間戳給所有的IEEE-1588事件消息,包括傳入和傳出包。IEEE-1588系統(tǒng)的精度主要依賴于事件消息的時(shí)間戳精度和時(shí)間戳標(biāo)記的時(shí)機(jī),因?yàn)檫@些影響了路徑延時(shí)對(duì)稱和不變的前提要求。TSYNC模塊一直監(jiān)視MAC控制器與以太網(wǎng)PHY之間的硬件接口(即MII層接口),并為任何時(shí)候探測(cè)到的事件消息生成硬件時(shí)間戳。由于物理層對(duì)報(bào)文傳輸?shù)难訒r(shí)很小且?guī)缀鯚o(wú)延時(shí)波動(dòng),因而可以得到很高的時(shí)間標(biāo)記精度[6]。事件消息的探測(cè)被設(shè)計(jì)為可編程的,基本可配置為支持IEEE-1558 2002版本或IEEE-1588 2008版本。此外,此種可編程特性允許支持IEEE-1588將來(lái)的版本,也可以支持需要時(shí)間戳的通用協(xié)議,包括配置打入時(shí)間戳到進(jìn)入或傳出的每個(gè)以太網(wǎng)包。

(2)靈活的時(shí)鐘源:本地時(shí)鐘的屬性對(duì)于IEEE-1588系統(tǒng)的性能至關(guān)重要。為滿足各種應(yīng)用的需求,ADSP_BF518處理器允許本地時(shí)鐘源有3個(gè)選項(xiàng):系統(tǒng)時(shí)鐘、外部時(shí)鐘、以太網(wǎng)時(shí)鐘。如果應(yīng)用程序有特定的時(shí)鐘要求,可選擇外部時(shí)鐘以提供定制的時(shí)鐘源。以太網(wǎng)時(shí)鐘的選擇可以提供很好的精度,如果主從設(shè)備連接在同一個(gè)回路,因?yàn)閰⒖紩r(shí)鐘來(lái)自以太網(wǎng)線,所以兩個(gè)設(shè)備運(yùn)行相同的時(shí)鐘。通常的應(yīng)用可以選擇系統(tǒng)時(shí)鐘作為時(shí)鐘源。被選的時(shí)鐘源也是由TSYNC模塊驅(qū)動(dòng),并通過特定的ClockOut引腳作為處理器的一個(gè)輸出,被系統(tǒng)的其他部分用來(lái)獲取本地時(shí)間信息。

(3)可調(diào)時(shí)鐘:TSYNC模塊的可調(diào)時(shí)鐘是基于加數(shù)器的時(shí)鐘。如圖3所示,輸入固定的時(shí)鐘信號(hào),輸出一個(gè)脈沖變少了的輸入信號(hào):每一次輸入時(shí)鐘,加數(shù)器的值會(huì)被加到累加器,每次累加器的溢出產(chǎn)生的進(jìn)位會(huì)驅(qū)動(dòng)本地時(shí)間計(jì)數(shù)器,時(shí)間計(jì)數(shù)器是以脈沖的數(shù)目表征本地時(shí)間信息。可以通過改變加數(shù)器的值來(lái)調(diào)整本地時(shí)鐘的頻率,因?yàn)榧訑?shù)器決定累加器溢出的頻率,從而決定本地時(shí)鐘計(jì)數(shù)器增加的頻率,因而可達(dá)到調(diào)整本地時(shí)鐘的目的。如式(1)所示,F(xiàn)in是輸入時(shí)鐘的頻率,A是加數(shù)器的值,F(xiàn)out是本地時(shí)鐘頻率。

3 影響時(shí)鐘同步精度的因素

在IEEE1588精確時(shí)鐘協(xié)議進(jìn)行主從時(shí)鐘同步的過程中,由主時(shí)鐘先發(fā)送同步報(bào)文。從時(shí)鐘收到同步報(bào)文時(shí),根據(jù)同步報(bào)文中的時(shí)間戳和線路延時(shí)計(jì)算出與主時(shí)鐘的偏差,對(duì)本地時(shí)鐘進(jìn)行調(diào)整。

在同步過程中,要滿足一些基本的前提條件。其中包括:同步系統(tǒng)子網(wǎng)內(nèi)的主從時(shí)鐘通信傳輸延時(shí)須對(duì)稱,如不對(duì)稱不可忽略,則必須做出補(bǔ)償;時(shí)鐘內(nèi)的晶體振蕩器應(yīng)具有足夠好的固有穩(wěn)定性。同步計(jì)算方式如下:

式中:D為主從時(shí)鐘線路的平均延時(shí)(D的存在是因?yàn)閺臅r(shí)鐘得到的時(shí)間是主時(shí)鐘發(fā)出包的時(shí)間戳,Tmk-Tsk是主從時(shí)間差),在系統(tǒng)啟動(dòng)時(shí)設(shè)為默認(rèn)值0;Ok為第k次同步時(shí)從時(shí)鐘計(jì)算出的與主時(shí)鐘的偏差;Tmk和Tsk分別為第k次同步時(shí),主時(shí)鐘和從時(shí)鐘在底層記錄的時(shí)間戳;T為本次同步修改系統(tǒng)時(shí)鐘前的PTP系統(tǒng)時(shí)間,T為本次同步后的PTP系統(tǒng)時(shí)間[7]。

主從時(shí)鐘通過交換時(shí)間消息的方式達(dá)到同步,存在如下局限性:

(1)主時(shí)鐘發(fā)送攜帶時(shí)間信息的廣播報(bào)文的時(shí)間間隔不能無(wú)限大。因?yàn)閺臅r(shí)鐘將使用自身精度低的振蕩器打入時(shí)間戳到接收到的廣播報(bào)文,如果報(bào)文的時(shí)間間隔過大,會(huì)導(dǎo)致主從時(shí)鐘隨著時(shí)間的推移偏差逐漸增大。如式(1)主從時(shí)鐘振蕩器的特點(diǎn)不同引起的偏差Ok,如果時(shí)鐘內(nèi)的晶體振蕩器的固有穩(wěn)定性不夠好,那么偏差Ok會(huì)更大,間隔時(shí)間內(nèi)產(chǎn)生的同步誤差就更大。

(2)如式(1)所示,主從時(shí)鐘的線路延時(shí)存在一定的誤差D,增加了額外的偏移值,間隔時(shí)間內(nèi)產(chǎn)生的同步誤差也就相應(yīng)地增加。

(3)如果路徑平均延時(shí)D在主從時(shí)鐘間不對(duì)稱,即無(wú)法通過平均值計(jì)算得到D,那么隨著D的準(zhǔn)確度降低,將進(jìn)一步導(dǎo)致主從時(shí)鐘間的同步精度降低。

4 主從時(shí)鐘延時(shí)計(jì)算和調(diào)整從時(shí)鐘時(shí)間的實(shí)現(xiàn)

如式(2)中Ok=Tmk+D-Tsk所示,Tmk和Tsk分別為第k次同步時(shí),主時(shí)鐘和從時(shí)鐘記錄的時(shí)間戳,為已知的時(shí)間信息。因此只要計(jì)算出平均路徑延時(shí)D,就可以得出Ok,從而最終算出同步后的從時(shí)鐘時(shí)間T。

主從時(shí)鐘的振蕩器越相似,則平均路徑延時(shí)D越準(zhǔn)確,那么從時(shí)鐘同步時(shí)間的精度就越高。IEEE-1588協(xié)議提供以下方法提高平均路徑延時(shí)D的準(zhǔn)確度:

(1)由于主從時(shí)鐘設(shè)備對(duì)同步報(bào)文的協(xié)議棧處理和操作系統(tǒng)調(diào)度存在不確定的延時(shí)抖動(dòng),造成平均路徑延時(shí)D變化大,準(zhǔn)確度降低,從而降低了同步精度。IEEE-1588提出越往底層打上時(shí)間戳,精度越高。從而消除了軟件處理帶來(lái)的不確定性延時(shí)抖動(dòng),提高了同步精度。

(2)在IEEE-1588第二版本引入的對(duì)等時(shí)鐘中,對(duì)不對(duì)稱的路徑延時(shí)必須做出修正,提高了平均路徑延時(shí)D的準(zhǔn)確度,從而提高了同步精度。

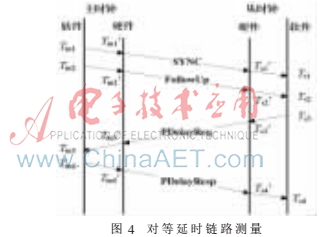

更新版本的IEEE-1588 2008進(jìn)一步引入了對(duì)等時(shí)鐘延時(shí)機(jī)制,同時(shí)增加了3個(gè)額外的事件消息,分別為PdelayReq、PdelayRespFollowUp和PdelayResp。圖4所示包括對(duì)等時(shí)鐘的事件消息交互過程以及時(shí)間戳產(chǎn)生的時(shí)刻和過程。

如圖4所示,可以把延時(shí)計(jì)算分為兩個(gè)過程:主時(shí)鐘到從時(shí)鐘的延時(shí)和從時(shí)鐘到主時(shí)鐘的延時(shí)。

4.1 主時(shí)鐘到從時(shí)鐘的延時(shí)計(jì)算過程

SYNC和FollowUp消息是由主時(shí)鐘發(fā)出,從時(shí)鐘對(duì)消息作出響應(yīng)并計(jì)算出主時(shí)鐘到從時(shí)鐘的傳輸延時(shí)[8]。

主時(shí)鐘設(shè)備讀取軟件時(shí)間戳Tm1,插入到SYNC消息中,然后發(fā)送此消息。接著在SYNC消息離開設(shè)備時(shí),主時(shí)鐘設(shè)備物理層會(huì)自動(dòng)在SYNC消息中的相應(yīng)字段打上硬件時(shí)間戳。SYNC消息到達(dá)從時(shí)鐘時(shí),從時(shí)鐘物理層打上硬件時(shí)間戳T,隨后被從時(shí)鐘軟件接收,標(biāo)記軟件時(shí)間戳Ts1。從時(shí)鐘軟件讀取接收硬件時(shí)間戳T,以便計(jì)算主時(shí)鐘到從時(shí)鐘的傳輸延時(shí)。如果沒有傳輸延時(shí),則Ts1′=Tm1′+Tms成立,其中Tms是主從時(shí)鐘間的時(shí)間差。1588 協(xié)議的最終目標(biāo)就是要補(bǔ)償該時(shí)間差。

SYNC發(fā)送完成后,主時(shí)鐘設(shè)備軟件讀取SYNC消息時(shí)間戳單元的離開時(shí)間T,并把T插入到FollowUp消息中,然后在軟件時(shí)間戳Tm2發(fā)送FollowUp消息。FollowUp消息在從時(shí)鐘設(shè)備的軟件時(shí)間戳Ts2收到。此時(shí),從時(shí)鐘設(shè)備軟件有兩個(gè)時(shí)間點(diǎn)T和T,分別為SYNC到達(dá)時(shí)間戳和SYNC離開時(shí)間戳。主從時(shí)鐘路徑延時(shí)Tmsd:

![WD`YE1YKV}0]8]IT12_}{J1.png WD`YE1YKV}0]8]IT12_}{J1.png](http://files.chinaaet.com/images/2017/01/16/6362017811924453857241291.png)

4.2 從時(shí)鐘到主時(shí)鐘的延時(shí)計(jì)算過程

PDlayReq消息由從時(shí)鐘設(shè)備發(fā)送,主時(shí)鐘接收到PDlayReq消息后,發(fā)送PDlayResp消息作為回應(yīng)。通過此過程,從時(shí)鐘設(shè)備可以計(jì)算出從時(shí)鐘到主時(shí)鐘的傳輸路徑延時(shí)。

如圖4所示,在時(shí)刻Ts3,從時(shí)鐘設(shè)備軟件讀取當(dāng)前的系統(tǒng)時(shí)間Ts3,并插入到PDlayReq消息中,然后發(fā)送出去。發(fā)送完成后,從時(shí)鐘設(shè)備軟件讀取消息離開設(shè)備的硬件時(shí)間戳T,并等待主時(shí)鐘設(shè)備的回應(yīng)。

隨后PDlayReq消息到達(dá)主時(shí)鐘設(shè)備,物理層標(biāo)記硬件時(shí)間戳T,且在軟件時(shí)間戳Tm3時(shí)刻被主時(shí)鐘設(shè)備軟件處理。軟件讀取PDlayReq消息到達(dá)主時(shí)鐘設(shè)備的硬件時(shí)間戳T,并插入到PDlayResp消息中,然后在軟件時(shí)間戳Tm4時(shí)刻發(fā)送給從時(shí)鐘。當(dāng)從時(shí)鐘設(shè)備軟件在軟件時(shí)間戳Ts4接收到PDlayReq消息時(shí),從時(shí)鐘設(shè)備軟件讀取該消息硬件時(shí)間戳T。此時(shí),從時(shí)鐘設(shè)備軟件具有兩個(gè)已知時(shí)間戳T,可以得出從時(shí)鐘到主時(shí)鐘的延時(shí)計(jì)算公式:

在式(3)、式(4)中,有一個(gè)未知量即主從時(shí)鐘間的時(shí)間差Tms,所以不可能求解出Tmsd或Tsmd。然而IEEE-1588協(xié)議的一個(gè)重要的假設(shè)為“傳輸路徑是對(duì)稱的”,即Tmsd=Tsmd=Td。那么可以得出平均路徑延時(shí)Td:

![5~QKVVA9L2~XX7Q]H8$$2W0.png 5~QKVVA9L2~XX7Q]H8$$2W0.png](http://files.chinaaet.com/images/2017/01/16/6362017814509253859788380.png)

從時(shí)鐘需同步于主時(shí)鐘的時(shí)間,以上所有的計(jì)算由從時(shí)鐘完成。從時(shí)鐘從主時(shí)鐘設(shè)備的FollowUp消息中得到T,接收FollowUp消息后得到自身的接收硬件時(shí)間戳T,發(fā)送PDlayReq消息得到自身的發(fā)送硬件時(shí)間戳T以及從主時(shí)鐘設(shè)備PDlayResp消息中抽取的硬件時(shí)間戳T。

4.3 從時(shí)鐘時(shí)間調(diào)整

計(jì)算出從主時(shí)鐘之間的時(shí)延后,需對(duì)從時(shí)鐘作出時(shí)間調(diào)整。這里包括兩方面:(1)需加上與主時(shí)鐘的絕對(duì)偏差以調(diào)整自身的絕對(duì)時(shí)間;(2)調(diào)整自身的時(shí)鐘頻率與主時(shí)鐘同步。

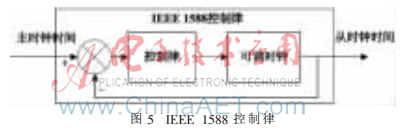

如圖5所示,調(diào)整從時(shí)鐘的控制律,從時(shí)鐘與主時(shí)鐘之間的差別驅(qū)動(dòng)了可調(diào)時(shí)鐘的運(yùn)行。可調(diào)時(shí)鐘分兩個(gè)步驟進(jìn)行,使得從時(shí)鐘的時(shí)間增長(zhǎng)不產(chǎn)生向前跳躍或向后折回:(1)當(dāng)時(shí)間差大于1 s時(shí),從時(shí)鐘采用絕對(duì)時(shí)間調(diào)整;(2)當(dāng)時(shí)間差在1 s內(nèi)時(shí),從時(shí)鐘采用頻率調(diào)節(jié)。

5 試驗(yàn)測(cè)試結(jié)果

測(cè)試環(huán)境是采用兩塊時(shí)鐘板卡直接連接進(jìn)行主從時(shí)鐘的對(duì)時(shí),主從時(shí)鐘輸出的PPS通過示波器保存處理。圖6所示是實(shí)驗(yàn)測(cè)試數(shù)據(jù),橫坐標(biāo)為對(duì)時(shí)次數(shù),縱坐標(biāo)為主從時(shí)延,單位為ns。

正值處理后的主從時(shí)鐘對(duì)時(shí)數(shù)據(jù)如表1所示。實(shí)驗(yàn)數(shù)據(jù)表明,主從時(shí)鐘對(duì)時(shí)精度在100 ns之內(nèi),且有90.26%的數(shù)據(jù)在50 ns內(nèi)。

由實(shí)驗(yàn)測(cè)試數(shù)據(jù)可知,對(duì)時(shí)精度滿足電力系統(tǒng)應(yīng)用的要求。可以得出結(jié)論:(1)通過本文介紹的在MII層標(biāo)記硬件時(shí)間戳的方式,可以消除操作系統(tǒng)和協(xié)議棧處理產(chǎn)生的延時(shí),更精確地標(biāo)記硬件時(shí)間戳,從而提高了對(duì)時(shí)精度;(2)以太網(wǎng)PHY芯片采用美國(guó)國(guó)家半導(dǎo)體DP83848,因?yàn)樗哂械偷难訒r(shí)抖動(dòng)特性,百兆網(wǎng)速的點(diǎn)對(duì)點(diǎn)主從對(duì)時(shí)產(chǎn)生的物理層延時(shí)抖動(dòng)非常微小。

參考文獻(xiàn)

[1] IEC 61850.Communication networks and systems in substa-tions[S].2003.

[2] 國(guó)家電網(wǎng)公司.智能變電站技術(shù)導(dǎo)則[Z].2009.

[3] 王水魚,魏傳均.基于IEEE 1588的智能變電站時(shí)鐘同步技術(shù)研究[J].微型機(jī)與應(yīng)用,2012,31(23):78-81.

[4] 黃健,劉鵬,楊瑞民.IEEE 1588精確時(shí)鐘同步協(xié)議從時(shí)鐘設(shè)計(jì)[J].電子技術(shù)應(yīng)用,2010,36(7):91-97,108.

[5] 魏豐,孫文杰.IEEE-1588協(xié)議時(shí)鐘同步報(bào)文的精確時(shí)間標(biāo)記方法研究[J].儀器儀表學(xué)報(bào),2009,30(1):162-169.

[6] 胡永春,張雪松,許偉國(guó),等.IEEE-1588時(shí)鐘同步系統(tǒng)誤差分析及其檢測(cè)方法[J].電力系統(tǒng)自動(dòng)化,2010,34(21):107-110.

[7] 陳炯聰.IEEE 1588同步技術(shù)在電力系統(tǒng)中的應(yīng)用[M].北京:中國(guó)電力出版社,2012.

[8] IEEE Std.1588-2008.1588 IEEE standard for a precision clock synchronization protocol for networked measurement and control systems[S].2008.