阮崢,陳亮,王寶瑛

(公安部第三研究所,上海 201204)

摘要:通信系統(tǒng)中,數(shù)字復(fù)接是提高帶寬利用率的一項(xiàng)重要技術(shù),將多路并行低速信號(hào)轉(zhuǎn)變?yōu)楦弑忍芈实拇袛?shù)字流。首先使用Cadence軟件仿真基本門級(jí)CMOS電路,通過自下而上的FPGA設(shè)計(jì)方法和Verilog硬件描述語言,設(shè)計(jì)四路串行復(fù)接器的功能組成模塊,完成Quartus II平臺(tái)上的可綜合驗(yàn)證。最后提出了復(fù)接器CMOS集成電路的設(shè)計(jì)思路。

關(guān)鍵詞:門級(jí)電路;Verilog;Quartus II;復(fù)接器;CMOS集成電路

0引言

通信系統(tǒng)中,一路獨(dú)立信號(hào)的速率通常都是較低的,通信設(shè)備的帶寬卻相對(duì)較大。多路復(fù)用技術(shù)正是解決信源速率與傳輸帶寬之間不對(duì)稱問題的有效途徑之一,通常使用頻分復(fù)用、時(shí)分復(fù)用、波分復(fù)用和碼分復(fù)用四種復(fù)用系統(tǒng)。基于時(shí)分復(fù)用理論的復(fù)接器,按照時(shí)序依次將N路相同速率和相位的低速信號(hào)整合為一路N倍速率的高速信號(hào),以提高傳輸物理介質(zhì)帶寬的利用率。隨著電路制作工藝的不斷進(jìn)步,復(fù)接器系統(tǒng)可以由多種基本復(fù)接電路組合,來實(shí)現(xiàn)Gb/s級(jí)別的工作速率,因而普遍用于通信系統(tǒng)的信道接口部分[1]。

集成電路設(shè)計(jì)之前一般需要經(jīng)過現(xiàn)場(chǎng)可編輯邏輯陣列(FPGA)的功能驗(yàn)證。作為一種通用半定制電路,F(xiàn)PGA的硬件驗(yàn)證可以方便在電路設(shè)計(jì)的早期發(fā)現(xiàn)問題,達(dá)到降低研發(fā)費(fèi)用、縮短開發(fā)周期的效果,因此對(duì)芯片的邏輯綜合和版圖設(shè)計(jì)具有重要意義。

本文在4∶1串行復(fù)接器的經(jīng)典設(shè)計(jì)原理基礎(chǔ)上,介紹基本門級(jí)CMOS電路的仿真,并在Quartus下設(shè)計(jì)驗(yàn)證復(fù)接器各組成電路模塊,分析電路時(shí)序邏輯功能。

1基本門級(jí)電路的CMOS設(shè)計(jì)仿真

基本非門和與非門的CMOS電路如圖1所示。

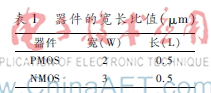

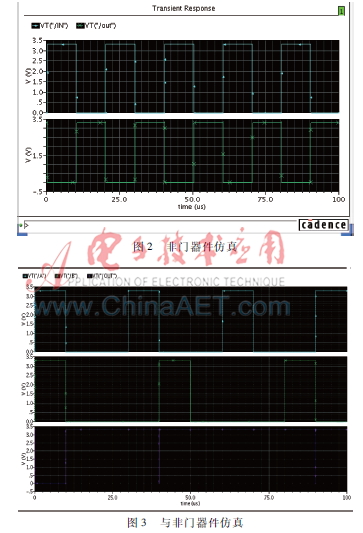

PMOS管和NMOS管的兩個(gè)柵極相連作為輸入,各自的漏極相連作為輸出,當(dāng)輸入信號(hào)IN大于NMOS的閾值電壓時(shí),M1導(dǎo)通,PMOS管截止,輸出信號(hào)OUT接地,為低電平輸出;當(dāng)IN低于閾值電壓時(shí),M0導(dǎo)通,M1截止,輸出信號(hào)OUT與VCC形成通路,輸出高電平,這樣就構(gòu)成了圖1所示的非門,又稱反相器。兩個(gè)PMOS管并聯(lián)后再與兩個(gè)串聯(lián)的NMOS管相連,構(gòu)成二輸入的與非門。當(dāng)輸入INA和INB其中一個(gè)或者全都為低電平,M3、M2中的一個(gè)或全部導(dǎo)通,輸出信號(hào)OUT與高電平VCC形成通路,輸出高電平;當(dāng)且僅當(dāng)輸入全為高電平時(shí),M1、M2導(dǎo)通,輸出信號(hào)OUT直接接地,輸出低電平,構(gòu)成圖1所示的與非門電路[2]。借助Cadence軟件,按照表1給出的參數(shù)設(shè)置器件的寬長(zhǎng)值,對(duì)非門、與非門進(jìn)行器件仿真。表1器件的寬長(zhǎng)比值(μm) 器件寬(W)長(zhǎng)(L)PMOS20.5NMOS30.5器件仿真的結(jié)果如圖2、圖3所示,可以看出符合相應(yīng)器件的邏輯特性。

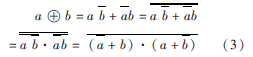

圖5四路串行復(fù)接器原理圖其他基本門電路邏輯如公式(1)~(3)所示:

式中a、b表示二輸入邏輯門的輸入信號(hào)。

公式表明,或門、異或門等基本電路都可以由與門、與非門構(gòu)成,稱之為基本CMOS邏輯門電路。基本門級(jí)電路繼續(xù)構(gòu)成多種形式和驅(qū)動(dòng)能力的觸發(fā)器、多路器、緩沖器等基本電路單元,并且作為集成電路制造廠家的標(biāo)準(zhǔn)單元庫(kù),提供給設(shè)計(jì)人員使用。需求電路的邏輯設(shè)計(jì)驗(yàn)證后,再進(jìn)行電路的版圖設(shè)計(jì)、驗(yàn)證、后仿真、流片、測(cè)試,最終在管級(jí)器件上實(shí)現(xiàn)[3]。

2復(fù)接原理

數(shù)字復(fù)接的作用是將低速數(shù)據(jù)碼流變換成高速數(shù)據(jù)碼流的設(shè)備[4]。圖4為M路信號(hào)的復(fù)接示意圖,M路信號(hào)在時(shí)序控制電路作用下,由時(shí)鐘信號(hào)控制時(shí)序,有條不紊地復(fù)接每一路獨(dú)立信源,依次輸出復(fù)接信號(hào),其實(shí)質(zhì)是在抽樣時(shí)間內(nèi)傳輸一路數(shù)據(jù),在其他時(shí)隙用于傳輸其他路信源數(shù)據(jù)。

4∶1串行復(fù)接器電路系統(tǒng)由三個(gè)D觸發(fā)器、三個(gè)2∶1的通道選擇器以及一個(gè)1:4分頻器構(gòu)成[5],如圖5所示。D觸發(fā)器用于數(shù)據(jù)鎖存,通道選擇器作為單刀雙擲開關(guān)。時(shí)鐘信號(hào)上升沿觸發(fā)觸發(fā)器,鎖存前端選擇器的輸出比特。分頻信號(hào)觸發(fā)通道選擇,高電平選擇信號(hào)a,低電平選擇信號(hào)b。如分頻信號(hào)正向脈沖期間,數(shù)據(jù)D1的一個(gè)比特直接輸出,而時(shí)鐘信號(hào)上升沿將數(shù)據(jù)D2,D3,D4的比特鎖存在相應(yīng)的D觸發(fā)器中,直到分頻信號(hào)負(fù)向脈沖到來移出,這樣D1、D2、D3、D4的數(shù)據(jù)一位接一位地輸出,表現(xiàn)為數(shù)據(jù)的復(fù)接。

數(shù)據(jù)復(fù)接的條件如下:

(1)需要復(fù)接的數(shù)據(jù)在一個(gè)分頻時(shí)鐘周期內(nèi)保持穩(wěn)定。

(2)時(shí)鐘信號(hào)的上升沿觸發(fā)鎖存,通道選擇器高電平輸入選擇信號(hào)a,低電平輸入選信號(hào)b。

(3)分頻器輸出占空比必須為1∶3。

在CK/4信號(hào)的正向脈沖期間,D觸發(fā)器和選擇器組成了一個(gè)移位寄存器。存儲(chǔ)的數(shù)據(jù)D2、D3和D4一位接一位輸出。任何占空比的分頻器都可以通過硬件描述語言實(shí)現(xiàn)[6]。電路用到兩個(gè)時(shí)鐘信號(hào):頻率等于復(fù)接器輸出比特率的時(shí)鐘信號(hào)和只有輸出頻率1/4的分頻信號(hào),前者用于數(shù)據(jù)寄存,后者用于數(shù)據(jù)移位,低速時(shí)實(shí)現(xiàn)相對(duì)容易。隨著輸出速率提高以及復(fù)接信號(hào)源數(shù)目的增加,D觸發(fā)器的速率可能限制整個(gè)電路的輸出速率,同時(shí)通道選擇器在一個(gè)輸出比特的周期內(nèi)要完成信號(hào)的選擇,需要的速度也必須很高,功耗的問題也會(huì)表現(xiàn)出來,因?yàn)樗蠨觸發(fā)器都工作在最高頻率的時(shí)鐘信號(hào)上,而CMOS管的功耗與翻轉(zhuǎn)頻率成正比。

這種結(jié)構(gòu)的電路運(yùn)行速度取決于n級(jí)移位寄存器和時(shí)鐘通道的第一級(jí)分頻器。D觸發(fā)器的速度有可能限制分接器的速度,因?yàn)檎麄€(gè)移位寄存器鏈路和分頻器的第一級(jí)中的D觸發(fā)器的頻率必須等于輸出的速度。另外,所有通道選擇器的速度也必須很高,因?yàn)樗鼈冊(cè)谝粋€(gè)輸出數(shù)據(jù)比特周期內(nèi)必須完成選擇的功能。因此,電路設(shè)計(jì)所用的技術(shù)是非常關(guān)鍵的,因?yàn)樗幸莆患拇嫫鞫际侵鲝挠|發(fā)器,為達(dá)到高速,通道選擇器也需要大電流。這樣功耗就會(huì)很高。

3程序設(shè)計(jì)

3.1觸發(fā)器的設(shè)計(jì)

時(shí)鐘信號(hào)上升沿時(shí)刻,寄存并輸出信號(hào)源。可綜合Verilog代碼片段如下:

always @(posedge clk)

begin

q<=d;

end

3.2二選一電路的設(shè)計(jì)

根據(jù)輸入信號(hào)電平的高低,決定輸出選擇信號(hào)的二選一電路模塊的代碼片段如下:

always@(sl or a or b)

if(sl)

out<=a;

else

out<=b;

3.3分頻器電路的設(shè)計(jì)

分頻器電路可以借助狀態(tài)機(jī)、計(jì)數(shù)器兩種基本方法,根據(jù)不同的占空比要求來選擇。這里采用計(jì)數(shù)器原理來實(shí)現(xiàn)占空比為1∶3的分頻器設(shè)計(jì),代碼片段如下:

always @(posedge clk)

if(count==2'b00)

out<=1;

count<=count+1;

else

out<=0;

if(count==2'b11)

count<=2'b00;

else

count<=count+1;

4結(jié)論

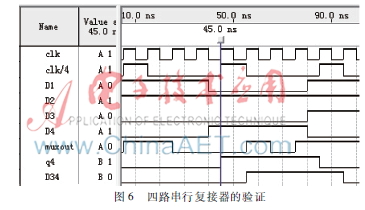

電路模塊各自得到Quartus II仿真驗(yàn)證后,由當(dāng)前文件形成各自symbol文件,用于完成復(fù)接器工程原理圖的自下而上的設(shè)計(jì)。復(fù)接器中所有的過程信號(hào)都以管腳信號(hào)輸出,用以顯示功能驗(yàn)證的正確性。

截取的功能仿真結(jié)果如圖6所示。仿真中添加了圖5電路中以D4作為輸入信號(hào)的觸發(fā)器的輸出信號(hào)q4、以D3作為輸入信號(hào)a的二選一電路的輸出D34和分頻器的輸出信號(hào)clk/4。可以看到,時(shí)鐘信號(hào)clk的周期為10 ns,分頻后輸出信號(hào)的周期為40 ns,頻率為時(shí)鐘信號(hào)的1/4,占空比為1∶3。q4在時(shí)鐘上升沿鎖存D4信號(hào),與其電平保持一致。D34在分頻信號(hào)為高電平時(shí)刻選擇信號(hào)D3,低電平時(shí)刻選擇信號(hào)D4。在第一個(gè)時(shí)隙(5 ns~45 ns)內(nèi),D1~D4輸入數(shù)據(jù)依次為1,1,0,0,這一時(shí)期的輸出復(fù)接信號(hào)muxout為1100,達(dá)到信號(hào)復(fù)接要求;第二個(gè)時(shí)隙(45 ns~85 ns)內(nèi)D1~D4輸入數(shù)據(jù)依次為0,1,0,1,其間輸出復(fù)接信號(hào)muxout為0101,滿足信號(hào)復(fù)接要求;后續(xù)時(shí)隙仿真功能依然正確。經(jīng)可綜合風(fēng)格的硬件描述語言驗(yàn)證的電路,再通過集成電路設(shè)計(jì)專用工具,邏輯綜合成邏輯門電路網(wǎng)表,由CMOS標(biāo)準(zhǔn)單元庫(kù)最終完成復(fù)接器集成電路的設(shè)計(jì)制造。

參考文獻(xiàn)

[1] 楊洋. 0.6umCMOS 4:1高速?gòu)?fù)接器設(shè)計(jì)[D]. 合肥:合肥工業(yè)大學(xué),2007.

[2] 凌云. 高速?gòu)?fù)接器設(shè)計(jì)[M].南京:東南大學(xué)出版社,2006.

[3] 王志功,景為平,孫玲. 集成電路設(shè)計(jì)技術(shù)與工具[M]. 南京:東南大學(xué)出版社,2007.

[4] 趙怡,但濤. 基于FPGA的多路數(shù)字信號(hào)復(fù)接系統(tǒng)設(shè)計(jì)與實(shí)現(xiàn)[J].電子科技,2013,26(12):3739.

[5] 左曉偉. 光纖復(fù)接器CMOS集成電路設(shè)計(jì)[M]. 南京:東南大學(xué)出版社,2007.

[6] 夏宇聞. Verilog數(shù)字系統(tǒng)設(shè)計(jì)教程(第2版)[M].北京:北京航空航天大學(xué)出版社,2008.(收稿日期:20160317)