摘 要: 描述了基于I2C總線多步進(jìn)電機(jī)平臺(tái)的設(shè)計(jì),介紹了I2C總線通信協(xié)議的特點(diǎn),給出了I2C總線在1片主MSP430G2553和8片從MSP430G2553之間數(shù)據(jù)傳輸程序流程圖和整個(gè)平臺(tái)的硬件結(jié)構(gòu)框架,完成了基于I2C總線的單主多從通信,最終實(shí)現(xiàn)了對(duì)多路步進(jìn)電機(jī)的控制。

關(guān)鍵詞: I2C總線;MSP430G2553;單主多從;步進(jìn)電機(jī)

0 引言

I2C總線是兩線式串行總線,用于連接微控制器及其外圍設(shè)備,是微電子通信控制領(lǐng)域廣泛采用的一種總線標(biāo)準(zhǔn)。它是同步通信的一種特殊形式,具有接口線少、控制方式簡(jiǎn)單、器件封裝形式小、通信速率較高等優(yōu)點(diǎn)。本文介紹一種利用I2C總線協(xié)議,通過(guò)單主多從模式,利用1段音頻信號(hào)控制8個(gè)單片機(jī)實(shí)現(xiàn)不同方向、速率的轉(zhuǎn)動(dòng)。

1 I2C總線技術(shù)

1.1 I2C總線接口

本文所用的芯片主要為TI公司的MSP430G2553芯片,其中的I2C模式是通過(guò)USCI_Bx模塊來(lái)進(jìn)行配置的,本文主要應(yīng)用了USCI_B0模塊[1]。在I2C模式中,USCI通過(guò)兩線式I2C串行總線提供了MSP430與I2C兼容器件的連接。外部器件串行依附在I2C總線上,通過(guò)2-線I2C接口為USCI模塊發(fā)送數(shù)據(jù)或從USCI接收數(shù)據(jù)。如圖1所示,I2C總線由時(shí)鐘線SCL和數(shù)據(jù)線SDA構(gòu)成,在時(shí)鐘線SCL保持高電平期間,數(shù)據(jù)線SDA上的電平被拉低(即負(fù)跳變),為I2C的開始信號(hào)[2]。在時(shí)鐘線SCL保持高電平期間,數(shù)據(jù)線SDA被釋放,是I2C的終止信號(hào)。

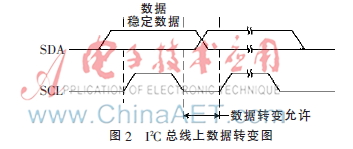

如圖2所示,進(jìn)行數(shù)據(jù)傳送時(shí),在SCL呈現(xiàn)高電平期間,SDA上的電平必須保持穩(wěn)定,只有在SCL為低電平期間,才允許SDA上的電平改變狀態(tài)。

關(guān)于傳輸速度,I2C總線在標(biāo)準(zhǔn)模式最高為100 kb/s,高速模式最高為400 kb/s。

1.2 I2C總線數(shù)據(jù)傳輸

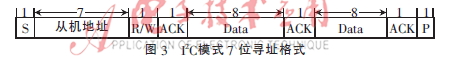

I2C總線傳輸數(shù)據(jù)必須遵循規(guī)定的數(shù)據(jù)傳輸格式[2],主機(jī)給每個(gè)數(shù)據(jù)傳輸位產(chǎn)生一個(gè)時(shí)鐘脈沖,I2C模式對(duì)數(shù)據(jù)位進(jìn)行操作。在主機(jī)設(shè)置好I2C為發(fā)送模式后,USCI模塊會(huì)檢測(cè)總線是否可用,產(chǎn)生START條件。本文中將音頻信號(hào)依據(jù)頻率分為8段,并且每段對(duì)應(yīng)不同的從機(jī)地址,如此便可依據(jù)不同頻率將音頻信號(hào)發(fā)送給不同的從機(jī)。I2C模式支持7位和10位尋址模式[3],本文運(yùn)用了7位尋址模式。如圖3所示,在7位尋址模式中,第一個(gè)字節(jié)是7位從機(jī)地址和R/W位。接收器在每個(gè)字節(jié)結(jié)束后發(fā)送ACK位。

所有掛到I2C總線的外圍器件各自都有一個(gè)唯一確定的地址[2]。任何時(shí)刻總線上只有一個(gè)主控器件對(duì)總線實(shí)行控制權(quán),分時(shí)實(shí)現(xiàn)點(diǎn)對(duì)點(diǎn)的數(shù)據(jù)傳送。I2C總線上所有外圍器件都有規(guī)范的器件地址,器件地址由7位組成,它和1位方向位(R/W)構(gòu)成了I2C總線器件的尋址字節(jié)SLA,格式如圖4所示。

其中高4位(A6、A5、A4、A3)是I2C總線外圍接口器件固有地址編碼,器件出廠時(shí)已固化好。A0~A2是對(duì)從機(jī)分配的不同地址,本文中MSP430G2553的高4位為0100[1],一共可以掛接8個(gè)單片機(jī)。而最低位R/W為數(shù)據(jù)方向位,當(dāng)R/W為0時(shí),主機(jī)發(fā)送數(shù)據(jù),當(dāng)R/W為1時(shí),主機(jī)接收數(shù)據(jù)。本文中主機(jī)只用于發(fā)送數(shù)據(jù),故R/W位一直為0。本文中的8個(gè)從機(jī)地址分別為:40H、42H、44H、46H、48H、4AH、4CH和4EH。

故總線上的數(shù)據(jù)傳輸過(guò)程[4]是:(1)主控制器發(fā)送開始信號(hào)S;(2)主控制器發(fā)送芯片尋址字節(jié);(3)從器件發(fā)出應(yīng)答信號(hào)ACK;(4)主控制器發(fā)送數(shù)據(jù)尋址字節(jié);(5)發(fā)送者發(fā)送數(shù)據(jù),接受者接收數(shù)據(jù);(6)主控制器發(fā)送停止信號(hào)P終止數(shù)據(jù)傳輸。其流程圖如圖5所示。

2 I2C的系統(tǒng)硬件結(jié)構(gòu)

圖6是本文所研究平臺(tái)的整體框圖,在此系統(tǒng)中8個(gè)從機(jī)對(duì)應(yīng)8種不同音符頻段,分別控制8個(gè)電機(jī)的轉(zhuǎn)速。系統(tǒng)的主要功能是通過(guò)PC由MATLAB對(duì)給定音頻進(jìn)行編碼[5],產(chǎn)生單片機(jī)可用的曲譜編碼,然后通過(guò)串口將所產(chǎn)生的編碼發(fā)送給主MSP430G2553,主機(jī)在尋址時(shí)先判斷編碼范圍,然后通過(guò)I2C總線尋址相應(yīng)的從機(jī),并向被尋址的MSP430G2553發(fā)送相應(yīng)的音頻編碼。從機(jī)將所接收到的音頻編碼作為定時(shí)器的定時(shí)周期,利用定時(shí)器產(chǎn)生相應(yīng)的脈沖信號(hào),從而驅(qū)動(dòng)電機(jī)轉(zhuǎn)動(dòng)。

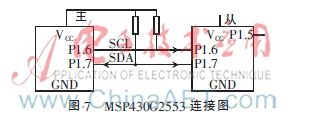

為實(shí)現(xiàn)單主多從單片機(jī)MSP430G2553之間的通信,將主機(jī)I2C總線上的SCL(P1.6)和SDA(P1.7)分別與從機(jī)的SCL(P1.6)和SDA(P1.7)相連接,并且在VCC與SCL、SDA兩個(gè)信號(hào)之間分別接上10 k?贅的上拉電阻,如圖7所示。由此從機(jī)的P1.6就成了時(shí)鐘接收端,P1.7為數(shù)據(jù)接收端。通過(guò)編程將主機(jī)發(fā)送的數(shù)據(jù)送入Buff,從機(jī)通過(guò)讀Buff中的數(shù)據(jù)將其實(shí)時(shí)轉(zhuǎn)換為頻率改變的方波,并通過(guò)P1.5口將其發(fā)送給電機(jī)驅(qū)動(dòng)器,從而實(shí)現(xiàn)控制步進(jìn)電機(jī)的功能。

3 I2C單主多從通信

首先將USCI模塊初始化,使主機(jī)/從機(jī)可以進(jìn)行接收/發(fā)送操作,初始化過(guò)程如下[6]:將USCI中軟件復(fù)位位UCSWRST置位來(lái)初始化所有的USCI寄存器,配置P1.6和P1.7分別為I2C的SCL端口和SDA端口,通過(guò)UCMST和UCMODEx選擇I2C模式和主機(jī)或從機(jī)模式。然后通過(guò)置位UCSEEL_2來(lái)選擇主機(jī)時(shí)鐘為SMCLK (1 MHz),并將主時(shí)鐘12分頻為100 kHz作為主機(jī)中的SCL時(shí)鐘[1]。上述模塊初始化完成后,清除UCSWRST,釋放USCI,使能發(fā)送中斷。

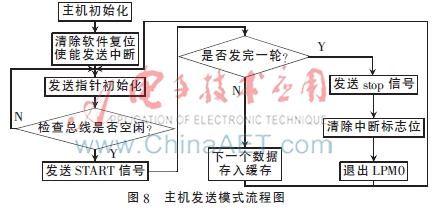

對(duì)于主發(fā)送模塊,初始化之后需要把從地址設(shè)置為7 bit,再將目標(biāo)從地址寫入寄存器UCB0I2CSA中。本系統(tǒng)將所給的音頻信號(hào)按照頻率分為8段,每段對(duì)應(yīng)不同的從機(jī)地址,使主機(jī)通過(guò)判斷與不同的從機(jī)地址相匹配。初始化完成后通過(guò)置位UCRT和UCTXSTT,使主機(jī)工作在發(fā)送模式并產(chǎn)生一個(gè)起始條件。當(dāng)?shù)刂纷x入U(xiǎn)CB0I2CSA中后,硬件會(huì)自動(dòng)識(shí)別并找到與之相對(duì)應(yīng)的從機(jī),一旦地址匹配則UCSTTIFG置位,主機(jī)進(jìn)入LPM0模式并且觸發(fā)中斷,將要發(fā)送的數(shù)據(jù)寫入U(xiǎn)CB0TXBUF中,當(dāng)從機(jī)地址被應(yīng)答時(shí)UCTXSTT位即刻清零。本文中將音頻信號(hào)裝入數(shù)組中,當(dāng)所有數(shù)據(jù)發(fā)送完畢后產(chǎn)生一個(gè)STOP條件,并將UCB0TXIFG清零同時(shí)退出低功耗模式。圖8為主機(jī)發(fā)送模式流程圖。

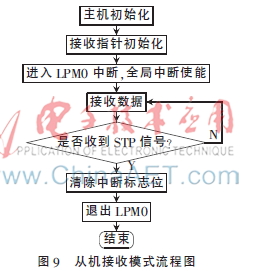

對(duì)于從接收模塊,由于要對(duì)主機(jī)中讀取的數(shù)據(jù)進(jìn)行處理,本文中選用定時(shí)器A將其數(shù)據(jù)轉(zhuǎn)換為對(duì)應(yīng)的脈沖波,從而達(dá)到控制電機(jī)的目的。因此需要先將定時(shí)器A初始化[7],為了不影響主機(jī)中SMCLK,本文使定時(shí)器A工作在ACLK時(shí)鐘下。隨后將其USCI模塊設(shè)置為I2C接收模式,并且無(wú)需設(shè)置USCI時(shí)鐘。一旦從設(shè)備中UCB0RXBUF接收到的新數(shù)據(jù)被讀走,從設(shè)備即發(fā)送一個(gè)應(yīng)答信號(hào)給主設(shè)備,然后開始下一個(gè)數(shù)據(jù)的接收。定時(shí)器A將接收到的數(shù)據(jù)通過(guò)定時(shí)器中斷產(chǎn)生頻率改變的方波,并通過(guò)P1.5口輸出,從而控制步進(jìn)電機(jī)依據(jù)音頻信號(hào)的不同頻率來(lái)變速轉(zhuǎn)動(dòng)。圖9為從機(jī)接收模式流程圖。

4 結(jié)論

本文介紹的I2C總線單主多從通信系統(tǒng)占用I/O資源少,功耗低,傳輸速率高,能夠以較高性能控制步進(jìn)電機(jī)隨音樂(lè)轉(zhuǎn)動(dòng)。從實(shí)驗(yàn)結(jié)果來(lái)看,主從單片機(jī)可以通過(guò)該總線系統(tǒng)進(jìn)行非常可靠的通信,進(jìn)而可在各個(gè)領(lǐng)域取得廣泛應(yīng)用。

參考文獻(xiàn)

[1] MSP430x2xx Users′ guide[Z].2004.

[2] 沈建華,楊艷琴,翟驍曙.MSP430系列16位超低功耗單片機(jī)原理與應(yīng)用[M].北京:清華大學(xué)出版社,2004.

[3] 賈朱紅,張曉冬.基于I2C總線的單主多從單片機(jī)之間的通信[J].微計(jì)算機(jī)信息,2009(8):101-102.

[4] 鄧忠華,李霞,陳浩.I2C總線技術(shù)在單片機(jī)串行擴(kuò)展中的應(yīng)用[J].武漢理工大學(xué)學(xué)報(bào)(交通科學(xué)與工程版),2005(2):227-229,247.

[5] 孫金中,馮炳軍.基于I2C總線控制的音頻處理電路設(shè)計(jì)[J].現(xiàn)代電子技術(shù),2009(18):85-88.

[6] 吳小平,李莉,何鑫,等.I2C總線及其數(shù)據(jù)通信編程[J].微計(jì)算機(jī)信息,2000(2):11-13.

[7] 陳光建,賈金玲.基于單片機(jī)的I2C總線系統(tǒng)設(shè)計(jì)[J].儀器儀表學(xué)報(bào),2006(S3):2465-2466,2472.