摘 要: 完成逐次逼近邏輯的逐次逼近寄存器(SAR)在逐次逼近模數(shù)轉(zhuǎn)換器(ADC)中的設(shè)計(jì)相當(dāng)重要,它控制著整個(gè)SAR ADC的正常運(yùn)行。提出一種新型且結(jié)構(gòu)簡(jiǎn)單、能在一次AD轉(zhuǎn)換中基于同一組時(shí)鐘序列信號(hào)同時(shí)完成兩路12 bit數(shù)據(jù)(即24 bit數(shù)據(jù))信號(hào)的逐位逼近轉(zhuǎn)換和存儲(chǔ)的無(wú)冗余碼SAR結(jié)構(gòu)。基于CSMC 0.5 m CMOS工藝采用全原理圖輸入的方法來(lái)實(shí)現(xiàn),最大程度地簡(jiǎn)化了電路結(jié)構(gòu)和面積,效率高且開(kāi)關(guān)功耗可降到最小。

關(guān)鍵詞: D觸發(fā)器;逐次逼近;時(shí)鐘序列信號(hào);寄存器

0 引言

現(xiàn)代生活中,通常需要將周圍環(huán)境中的溫度、壓力、電流等模擬信息采集后以圖像的形式立即顯示在屏幕上,或者以聲音的形式傳送,以能更方便地觀測(cè)和分析,達(dá)到智能人機(jī)交互的目的,這一過(guò)程必定缺少不了將模擬量正確轉(zhuǎn)化為數(shù)字量的模數(shù)轉(zhuǎn)換器(ADC)。常用的逐次逼近型ADC具有速度高、功耗低且價(jià)格便宜的優(yōu)點(diǎn)[1],可以滿足許多便攜式、工業(yè)、醫(yī)療等領(lǐng)域數(shù)據(jù)采集應(yīng)用的需求。SAR ADC中SAR控制著轉(zhuǎn)換器的運(yùn)行,是一個(gè)十分重要的子電路,參考文獻(xiàn)[2]和參考文獻(xiàn)[3]的SAR通過(guò)編寫(xiě)Verilog代碼經(jīng)綜合工具綜合后得到,但對(duì)于逐次逼近寄存器,采用該方法進(jìn)行綜合后將會(huì)需要調(diào)用比較多的D觸發(fā)器以及門(mén)級(jí)電路,這將會(huì)增大開(kāi)關(guān)功耗[4-5]和電路面積,且通常需要同時(shí)處理較多的數(shù)據(jù)信息,因此將寄存器電路規(guī)模優(yōu)化設(shè)計(jì)至最簡(jiǎn)單化、無(wú)冗余碼、減小面積和功耗具有十分重要的意義。基于此,本文提出一種新型的適用于兩路12位ADC的逐次逼近型寄存器結(jié)構(gòu)的實(shí)現(xiàn)方法,并對(duì)具體電路設(shè)計(jì)和時(shí)序進(jìn)行詳細(xì)分析。

1 SAR在ADC中的逐次逼近邏輯

逐次逼近型ADC主要由采樣保持放大器(SHA)、模擬比較器、參考數(shù)模轉(zhuǎn)換器(DAC)和逐次逼近型寄存器(SAR)構(gòu)成。如圖1所示[6],逐次逼近型ADC是一種使用二進(jìn)制搜索算法使得DAC的輸出逐次逼近輸入模擬信號(hào)V1的反饋系統(tǒng),逐次逼近型寄存器SAR控制著轉(zhuǎn)換的運(yùn)行。

SAR控制過(guò)程[7-8]:在模數(shù)轉(zhuǎn)換開(kāi)始之前,SAR(由N位移位寄存器和N位保持寄存器構(gòu)成)被清零,首先采樣保持后的模擬輸入信號(hào)V1輸入到比較器的一端,變換過(guò)程從數(shù)字信號(hào)的最高位開(kāi)始到最低位逐次試探、逼近。在第一個(gè)時(shí)鐘周期,SAR的最高位MSB置“1”,其他各位仍保持為零,N位保持寄存器將輸出加載到N位DAC產(chǎn)生相應(yīng)的模擬信號(hào)V0(此刻V0=1/2Vref,Vref為參考電壓),如果1/2Vref≤V1,則比較器的輸出保持不變,SAR的最高位MSB保存為“1”,否則保存為“0”,至此確定了SAR的最高位。在第二個(gè)周期,將“1”送入N位保持寄存器的次高位,如果前一個(gè)轉(zhuǎn)換周期確定的MSB=1,那么此時(shí)DAC輸出3/4 Vref,Vin與3/4 Vref比較大小,從而確定SAR次高位;如果前一個(gè)轉(zhuǎn)換周期確定的MSB=0,那么此時(shí)DAC輸出1/4 Vref,Vin與1/4 Vref比較大小,從而確定SAR次高位。依次類推,從高到低位一次逐一進(jìn)行試探,試探位借助于N位序列信號(hào)發(fā)生器(移位寄存器)從MSB順次移向LSB。N位數(shù)字信號(hào)逐次逼近的過(guò)程需要N個(gè)時(shí)鐘周期。判斷試探的“1”究竟是保持還是被“0”所取代,由比較器和逐次逼近寄存器邏輯完成,每次逼近動(dòng)作由時(shí)鐘信號(hào)同步,且每次逼近的結(jié)果存留在保持寄存器中。在MSB到LSB各位的試探都結(jié)束后,控制邏輯發(fā)出一個(gè)狀態(tài)信號(hào),允許數(shù)字輸出。

2 SAR的設(shè)計(jì)

本文設(shè)計(jì)的SAR在同一組時(shí)鐘序列信號(hào)下可同時(shí)完成兩路數(shù)據(jù)信號(hào)的逐位逼近轉(zhuǎn)換和存儲(chǔ),采用直接原理圖輸入的方式[9],基于D觸發(fā)器和非門(mén)、與非門(mén)、或非門(mén)等門(mén)級(jí)單元電路完成了序列信號(hào)產(chǎn)生器和保持寄存器兩個(gè)部分邏輯電路的設(shè)計(jì)和仿真驗(yàn)證,采用最少的D觸發(fā)器,具有更高效的轉(zhuǎn)換效果,以下進(jìn)行詳細(xì)分析。

2.1 D觸發(fā)器的設(shè)計(jì)

本文采用具有低電平異步復(fù)位、上升沿觸發(fā)的D觸發(fā)器,原理圖如圖2所示。通過(guò)非門(mén)、傳輸門(mén)和與非門(mén)的邏輯組合形成主、從觸發(fā)器,再經(jīng)過(guò)主從觸發(fā)器的級(jí)聯(lián)構(gòu)成該DFF。其中RB端為復(fù)位信號(hào)且低電平有效。當(dāng)RB為0時(shí),將a、b兩點(diǎn)維持的信息清零,也將c、d兩點(diǎn)維持的信號(hào)清零并將低電平送到Q端。RB為1時(shí),當(dāng)CK=0,傳輸門(mén)TG1打開(kāi),D端數(shù)據(jù)送到主觸發(fā)器中并保存,當(dāng)CK=1時(shí)傳輸門(mén)TG2打開(kāi),保存在主觸發(fā)器的數(shù)據(jù)送入從觸發(fā)器中,最終從Q端輸出,至此完成一個(gè)時(shí)鐘信號(hào)作用下將D端輸入數(shù)據(jù)送到Q端的功能。當(dāng)時(shí)鐘下降沿再次到達(dá)時(shí),主觸發(fā)器才再次接收新數(shù)據(jù),而從觸發(fā)器鎖存原來(lái)的數(shù)據(jù),只有當(dāng)時(shí)鐘上升沿再次到達(dá)時(shí)從觸發(fā)器才翻轉(zhuǎn)從而輸出新的數(shù)據(jù)。圖3為該D觸發(fā)器的功能仿真結(jié)果。圖4為該D觸發(fā)器的晶體管級(jí)電路圖。

2.2 12 bits序列信號(hào)產(chǎn)生器的設(shè)計(jì)及仿真

移位寄存器是指寄存器里存儲(chǔ)的代碼能在移位脈沖的作用下依次左移或右移。如圖5所示,本文采用17個(gè)D觸發(fā)器(DFF)組成一個(gè)移位寄存器,其中第一個(gè)DFF的輸入端接收輸入信號(hào)CON,其余的每個(gè)觸發(fā)器輸入端均與前邊一個(gè)DFF的Q端相連。采用或非門(mén)和與門(mén)等門(mén)電路進(jìn)行邏輯組合,實(shí)現(xiàn)對(duì)移位寄存器產(chǎn)生的序列信號(hào)進(jìn)行時(shí)序控制,確保每個(gè)轉(zhuǎn)換周期的準(zhǔn)確運(yùn)行。

信號(hào)POR作為所有DFF清零端RB的輸入信號(hào),低電平有效。在SAR沒(méi)開(kāi)始工作前,POR為低電平,所有DFF都被清零,則TT和C0~C15都為低電平“0”,TT和C0~C1通過(guò)或非門(mén)產(chǎn)生的T1~T4為高電平“1”,T1~T4通過(guò)與門(mén)進(jìn)而使CON為“1”,這為轉(zhuǎn)換開(kāi)始后TT和C0~C15能夠產(chǎn)生上升沿跳變做好了準(zhǔn)備。TT在SAR ADC中接入到采樣保持模塊,控制采樣模擬信號(hào)的開(kāi)始。當(dāng)POR變?yōu)楦唠娖綍r(shí),SAR開(kāi)始工作,所有DFF可正常存儲(chǔ)數(shù)據(jù),時(shí)鐘信號(hào)clk的第一個(gè)上升沿到達(dá)后,C0=Q0=D0=CON=1,TT=Q1=D1=0,C1=Q2=D2=0,……,如此類推,其余DFF的輸出Q也跟隨輸入端D的狀態(tài)變化,都為0,同時(shí)由于C0的改變,導(dǎo)致CON也改變?yōu)?。第二個(gè)clk上升沿到達(dá)后,C0=Q0=D0=CON=0,TT=Q1=D1=1,C1=Q2=D2=0,……,在隨后的clk上升沿到來(lái)時(shí),移位寄存器都做同樣的動(dòng)作,產(chǎn)生一系列上升沿信號(hào),其中的12個(gè)上升沿信號(hào)C2~C13作為12 bit保持寄存器的序列時(shí)鐘輸入信號(hào)。時(shí)序仿真結(jié)果如圖6所示。

2.3 12 bit保持寄存器的設(shè)計(jì)及仿真

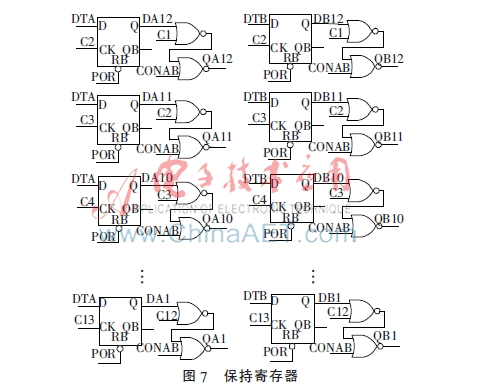

用24個(gè)DFF和或非門(mén)組成保持寄存器,可實(shí)現(xiàn)在序列產(chǎn)生器產(chǎn)生的時(shí)鐘信號(hào)下完成兩路12 bit數(shù)據(jù)的存儲(chǔ),電路結(jié)構(gòu)如圖7所示。兩路轉(zhuǎn)換的時(shí)鐘信號(hào)是相同的,它們同時(shí)動(dòng)作,兩路的工作機(jī)制相同。

保持寄存器兩路的輸入輸出分別為DTA、DTB和DA[12…1]、OA[12…1]、DB[12…1]、OB[12…1],其中OA[12…1]和OB[12…1]為加載到12 bit DAC的12 bit數(shù)字碼,產(chǎn)生相應(yīng)的模擬信號(hào)V0,最高位MSB為OA[12]和OB[12]。DTA、DTB為V0和模擬輸入信號(hào)V1通過(guò)比較器比較后輸出的結(jié)果“0”或“1”。由圖3和圖4可知,CONAB在C0上升沿到達(dá)之后、C15上升沿到達(dá)之前都是低電平0,這樣設(shè)計(jì)可以保證CONAB輸入或非門(mén)后,其輸出由另一個(gè)輸入端口的輸入狀態(tài)決定。C2上升沿沒(méi)到來(lái)之前,DFF還沒(méi)有動(dòng)作,故DA[12…1]=000…0,DB[12…1]=000…0,C1先產(chǎn)生上升沿由“0”跳變?yōu)椤?”,則OA[12]=OB[12]=1,且OA[11…1]=OB[11…1]=[000…0]。接著C2上升沿到達(dá),處理MSB的DFF輸出端DA[12]被置成此刻對(duì)應(yīng)的輸入數(shù)據(jù)DTA(OA[12…1]=OB[12…1]=[100…0],加載到DAC后輸出V0與V1比較的輸出結(jié)果),此時(shí)C1已變?yōu)椤?”,OA[12]由DA[12]決定。若此刻DA[12]=“1”,則OA[12]保留為“1”,若DA[12]=“0”,則OA[12]用“0”取代原來(lái)的“1”,同時(shí)因?yàn)镃2為“1”,使得OA[11]=OB[11]=“1”,新得到OA[12…1]=OB[12…1]=[X100…0]加到DAC轉(zhuǎn)換器的輸入端上,以便下一次的逼近比較。隨后的C3~C13分別跳變的瞬間,保持寄存器都作同樣的動(dòng)作,依次完成從次高位到最低位的逐一比較。

C2~C13只有一次上升沿,故數(shù)碼寄存器可將輸入數(shù)據(jù)DTA鎖存,直到C15跳變,控制CONA的DFF清零端RB為低電平輸入,導(dǎo)致CONAB跟著變?yōu)椤?”,OA[12…1]=000…0,12個(gè)數(shù)位都比較結(jié)束,輸出模數(shù)轉(zhuǎn)換的最終結(jié)果為12 bit串行數(shù)據(jù)DA[12…1]和DB[12…1]。因?yàn)橐莆患拇嫫鞯臅r(shí)鐘輸入信號(hào)由clk和C15通過(guò)“或”邏輯來(lái)決定,當(dāng)C15變?yōu)楦唠娖胶螅莆患拇嫫鞯臅r(shí)鐘信號(hào)將不再滿足上升沿觸發(fā)的條件,直到來(lái)一個(gè)低電平POR將所有DFF清零才使C15=0。圖8為一次轉(zhuǎn)換的仿真結(jié)果(圖(b)緊接著圖(a)右邊),可以看出當(dāng)CONAB變?yōu)楦唠娖胶螅屑拇嫫髑辶悖琌A[12…1]=OB[12…1]=[000…0],為下一次AD轉(zhuǎn)換做好準(zhǔn)備,同時(shí)輸出最終數(shù)據(jù)DA[12…1]和DB[12…1],并鎖存。

3 版圖設(shè)計(jì)及在SAR ADC中的驗(yàn)證

基于CSMC 0.5 m DPTM工藝,采用手工布局布線的方式代替參考文獻(xiàn)[10]中的EDA自動(dòng)布局布方式,實(shí)現(xiàn)SAR版圖如圖9所示,整體優(yōu)化到最緊湊,很好地節(jié)省了版圖面積,降低了成本,面積約為290 m×110 m。

將本文設(shè)計(jì)的SAR接入到SAR ADC整體電路中,輸入兩路模擬信號(hào)進(jìn)行仿真,A路輸入模擬信號(hào)2.505 V,B路輸入模擬信號(hào)2.635 V,5 V單電源供電,得到仿真結(jié)果如圖10所示。由結(jié)果可知,TT上升沿到達(dá)時(shí),A路B路開(kāi)始采樣保持,A路為2.5 050 326 V,B路為 2.6 352 034 V,輸出AD轉(zhuǎn)換的最終數(shù)字信號(hào)DA[12…1]=[100000000101],DB[12…1]=[100001101111],將這兩個(gè)數(shù)字量轉(zhuǎn)換后分別為2.5 061 035 V和2.6 354 980 V,都滿足誤差要求,表明所設(shè)計(jì)的SAR能夠準(zhǔn)確實(shí)現(xiàn)逐次逼近比較的功能。

4 結(jié)論

根據(jù)SAR ADC的工作機(jī)理,采用全定制設(shè)計(jì)方法設(shè)計(jì)了一個(gè)可同時(shí)完成兩路12 bit數(shù)據(jù)信號(hào)的逐位逼近寄存器,仿真驗(yàn)證結(jié)果表明,該SAR滿足SAR ADC正常運(yùn)轉(zhuǎn)所需要的時(shí)序要求,并解決了采用邏輯綜合設(shè)計(jì)方法帶來(lái)的電路單元冗雜、功耗大、開(kāi)關(guān)噪聲大和電路面積大等問(wèn)題;通過(guò)Cadence軟件完成原理圖和版圖的設(shè)計(jì),將其應(yīng)用到SAR ADC的整體電路中進(jìn)行仿真,結(jié)果表明設(shè)計(jì)達(dá)到要求。該設(shè)計(jì)在需要同時(shí)處理多位數(shù)據(jù)的模數(shù)轉(zhuǎn)換應(yīng)用中具有重要的實(shí)際應(yīng)用價(jià)值。

參考文獻(xiàn)

[1] 孫彤,李冬梅.逐次逼近A/C轉(zhuǎn)換器綜述[J].微電子學(xué),2007,37(4):523-547.

[2] 王俊博.基于CMOS工藝10位模數(shù)轉(zhuǎn)換電路的設(shè)計(jì)[D].哈爾濱:黑龍江大學(xué),2010.

[3] 周文婷.數(shù)字CMOS工藝下10位580 kSps逐次逼近型模數(shù)轉(zhuǎn)換器設(shè)計(jì)[D].上海:上海交通大學(xué),2010.

[4] Ye Yafei, Liu Liyuan, Li Fule, et al. An 8-bit 1 MHz successive approximation register(SAR) A/D with 7.98 ENOB[J]. Anti-Counterfeiting, Security and Identification(ASID), IEEE International Conference, 2011:139-142.

[5] 張少真,李哲英.應(yīng)用于SAR ADC中逐次逼近寄存器的設(shè)計(jì)[J].北京聯(lián)合大學(xué)學(xué)報(bào)(自然科學(xué)版),2011,25(2):15-19.

[6] 張紅,高煒祺,張正璠,等.一種基于新型寄存器結(jié)構(gòu)的逐次逼近A/D轉(zhuǎn)換器[J].微電子學(xué),2006,36(3):337-343.

[7] 李偉華.VLSI設(shè)計(jì)基礎(chǔ)[M].北京:電子工業(yè)出版社,2010.

[8] 閻石.數(shù)字電子技術(shù)基礎(chǔ)[M].北京:高等教育出版社,2006.

[9] 小林芳直.數(shù)字邏輯電路的ASIC設(shè)計(jì)[M].蔣民,譯.北京:科學(xué)出版社,2004.

[10] 孫磊.一種低功耗逐次逼近型模數(shù)轉(zhuǎn)換器的研究與設(shè)計(jì)[D].上海:上海交通大學(xué),2010.