盡管當(dāng)前趨勢全部集中一個方向——設(shè)計者需要使用A/D轉(zhuǎn)換器時通常選定一個集成的A/D轉(zhuǎn)換器(ADC)。大多數(shù)工程師并沒有意識到還有降低ADC性價比的其它替代方案。而模擬比較器、D/A轉(zhuǎn)換器(DAC)和信號處理一起恰好就是構(gòu)成逐次逼近ADC的核心電路。

在某些特定領(lǐng)域,分立比較器/DAC的使用非常普遍。自動測試設(shè)備、核脈沖反應(yīng)堆高度監(jiān)測器以及自動化時域反射計等,通常都采用這種技術(shù),DAC用于驅(qū)動比較器的一個輸入,另一個輸入由被監(jiān)測信號驅(qū)動。接下來是通用測試問題以及特定方法的選擇,事實上,此時采用比較器/DAC組合比采用現(xiàn)成的ADC更受歡迎。

瞬態(tài)電壓分析

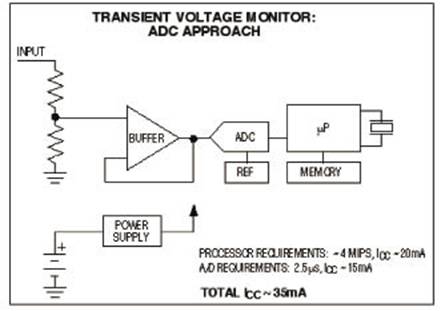

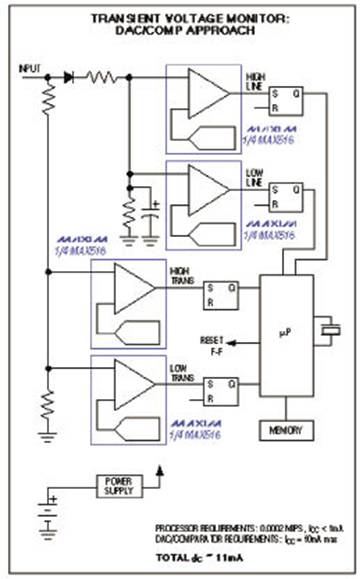

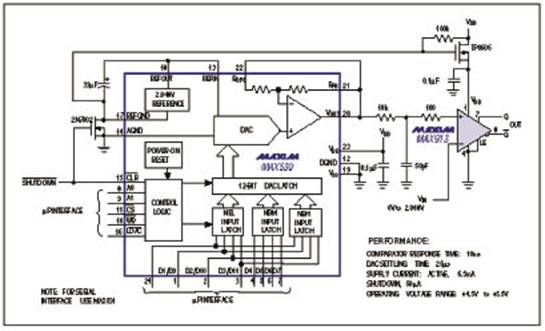

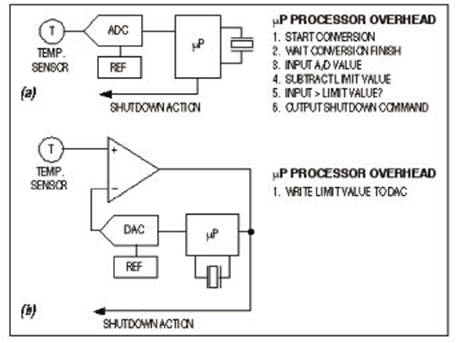

捕獲快速幅度變化事件(瞬態(tài))的“強(qiáng)力”技術(shù)就是采用處理器支持的高速ADC和RAM對其進(jìn)行簡單量化(圖1)。單觸發(fā)事件可能必須采用這種方法,因為需要獲取瞬態(tài)細(xì)節(jié)。然而,如果瞬態(tài)是重復(fù)性的,則可采用DAC/比較器的方法測量它們的峰值幅度及其它特性(圖2)。

比較器的一個輸入引腳由DAC設(shè)置判定電平,瞬態(tài)信號施加到另一個輸入。通過調(diào)整DAC輸出可確定峰值瞬態(tài)幅度。超越門限時,采用數(shù)字鎖存捕獲比較器的輸出響應(yīng)。僅需要比較器輸入支持瞬態(tài)帶寬,任意長的DAC輸出建立時間并不會影響測量精度。這樣,在模擬域可用低成本DAC和比較器代替昂貴的ADC。

圖1 采用“強(qiáng)力” 法進(jìn)行瞬態(tài)分析,ADC電路耗電大且價格昂貴

圖2 如果圖1應(yīng)用可接受對幅度進(jìn)行重復(fù)測量,用DAC/比較器組合替代ADC可省電并降低成本。

需注意的是,在監(jiān)視模擬電壓時必須考慮容限。許多自診斷設(shè)備監(jiān)視系統(tǒng)電壓、溫度以及其它模擬量,容限值在軟件中設(shè)置。然而,如果這種比較由比較器實現(xiàn),設(shè)置值由DAC提供,這樣可減輕處理器負(fù)荷,因為只需要讀取一位來表示超限狀態(tài)。

這種技術(shù)(模擬域比較)與ADC技術(shù)(數(shù)字域比較)具有相同精度,對于一個設(shè)置點時,可通過簡單比較實現(xiàn),為什么還要對整個值進(jìn)行量化?必須提及的一種情況是:如果與幾個設(shè)置點進(jìn)行比較時,例如報警上限/下限和關(guān)斷的下限/上限電平,可選擇ADC,否則需要4路DAC和4個比較器。

由DAC構(gòu)建簡單的ADC

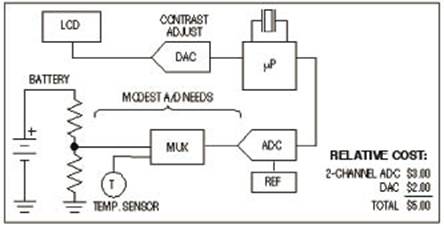

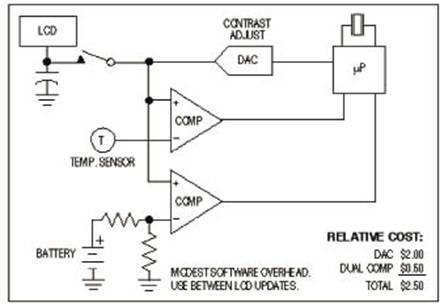

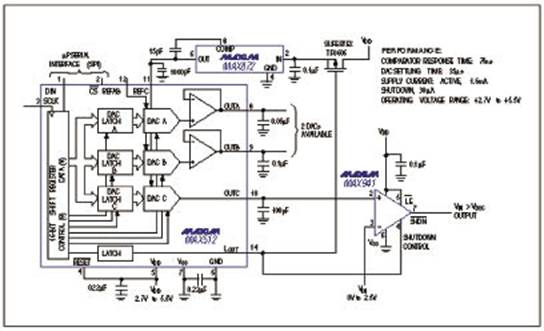

便攜式儀器受成本和尺寸限制,有些情況下可以利用DAC實現(xiàn)A/D轉(zhuǎn)換功能。例如,蜂窩電話和醫(yī)療電子通常采用DAC調(diào)整LCD對比度電壓(圖3)。有時可通過簡單添加一個比較器和開關(guān),監(jiān)視溫度或電池電壓(如上所述)。那么現(xiàn)有DAC可執(zhí)行兩種任務(wù),在DAC執(zhí)行模擬至數(shù)字轉(zhuǎn)換時關(guān)閉顯示器。作為另一種替代方案,由模擬開關(guān)和電容構(gòu)成的簡單采樣/保持電路(圖4)可在A/D轉(zhuǎn)換期間維持LCD的對比度電壓。

圖3 該電路常見于便攜儀器

圖4 對圖3增加兩個比較器,由DAC實現(xiàn)ADC功能,節(jié)省成本。

另外一種方法就是用一個低成本雙路DAC替代現(xiàn)有單路DAC。雙路DAC中的一路用于產(chǎn)生LCD對比度電壓,另一路用于構(gòu)成ADC。無論單路還是雙路,都需要DAC和比較器支持快速、驅(qū)動DAC的簡單程序,以及對比較器采樣來實現(xiàn)逐次逼近。

設(shè)計考慮

DAC和比較器的結(jié)合非常簡單。信號作用到比較器的同相輸入端,DAC提供的數(shù)字可編程門限作用到反相輸入端。只要信號比門限值大,比較器就會產(chǎn)生邏輯高電平輸出。但在使用時必須注意幾個方面:

為確保精確的門限電平,考慮到比較器的輸入偏置電流以及比例網(wǎng)絡(luò),DAC的直流輸出阻抗應(yīng)很小。在超低功耗電路中更應(yīng)注意,DAC的輸出阻抗可能高達(dá)10kΩ。

DAC的另一個要求是低交流輸出阻抗。否則,比較器輸出的高速數(shù)字信號的壓擺率經(jīng)過布線寄生電容耦合,將產(chǎn)生輸入瞬態(tài)變化,導(dǎo)致自激并降低精度。如果允許犧牲一定的建立時間,可在比較器輸入端增加一個旁路電容來降低DAC的交流輸出阻抗。DAC輸出放大器的大電容負(fù)載可導(dǎo)致不穩(wěn)定或振蕩,但這個問題可在DAC輸出串聯(lián)一個電阻加以修正。

比較器的主要問題是滯回。大多數(shù)比較器電路帶有滯回,以防止噪聲和振蕩,但使用滯回時必須謹(jǐn)慎——它會造成門限值隨輸出而改變。如果系統(tǒng)可對受輸出狀態(tài)影響的滯回進(jìn)行補償,可以接受這種配置;否則,應(yīng)當(dāng)避免滯回。

如果采用的比較器具有內(nèi)部滯回并且不能禁止,可確保DAC輸出總是在相同方向逼近比較器門限,這樣可消除負(fù)面影響。通過在每位測試完成后將DAC設(shè)置為零,便于達(dá)到這一目的;例如,在本文最后列出的偽代碼后增加一行。

另一選擇是,通過增加一個小電容反饋也可消除滯回,這會加速比較器在線性工作區(qū)的轉(zhuǎn)換。或者,增加一個輸出觸發(fā)器或鎖存器,在給定時刻捕獲比較器輸出狀態(tài)。

當(dāng)前比較器都能夠很好地處理擺率受限的輸入信號。例如,Maxim公司的MAX913和MAX912在這方面尤其有效,因為它們在線性工作區(qū)能夠確保穩(wěn)定。圖5列舉了MAX913在高速、12位應(yīng)用中的性能。圖6電路(超低功耗8位轉(zhuǎn)換器)在不使用時可將其關(guān)閉以節(jié)省能量。

圖5 由于比較器在其線性工作區(qū)保持穩(wěn)定,該高速、12位幅度采集器可處理低速輸入電壓。

圖6 該低電壓、8位數(shù)據(jù)采集器替代ADC具有幾個優(yōu)勢:低成本、低功耗、以及采樣間隔期間關(guān)斷功能。

DAC/比較器組合IC

Maxim提供3款單芯片器件可大大簡化設(shè)計,這些芯片組合了比較器和DAC。每款器件都非常適合本文應(yīng)用及其它多種應(yīng)用。

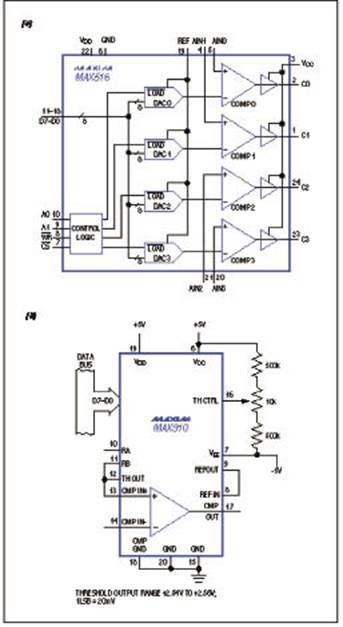

例如,MAX516是一款4通道器件,具有亞微秒速度,非常適合多種中等速度、多通道應(yīng)用(圖7a)。

MAX910是單通道、高速、TTL輸出DAC/比較器,具有8ns傳輸延遲(圖7b)。類似器件(MAX911)具有更高速度——ECL互補輸出、4ns傳輸延遲。

圖7 Maxim 8位DAC/比較器IC包括4通道MAX516(a)、高速、TTL兼容MAX910(b)、以及ECL兼容MAX911(未列出)

逐次逼近

逐次逼近采用天平和一系列用于確定物體重量的二進(jìn)制權(quán)重(權(quán)重相對值為1、2、4、8、16等)的方式很容易說明。確定一個未知重量的最快方法(逐次逼近),首先,將未知重量與最大權(quán)重進(jìn)行比較。根據(jù)天平指示,要么移除該重量,要么增加下一個最大重量,按這種方式一直到最小的權(quán)重。物體的重量就是天平盤上剩余權(quán)重的總和。

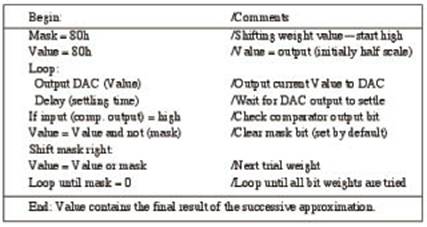

在逐次逼近ADC中,內(nèi)部DAC的位模擬系列二進(jìn)制重量,比較器輸出模擬天平指示。驅(qū)動權(quán)位處理的邏輯保存在封裝好的ADC的逐次逼近寄存器(SAR)或者控制DAC/比較器電路的處理器軟件子程序,該子程序可由不到20行的代碼來實現(xiàn)(表1)。

應(yīng)用

本章節(jié)列舉了DAC/比較器架構(gòu)和集成ADC相比所具備的優(yōu)勢。所討論的應(yīng)用電路既常見又簡單,也存在一些共性問題。

首先,考慮采用低成本方法實現(xiàn)電力線電壓跌落、浪涌以及瞬態(tài)檢測和故障記錄。理想的設(shè)計是采用墻上設(shè)備監(jiān)測電力線異常,并將每次異常發(fā)生的時間記錄到RAM中(電壓跌落和浪涌的持續(xù)時間可以從幾毫秒到幾小時;瞬態(tài)可能短至10微秒)。監(jiān)視器必須記錄電力線完全失效的持續(xù)時間,因此,監(jiān)視器應(yīng)當(dāng)由電池供電。

傳統(tǒng)解決方案是采用控制器和ADC。由于轉(zhuǎn)換器連續(xù)對電力線電壓采樣,控制器需將每次采樣值與軟件中用戶設(shè)定的限制進(jìn)行比較,并將任何超出規(guī)定的狀態(tài)記錄到RAM。由于系統(tǒng)必須能夠追蹤到短至10µs的瞬態(tài)情況,ADC采樣間隔必須相當(dāng)短——保守估算時間可以長達(dá)2.5µs。因此,控制器必須以1/2.5µs = 400ksps的速率進(jìn)行采樣處理。

如果軟件比較具有高效編碼并且ADC無需處理器干預(yù),系統(tǒng)每次采樣可執(zhí)行少于10條指令,這就要求處理器具有4MIPS的能力。這種執(zhí)行能力并不適合采用電池供電(圖1)。需要考慮用模擬方法對輸入瞬態(tài)偏離進(jìn)行響應(yīng),用以替代連續(xù)跟蹤方案。

在這種情況下,DAC/比較器替代方案提供了幾個明顯優(yōu)勢。需要4個DAC和4個比較器(或一片MAX516),后面連接一個4路設(shè)置/復(fù)位觸發(fā)器。一組DAC/比較器/FF監(jiān)測高瞬態(tài)電壓,一組監(jiān)測低瞬態(tài)電壓,一組用于監(jiān)測電網(wǎng)跌落,一組用于監(jiān)測浪涌(圖2)。瞬態(tài)電壓直接耦合到比較器,連接到電壓跌落和浪涌監(jiān)測比較器的輸入首先要進(jìn)行整流和濾波,以獲得電網(wǎng)電壓的平均值。可在軟件中調(diào)整到合適的rms。

系統(tǒng)每T秒進(jìn)行采樣并對觸發(fā)器復(fù)位,此處T為瞬態(tài)記錄時間分辨率(也許為60s)。高、低瞬態(tài)電平DAC用于設(shè)置所要求的門限。電壓跌落和浪涌DAC在每T秒間隔后進(jìn)行調(diào)整,采用逐次逼近技術(shù)產(chǎn)生高、低門限,以跟蹤目前平均值。

假設(shè)執(zhí)行逐次逼近以及其它任務(wù)的子程序具有1000條指令(保守估計),對于T=60s,CPU平均每秒執(zhí)行17條指令。執(zhí)行速率是0.00002MIPS,非常適合低功耗系統(tǒng),遠(yuǎn)遠(yuǎn)低于ADC方案的4MIPS。為進(jìn)一步降低功耗,控制器可在大部分時間內(nèi)處于“休眠”,僅在處理電力線異常時喚醒。將電壓比較從軟件方式轉(zhuǎn)換為模擬硬件方式,該電路大大降低了功耗、設(shè)計復(fù)雜性以及成本。

較低的故障檢測和診斷維護(hù)成本

打印頭控制、車輛控制以及許多其它機(jī)電應(yīng)用,需嚴(yán)格監(jiān)視內(nèi)部電壓和溫度以確定何時更換工作模式。極端情況下,這種反饋可使系統(tǒng)避免全部關(guān)斷自毀。例如,在必要時步進(jìn)電機(jī)控制器必須調(diào)整輸出MOSFET的柵極驅(qū)動以避免線性工作時消耗過多功率。

監(jiān)測這些問題的傳統(tǒng)方法是采用ADC(圖8a)。處理器控制ADC進(jìn)行周期性測量,與控制處理保持時間常數(shù)一致。然后對結(jié)果的量化值進(jìn)行縮放后與軟件中的門限進(jìn)行比較。如果超出范圍,可觸發(fā)糾正動作或者全部關(guān)斷系統(tǒng)。

另外一種方法是采用DAC/比較器組合(圖8b)。靜態(tài)DAC輸出建立關(guān)斷門限或比較器觸發(fā)值。當(dāng)溫度變化造成比較器觸發(fā),比較器會對處理器發(fā)出中斷來啟動糾正動作。必要時,處理器還可以通過啟動基于軟件的逐次逼近程序來確定極限溫度值。

表1 逐次逼近偽代碼

圖8 在這種情況下,用DAC和比較器(b)替換ADC(a)可降低系統(tǒng)成本、響應(yīng)時間以及軟件開銷

另一方面,為支持ADC,處理器在跳轉(zhuǎn)到關(guān)斷子程序之前必須輪詢ADC、輸入采樣值并與先前設(shè)定值進(jìn)行比較。這樣,DAC/比較器不僅節(jié)約成本,而且提供了比采用ADC的更快響應(yīng);同時還減小了處理器開銷。

時域反射計

最后,低成本、低功耗DAC/比較器組合(相對于ADC)在便攜式時域反射計(TDR)中非常實用,后者是一種用于檢測電纜的不連續(xù)性并可測量中間傳輸長度的儀器。廉價的便攜式TDR隨著網(wǎng)絡(luò)電纜的增加變得非常普遍。

TDR工作原理類似于雷達(dá),沿著線纜發(fā)送一個主脈沖并監(jiān)測由開路、短路、或者其它電纜阻抗不連續(xù)產(chǎn)生的反射。發(fā)射脈沖及其反射波傳輸延時間隔大約為每英尺3.3ns,假設(shè)線傳輸速率為0.6c(光速的十分之六)。那么,在電子學(xué)上10ns時間分辨率可分辨出大約3英尺距離的不連續(xù)性。

接收到的脈沖幅度和發(fā)送脈沖幅度的比用于計算反射系數(shù)。知道反射系數(shù)和電纜阻抗就可以計算不連續(xù)阻抗,從這些信息可推斷出不連續(xù)的原因。同軸電纜在反射回路上對脈沖的衰減使其變得復(fù)雜,因此,軟件必須對此進(jìn)行補償,通常根據(jù)測量距離施加一個幅度修正。

本應(yīng)用中的ADC必須每個5ns轉(zhuǎn)換一次(200Msps)。盡管廠商可以提供這種ADC,但價格非常昂貴,而且功耗大,通常不適合便攜式應(yīng)用。

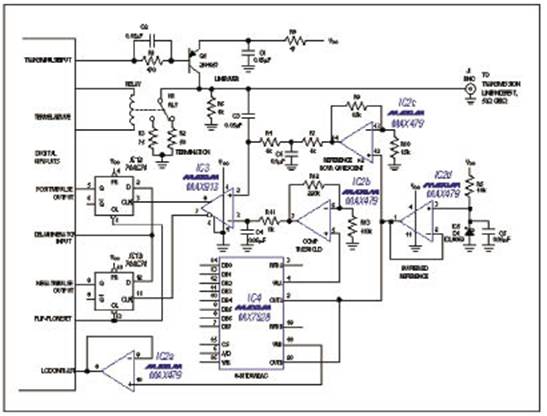

實際應(yīng)用中的手持式TDR模擬前端(圖9)能夠說明上述觀點。為了便于說明,這里沒有包括數(shù)字電路。盡管簡單并且沒有特殊元件,該電路仍具有很好性能。能夠可靠地測量端接阻抗并且對于500英尺長的電纜具有5%測量精度。可測量長達(dá)2000英尺的開路或短路故障。重要的是,系統(tǒng)(包括顯示和數(shù)字電路)可在9V堿性電池下工作長達(dá)20小時。

圖9 該時域反射計的模擬部分采用DAC/比較器代替ADC

圖9中比較器(IC3)采用單電源供電、地電位檢測以及僅10ns傳輸延遲。DAC(IC4)為雙通道器件,一方面用于脈沖高度測量,另一方面驅(qū)動LCD對比度控制(如圖3)。注意DAC為反向驅(qū)動;電流輸出端連接在一起由經(jīng)過緩沖的電壓基準(zhǔn)驅(qū)動,基準(zhǔn)輸入作為電壓輸出(每路帶有一個外部放大器緩沖)。

利用簡單的脈沖單穩(wěn)態(tài)電路(沒有列出)驅(qū)動Q1基極,利用正向、持續(xù)時間為10ns的脈沖依次驅(qū)動電纜。電纜的所有反射通過C3耦合到比較器。

IC5為1.2V輸出帶隙基準(zhǔn),由放大器IC2d緩沖,為IC4雙路DAC提供基準(zhǔn)電壓。該基準(zhǔn)電壓被IC2c兩倍增益放大器放大后,為比較器同相輸入提供2.5V直流電平。DAC A在比較器反相輸入端施加一個0至3.8V電壓。高于2.5V的電平用來判斷正向脈沖高度,低于2.5V的電平用來判斷負(fù)向脈沖幅度。

每個輸入到傳輸線的脈沖還經(jīng)過了數(shù)字電路可變延遲線,該延遲線是由計數(shù)器控制的20ns延遲單元串接而成。來自數(shù)字部分經(jīng)過延遲的脈沖驅(qū)動兩個觸發(fā)器(IC1a和IC1b)的D輸入端,觸發(fā)器由比較器互補TTL輸出輪流觸發(fā)。這樣,時間測量取決于返回脈沖和通過延遲線脈沖的競爭:如果D輸入比時鐘變化到來得早,觸發(fā)器輸出為高;否則,輸出為低。

測量時,將DAC輸出設(shè)置為最低值并重復(fù)調(diào)整延遲,直到觸發(fā)器輸出保持為零,讀取計數(shù)器。同樣,測量返回脈沖高度時,重復(fù)調(diào)整DAC輸出直到觸發(fā)器輸出保持為零,然后讀取DAC。注意,兩個觸發(fā)器需要捕獲正脈沖和負(fù)脈沖的前沿。前沿是指正脈沖的上升沿和負(fù)脈沖的下降沿;如果兩個脈沖施加到一個觸發(fā)器,脈沖寬度可能產(chǎn)生人們所不期望的延遲。