文獻標識碼: A

文章編號: 0258-7998(2015)02-0059-02

0 引言

FIR濾波器具有嚴格的線性相頻特性,同時又可保證任意幅頻特性。而這個特點使FIR濾波器在數(shù)據(jù)傳輸、圖像處理和識別、語音處理和通信系統(tǒng)中具有廣泛的應(yīng)用。除此之外,F(xiàn)IR濾波器除0以外沒有其他的極點,所以整個濾波系統(tǒng)是相對穩(wěn)定的,不存在不穩(wěn)定的問題,這是FIR區(qū)別于IIR的本質(zhì)原因,而FIR在傳輸數(shù)據(jù)時存在色散。

本文只討論FIR濾波器的設(shè)計方法。基于DA算法的濾波器有效解決了MAC結(jié)構(gòu)的不足,但是隨著濾波器的階數(shù)增加,查找表的規(guī)模呈指數(shù)增加,再設(shè)計高階濾波器時普通DA算法甚至難以實現(xiàn)。本文提出了一種優(yōu)化的DA算法來克服一般DA算法在設(shè)計高階濾波器時的缺陷,并用Verilog HDL語言在FPGA上實現(xiàn)[1]。

1 線性相位FIR濾波器的結(jié)構(gòu)

如果FIR中的h(n)為實數(shù),并符合下列條件其中的一種:

偶對稱:h(n)=h(N-1-n)

奇對稱:h(n)=-h(N-1-n)

稱其具有線性相位結(jié)構(gòu)。

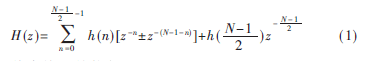

當N為奇數(shù)時,其系統(tǒng)函數(shù)為[2]:

其直接型結(jié)構(gòu)如圖1所示。

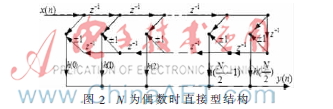

當N為偶數(shù)時,其系統(tǒng)函數(shù)為:

其直接型結(jié)構(gòu)如圖2所示。

2 分布式算法

2.1 分布式算法基礎(chǔ)

DA算法是基于查找表結(jié)構(gòu)的,其詳細公式解析如下[3]:

重新分配求和的順序,其結(jié)果如下:

y=c[0]( xB-1[0]2B-1+ xB-2[0]2B-2+…+ x0[0]20)

+c[1]( xB-1[1]2B-1+ xB-2[1]2B-2+…+ x0[1]20)+…

+c[N-1](xB-1[N-1]2B-1+xB-2[N-1]2B-2+…+x0[N-1]20)

=(c[0] xB-1[0]+c[1] xB-1[1]+…+c[N-1]xB-1[N-1])2B-1

+c[0] xB-2[0]+c[1] xB-2[1]+…+c[N-1]xB-2[N-1])2B-2

+…+(c[0] x0[0]+c[1] x0[1]+…+c[N-1] x0[N-1])20

(6)

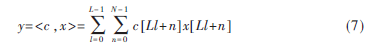

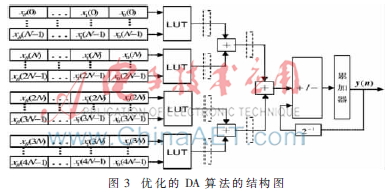

2.2 分布式算法的優(yōu)化

假如N的數(shù)量增加,一個單一的LUT無法執(zhí)行全字,就能夠利用部分表并先將結(jié)果相加。其原理為:假定長度為LN的內(nèi)積 ,那么可以用一個DA體系結(jié)構(gòu)實現(xiàn)它:

,那么可以用一個DA體系結(jié)構(gòu)實現(xiàn)它:

表的規(guī)模從一個24N B的LUT減少4個2N B表。優(yōu)化的DA算法的結(jié)構(gòu)圖如圖3所示。

3 基于FPGA的FIR低通濾波器的設(shè)計

3.1 基于FPGA的FIR設(shè)計流程

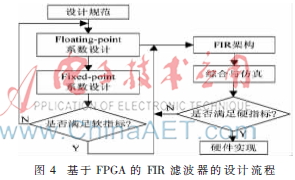

本文設(shè)計的FIR濾波器的流程如圖4所示,主要分為系數(shù)提取和FPGA完成[4]。

3.2 FIR濾波器的MATLAB設(shè)計

本文設(shè)計濾波器主要參數(shù)為阻帶最小衰減為30 dB,通帶波紋小于0.5 dB,截止頻率為0.4。為此設(shè)計了18階的FIR線性相位低通濾波器,采用窗函數(shù)中的凱澤窗來設(shè)計。根據(jù)凱澤窗參數(shù)?對濾波器的性能的影響,來滿足條件。由這些技術(shù)指標可通過MATLAB提供的濾波器設(shè)計工具箱FDAtool來仿真設(shè)計濾波器,從而提取濾波器的系數(shù)[5]。

由于提取出來的系數(shù)是浮點型,而FPGA只能處理定點型數(shù)據(jù),所以需要把提取出來的系數(shù)進行量化,在該設(shè)計方案中將系數(shù)擴大1 024倍,即210。再通過編碼轉(zhuǎn)化為二進制形式。通過FDAtool工具提取出的數(shù)據(jù)及其量化結(jié)果如下:

h(0)=h(17)=-0.014 361 548 558 709 025,

h(1)=h(16)

=0.000 000 000 000 000 007 952 163 344 493 980 7,

h(2)=h(15)=0.028 618 979 697 780 135,

h(3)=h(14)=0.024 250 698 402 580 449,

h(4)=h(13)=-0.033 323 873 349 896 04,

h(5)=h(12)= -0.075 849 033 020 568 446,

h(6)=h(11)

=0.000 000 000 000 000 014 598 689 803 221 391,

h(7)=h(10)=0.197 209 967 107 277 67,

h(8)=h(9)=0.373 454 809 721 535 27。

其量化結(jié)果分別為:-15,0,29,25,-34,-78,0,202,

382。十六進制補碼分別為fff1,0000,001d,0019,ffde,ffb2,0000,00ca,017e。

3.3 線性相位FIR濾波器的FPGA實現(xiàn)

本文采用模塊化思想,由一個主時鐘控制各個子時鐘,全部模塊分別為并串轉(zhuǎn)換、延時與預(yù)求和、移位累加、查找表采用3個分割查表結(jié)構(gòu)和求部分和的模塊[6]。

為了驗證電路能否連續(xù)正確運行,本文連續(xù)隨機輸入序列0、127、100、57、26、5、20、26、79、8、12、49、35、102、99、125、63、82在Modelsim工具上進行仿真,其結(jié)果如圖5所示。

仿真結(jié)果與MATLAB工具計算的理論值相比較,其Modelsim部分仿真結(jié)果如下:0、-2、-1、3、6、0、-11、-9、

19、19、66。MATLAB理論計算結(jié)果對應(yīng)為:0、-1.823 9、-1.436 2、2.816 0、5.568 3、-0.247 6、-11.1261、-9.084 2、

19.414 9、66.125 3。通過仿真與MATLAB計算理論結(jié)果進行比較,理論值與仿真結(jié)果存在誤差但是誤差在允許的范圍內(nèi),誤差主要是因為量化時產(chǎn)生的。

4 結(jié)束語

本文提出的優(yōu)化DA算法本質(zhì)是提出對查找表的優(yōu)化,事實證明濾波器階數(shù)越高,此優(yōu)化算法的作用越明顯,而且可以節(jié)省內(nèi)部邏輯資源。最后通過硬件實現(xiàn),結(jié)果與理論值相比較,設(shè)計符合預(yù)期。

參考文獻

[1] 程佩青.數(shù)字信號處理[M].北京:清華大學出版社,2001.

[2] Meyer-Baese U(美).數(shù)字信號處理的FPGA實現(xiàn)[M].北京:清華大學出版社,2011.

[3] 杜勇.數(shù)字濾波器的MATLAB與FPGA實現(xiàn)[M].北京:電子工業(yè)出版社,2012.

[4] 高耀紅.基于FPGA的FIR低通濾波器[D].長沙:湖南大學,2012.

[5] 劉朋全.基于FPGA的FIR數(shù)字濾波器的設(shè)計和實現(xiàn)[D].西安:西北工業(yè)大學,2006.

[6] 夏宇聞.數(shù)字系統(tǒng)設(shè)計教程[M].北京:北京航空航天大學出版社,2008.