文獻(xiàn)標(biāo)識(shí)碼: A

文章編號(hào): 0258-7998(2015)03-0048-03

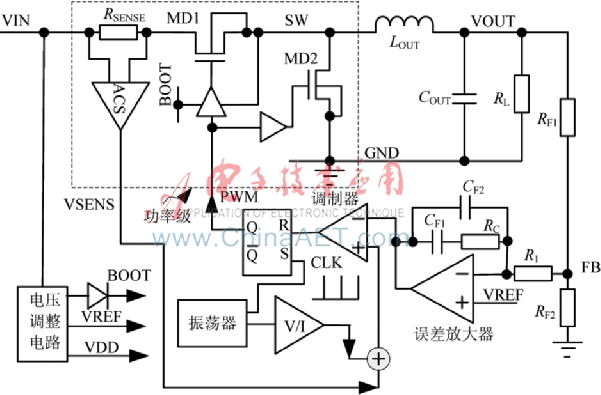

當(dāng)前,數(shù)字多媒體、視頻廣播設(shè)備、個(gè)人導(dǎo)航設(shè)備(PND)、車載電源設(shè)備的使用越來越廣泛, 為這些設(shè)備提供電源管理,常需要具有高壓大電流高轉(zhuǎn)換率效的DC-DC轉(zhuǎn)換器。為了減小設(shè)備體積和重量,電源模塊必須最小化,因此,實(shí)現(xiàn)轉(zhuǎn)換器的高轉(zhuǎn)換效率以及高集成度成為一種趨勢(shì)[1-2]。考慮到電壓控制模式和非同步轉(zhuǎn)換器的一些缺點(diǎn),更多的系統(tǒng)選擇使用同步電流模式DC-DC轉(zhuǎn)換器;圖1為典型電流模同步BUCK轉(zhuǎn)換器的電路框圖,圖中陰影部分為轉(zhuǎn)換器的功率級(jí),而電流控制模式BUCK DC-DC轉(zhuǎn)換器中功率級(jí)的設(shè)計(jì)是最重要的功能模塊之一,亦是轉(zhuǎn)換器設(shè)計(jì)的難點(diǎn)所在,原因在于:功率級(jí)中作為開關(guān)的功率晶體管導(dǎo)通電阻會(huì)影響系統(tǒng)轉(zhuǎn)換器的效率,在大負(fù)載電流條件下,功率開關(guān)晶體管的導(dǎo)通電阻還會(huì)影響芯片的熱設(shè)計(jì),一般來講,功率開關(guān)的導(dǎo)通電阻與其寬長(zhǎng)比成反比,但大尺寸器件會(huì)導(dǎo)致更大的芯片面積,增加芯片的成本,缺少市場(chǎng)的競(jìng)爭(zhēng)力,怎樣能夠在減小導(dǎo)通電阻和芯片面積之間找到合適的折中點(diǎn)是功率晶體管設(shè)計(jì)的關(guān)鍵;其次,功率晶體管在版圖設(shè)計(jì)時(shí)的寄生效應(yīng)也會(huì)影響轉(zhuǎn)換器的性能,功率晶體管的版圖優(yōu)化是功率級(jí)設(shè)計(jì)的一個(gè)重要部分;最后,電流模轉(zhuǎn)換器需要對(duì)電感電流進(jìn)行檢測(cè),設(shè)計(jì)合適的低功耗電感電流檢測(cè)電路亦是功率級(jí)設(shè)計(jì)的難點(diǎn)。

基于上面的考慮,本文將以電流模式控制同步降壓型DC-DC轉(zhuǎn)換器為例,設(shè)計(jì)輸入電壓最大為18 V、典型輸出電壓為5 V、能夠提供3 A負(fù)載電流的功率級(jí)。

1 同步功率晶體管設(shè)計(jì)

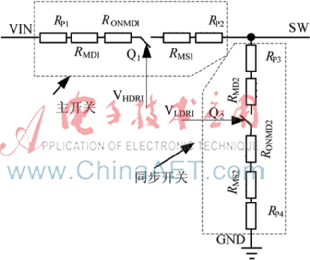

對(duì)于單片高壓大電流集成DC-DC轉(zhuǎn)換器,功率級(jí)設(shè)計(jì)極具挑戰(zhàn)性,特別是高壓功率開關(guān)采用LDMOS晶體管,在大電流下需要考慮以下幾個(gè)方面: DMOS晶體管會(huì)寄生雙極性晶體管,當(dāng)晶體管流過一定的電流,晶體管的漏極和源極電壓會(huì)增加到擊穿電壓,然后漏源電壓將回跳到一定的低值[3-4];其次,在負(fù)載電流比較大時(shí),芯片封裝時(shí)引線產(chǎn)生的寄生電阻[5]將不能忽略不計(jì),如圖2所示,RP1~RP4為芯片封裝引線產(chǎn)生的寄生電阻,為了能夠減小其寄生電阻,在芯片封裝時(shí),PAD與封裝管腳之間引線要避免過長(zhǎng);圖2中,RONMD1為主功率開關(guān)導(dǎo)通電阻,RONMD2為同步開關(guān)的導(dǎo)通電阻; Q1和Q2是由驅(qū)動(dòng)電路控制的理想開關(guān)。

主開關(guān)的等效直流導(dǎo)通電阻RHS如下式所示:

RHS=RP1+RMD1+RONMD1+RMS1+RP2(1)

其中:RMD1和RMS1分別為主開關(guān)功率晶體管版圖設(shè)計(jì)時(shí)漏極和源極金屬連線產(chǎn)生的寄生電阻,該電阻主要由金屬連線的物理設(shè)計(jì)決定。

同步開關(guān)的等效直流導(dǎo)通電阻RLS如下式所示:

RLS=RP3+RMD2+RONMD2+RMS2+RP4(2)

其中:RMD2和RMS2分別為同步開關(guān)功率晶體管版圖設(shè)計(jì)時(shí)漏極和源極金屬連線產(chǎn)生的寄生電阻,該電阻主要由晶體管的物理設(shè)計(jì)決定。

主功率開關(guān)和同步開關(guān)晶體管一般選用N溝道LDMOS晶體管,原因在于N溝道LDMOS晶體管的電子遷移率大于P溝道LDMOS晶體管空穴遷移率,對(duì)于相同大小的導(dǎo)通電阻,LDNMOS晶體管的面積僅為L(zhǎng)DPMOS晶體管面積的1/2~1/3[3],本文設(shè)計(jì)主開關(guān)和同步開關(guān)等效直流導(dǎo)通電阻RHS和RLS約為88 m?贅。

2 電感電流檢測(cè)電路

電流模式DC-DC轉(zhuǎn)換器中,電感電流的檢測(cè)是智能功率芯片非常重要的功能之一,因此也衍生了多種電感電流檢測(cè)的方式[6]。

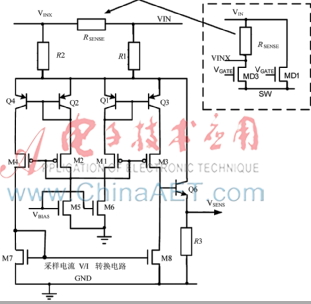

本文對(duì)電感電流檢測(cè)的方式采用間接檢測(cè)方式,圖3給出電路結(jié)構(gòu),當(dāng)主開關(guān)功率(MD1)晶體管導(dǎo)通時(shí),MD1的漏極電流等于電感流過的電流,為了避免直接檢測(cè)MD1電流會(huì)導(dǎo)致消耗更大的功耗,不利于系統(tǒng)的效率提高,本設(shè)計(jì)采用等比例檢測(cè)主開關(guān)MD1的漏極電流,然后通過在比例晶體管MD2的漏極連接一個(gè)較小的電阻將比例電流轉(zhuǎn)換成電壓VSENS,這樣的優(yōu)點(diǎn)在于:采樣電流的功耗較低,由于采樣電阻連接在晶體管的漏極,電流的比例系數(shù)精確。下面給出VSENS的計(jì)算公式:

![D36NGQ]I$O4[1330H)CN]9N.png D36NGQ]I$O4[1330H)CN]9N.png](http://files.chinaaet.com/images/2015/06/02/6356887264579500002583135.png)

其中,M為功率晶體管電流采樣比例系數(shù),在本設(shè)計(jì)中,檢測(cè)電感電流技術(shù)如圖1所示,MD1的寬長(zhǎng)比是MD3的寬長(zhǎng)比的49倍,即M=49。由RSENSE=2 ?贅電阻把采樣的電流轉(zhuǎn)換成電壓,并通過圖3所示的電路把該采樣的電壓進(jìn)行放大,該放大系數(shù)設(shè)計(jì)為R3/R1,2=5倍。

3 同步功率晶體管驅(qū)動(dòng)電路設(shè)計(jì)

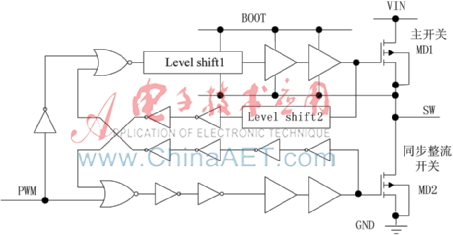

在降壓型DC-DC轉(zhuǎn)換器中,主開關(guān)晶體管使用N溝道LDMOS晶體管,為了能夠驅(qū)動(dòng)該功率開關(guān)晶體管,需要集成片上自舉電路才能驅(qū)動(dòng)LDNMOS功率晶體管。

由于轉(zhuǎn)換器采用同步工作模式,主開關(guān)和同步整流開關(guān)交替導(dǎo)通,為避免主開關(guān)和整流開關(guān)同時(shí)導(dǎo)通可能造成的功率晶體管的損壞,以及損失轉(zhuǎn)換器的效率,同步驅(qū)動(dòng)電路還需要采用死區(qū)時(shí)間控制邏輯電路,詳細(xì)電路圖如圖4所示。當(dāng)同步整流開關(guān)關(guān)閉時(shí),同步整流開關(guān)管的寄生二極管導(dǎo)通,但死區(qū)時(shí)間不能太大,否則會(huì)導(dǎo)致由于寄生二極管導(dǎo)通時(shí)間過長(zhǎng),造成轉(zhuǎn)換效率降低。

功率級(jí)的輸入電源電壓范圍為5~18 V,功率開關(guān)晶體管的柵源電壓為5 V。由于信號(hào)PWM為0~VDD(低電平為0 V,高電平為5 V)的脈沖寬度調(diào)制信號(hào),為了對(duì)主開關(guān)MD1的驅(qū)動(dòng),脈沖寬度調(diào)制信號(hào)的電平需要轉(zhuǎn)換為SW~VBOOT;為了能夠把0~VDD電平轉(zhuǎn)換成低電平為SW,高電平為VBOOT,必須使用電平移位器(圖4中l(wèi)evel shift1);為了能夠?qū)崿F(xiàn)死區(qū)時(shí)間的控制,還需要把SW~VBOOT轉(zhuǎn)換為0~5 V電平,使用圖4中l(wèi)evel shift2。另外,功率器件LDNMOS有比較大的柵電容,因此, LDNMOS前級(jí)反相器采用反相器鏈進(jìn)行驅(qū)動(dòng)。

4 轉(zhuǎn)換器功率級(jí)版圖設(shè)計(jì)考慮

由于降壓型DC-DC轉(zhuǎn)換器的主開關(guān)MD1位于電源和輸出之間,故MD1的背柵與源極相連,而不與襯底電位相連,因此,在版圖設(shè)計(jì)時(shí),該LDNMOS背柵下面需要N型埋層(NBL)作為隔離。功率晶體管的版圖設(shè)計(jì)還需要考慮以下幾個(gè)方面:

首先,確定功率晶體管面積,根據(jù)前面轉(zhuǎn)換器負(fù)載電流對(duì)功率晶體管的需求,采用SMIC 0.35 ?滋m DPTM BCDMOS工藝技術(shù),其LDNMOS的導(dǎo)通電阻每平方毫米為16.5 m?贅(常溫25 ℃),本文設(shè)計(jì)的功率晶體管的面積:MD1為0.5 mm2,MD2為0.5 mm2。

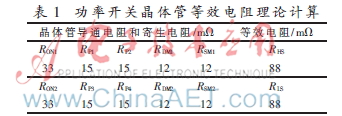

其次,盡可能減小功率晶體管的金屬連線和封裝引線所產(chǎn)生的寄生電阻,下面分別考慮如下:根據(jù)所選用的工藝,采用頂層加厚鋁線來減小金屬連線寄生電阻,同時(shí)對(duì)頂層金屬精心布線來優(yōu)化功率晶體管的寄生電阻;一般來講,對(duì)于設(shè)計(jì)負(fù)載電流大于1 A以上的DC-DC轉(zhuǎn)換器,PAD與封裝管腳一般采用多根金絲,設(shè)計(jì)經(jīng)驗(yàn)1根金絲(1密爾直徑)能夠承受約1 A電流,不同金絲直徑其電阻亦不一樣,特別是設(shè)計(jì)負(fù)載電流大于2 A以上的轉(zhuǎn)換器,由于導(dǎo)通電阻很小,引線寄生電阻在式(1)、(2)中占有的分量不能忽略不計(jì),本設(shè)計(jì)采用4根1密爾金絲作為封裝引線。當(dāng)前,封裝引線采用銅線技術(shù)趨于成熟,而銅線的電阻率比金線電阻率小,而且還有價(jià)格優(yōu)勢(shì),因此采用銅線封裝越來越受歡迎。本設(shè)計(jì)采用上述設(shè)計(jì)思想,計(jì)算得到的功率管的理論值如表1所示。

最后,對(duì)主開關(guān)和同步開關(guān)需要良好的隔離,避免互相干擾;在芯片版圖中,功率器件和模擬電路需要隔離環(huán),衰減開關(guān)噪聲對(duì)內(nèi)部模擬電路的影響。

5 功率級(jí)測(cè)試結(jié)果

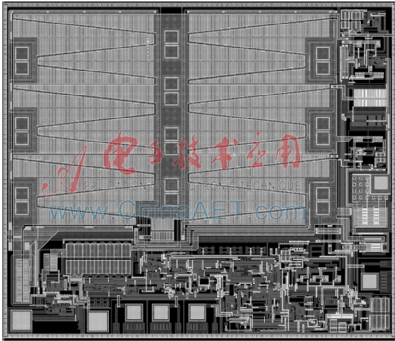

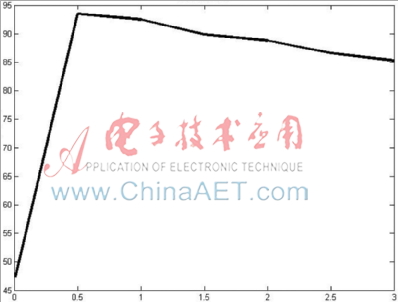

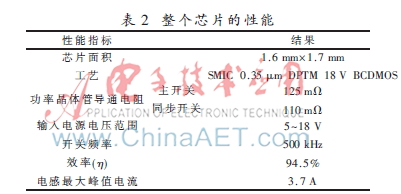

對(duì)前面所述功率級(jí)設(shè)計(jì),應(yīng)用到電流模降壓型DC-DC轉(zhuǎn)換器,采用SMIC 0.35 m DPTM BCD工藝流片,芯片面積為1.6 mm×1.7 mm,電流模降壓型DC-DC版圖結(jié)構(gòu)如圖5所示。通過對(duì)芯片進(jìn)行電氣測(cè)試,測(cè)試條件:外接電感4.7 ?H,輸出電容采用22 ?滋F陶瓷電容,輸入電源電壓為12 V,轉(zhuǎn)換器開關(guān)頻率為500 kHz,輸出電壓設(shè)置為5.0 V,輸出能夠提供3 A負(fù)載電流;圖6給出了輸出為5.0 V,在輸入電源電壓為12 V,不同負(fù)載條件下的效率曲線;表2給出功率級(jí)測(cè)試的結(jié)果,測(cè)試結(jié)果發(fā)現(xiàn),功率開關(guān)導(dǎo)通電阻均大于表1的理論設(shè)計(jì)值,原因在于:表1給出的導(dǎo)通電阻為常溫計(jì)算值,而實(shí)際測(cè)試時(shí),由于在大電流條件下,芯片溫度的上升導(dǎo)致導(dǎo)通電阻增加。

6 結(jié)論

本文采用0.35 m DPTM 18 V BCDMOS工藝技術(shù)設(shè)計(jì)電流模降壓型DC-DC轉(zhuǎn)換器功率級(jí),該功率級(jí)設(shè)計(jì)包括功率晶體管設(shè)計(jì),并給出了功率晶體管的等效導(dǎo)通電阻,電流檢測(cè)電路設(shè)計(jì)以及功率晶體管的驅(qū)動(dòng)電路設(shè)計(jì),最后給出了DC-DC轉(zhuǎn)換器功率級(jí)的版圖設(shè)計(jì)考慮。該功率級(jí)電路已經(jīng)應(yīng)用于DC-DC轉(zhuǎn)換器中,測(cè)試結(jié)果表明:在轉(zhuǎn)換器輸入電壓為12 V、輸出5.0 V時(shí),輸出電流為3 A;其轉(zhuǎn)換效率最大可以達(dá)到94.5%。

參考文獻(xiàn)

[1] LEE C F,MOK P K T.A monolithic current-model cmos DC-DC converter with on chip current-sensing technique[J].IEEE Journal of Solid-State Circuits,2004,39(1):3-14.

[2] Deng Haifei.Monolithically integrated boost converter basedon 0.5 m cmos process[C].IEEE Int.Symp.On Power Semiconductor Devices & ICs,2004:169-172.

[3] MORROW P,GAALAAS E.A 20-W stereo class-D audiooutput power stage in 0.6 ?滋m BCDMOS technology[J].IEEE Journal of Solid-State Circuits,2004,39(11):1948-1958.

[4] HOWER P L.Safe operating area-a new frontier in LDMOSdesign[C].Proc.14th Int.Symposium on Power SemiconductorDevices and ICs,2002:1-8.

[5] BERKHOUT M.An integrated 200-W class-D audio ampli-fier[J].IEEE Journal of Solid-State Circuits,2003,38(7):1198-1206.

[6] FORGHANI-Z H P,RINCON-M G A.Current-sensing techniques for DC-DC converters[C].Proc.of IEEE MWS-CAS.2002:557-580.