實(shí)現(xiàn)數(shù)碼時(shí)鐘的功能,要求能夠進(jìn)行24時(shí)制時(shí)、分、秒的顯示,并能夠通過(guò)按鍵調(diào)整時(shí)間。

二、 實(shí)驗(yàn)原理

通過(guò)對(duì)系統(tǒng)時(shí)鐘進(jìn)行計(jì)數(shù),獲得1S的標(biāo)準(zhǔn)信號(hào),再以該信號(hào)為基礎(chǔ),進(jìn)行時(shí)、分、秒的計(jì)數(shù),通過(guò)數(shù)碼管將該計(jì)數(shù)值顯示出來(lái),即可實(shí)現(xiàn)數(shù)字鐘的功能。同時(shí)可以使用獨(dú)立按鍵對(duì)時(shí)、分、秒計(jì)數(shù)器的初始值進(jìn)行設(shè)置,即可實(shí)現(xiàn)時(shí)間的設(shè)定。

三、 硬件設(shè)計(jì)

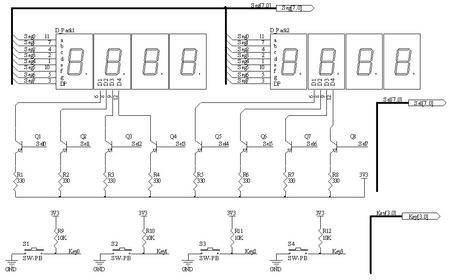

本實(shí)驗(yàn)硬件電路簡(jiǎn)單,用到了8個(gè)數(shù)碼管和4個(gè)獨(dú)立按鍵。硬件電路如下:

圖3-1 數(shù)字鐘電路

四、 架構(gòu)設(shè)計(jì)

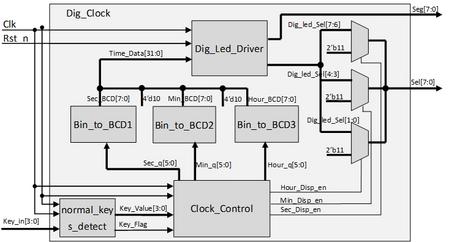

本實(shí)驗(yàn)設(shè)計(jì)架構(gòu)模塊較多,下圖為數(shù)字鐘的架構(gòu):

圖4-1 數(shù)字鐘實(shí)驗(yàn)?zāi)K組織結(jié)構(gòu)圖

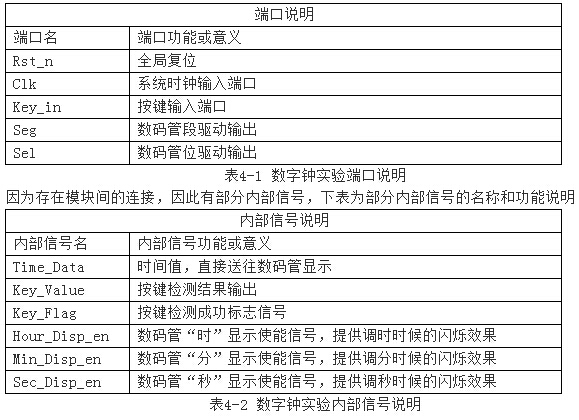

由圖可知本實(shí)驗(yàn)有16個(gè)輸出端口和6個(gè)輸入端口,各端口的意義如下

本站內(nèi)容除特別聲明的原創(chuàng)文章之外,轉(zhuǎn)載內(nèi)容只為傳遞更多信息,并不代表本網(wǎng)站贊同其觀點(diǎn)。轉(zhuǎn)載的所有的文章、圖片、音/視頻文件等資料的版權(quán)歸版權(quán)所有權(quán)人所有。本站采用的非本站原創(chuàng)文章及圖片等內(nèi)容無(wú)法一一聯(lián)系確認(rèn)版權(quán)者。如涉及作品內(nèi)容、版權(quán)和其它問(wèn)題,請(qǐng)及時(shí)通過(guò)電子郵件或電話通知我們,以便迅速采取適當(dāng)措施,避免給雙方造成不必要的經(jīng)濟(jì)損失。聯(lián)系電話:010-82306118;郵箱:[email protected]。