當(dāng)今,在沒有透徹掌握芯片、封裝結(jié)構(gòu)及PCB的電源供電系統(tǒng)特性時(shí),高速電子系統(tǒng)的設(shè)計(jì)是很難成功的。事實(shí)上,為了滿足更低的供電電壓、更快的信號(hào)翻轉(zhuǎn)速度、更高的集成度和許多越來越具有挑戰(zhàn)性的要求,很多走在電子設(shè)計(jì)前沿的公司在產(chǎn)品設(shè)計(jì)過程中為了確保電源和信號(hào)的完整性,對(duì)電源供電系統(tǒng)的分析投入了大量的資金,人力和物力。

電源供電系統(tǒng)(PDS)的分析與設(shè)計(jì)在高速電路設(shè)計(jì)領(lǐng)域,特別是在計(jì)算機(jī)、半導(dǎo)體、通信、網(wǎng)絡(luò)和消費(fèi)電子產(chǎn)業(yè)中正變得越來越重要。隨著超大規(guī)模集成電路技術(shù)不可避免的進(jìn)一步等比縮小,集成電路的供電電壓將會(huì)持續(xù)降低。隨著越來越多的生產(chǎn)廠家從130nm技術(shù)轉(zhuǎn)向90nm技術(shù),可以預(yù)見供電電壓會(huì)降到1.2V,甚至更低,而同時(shí)電流也會(huì)顯著地增加。從直流IR壓降到交流動(dòng)態(tài)電壓波動(dòng)控制來看,由于允許的噪聲范圍越來越小,這種發(fā)展趨勢給電源供電系統(tǒng)的設(shè)計(jì)帶來了巨大的挑戰(zhàn)。

PCB電源供電系統(tǒng)設(shè)計(jì)概覽

通常在交流分析中,電源地之間的輸入阻抗是用來衡量電源供電系統(tǒng)特性的一個(gè)重要的觀測量。對(duì)這個(gè)觀測量的確定在直流分析中則演變成為IR壓降的計(jì)算。無論在直流或交流的分析中,影響電源供電系統(tǒng)特性的因素有:PCB的分層、電源板層平面的形狀、元器件的布局、過孔和管腳的分布等等。

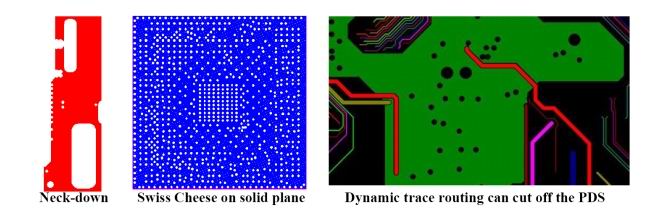

圖1:PCB上一些常見的會(huì)增加電流路徑阻性的物理結(jié)構(gòu)設(shè)計(jì)。

電源地之間的輸入阻抗概念就可以應(yīng)用在對(duì)上述因素的仿真和分析中。比如,電源地輸入阻抗的一個(gè)非常廣泛的應(yīng)用是用來評(píng)估板上去耦電容的放置問題。隨著一定數(shù)量的去耦電容被放置在板上,電路板本身特有的諧振可以被抑制掉,從而減少噪聲的產(chǎn)生,還可以降低電路板邊緣輻射以緩解電磁兼容問題。為了提高電源供電系統(tǒng)的可靠性和降級(jí)系統(tǒng)的制造成本,系統(tǒng)設(shè)計(jì)工程師必須經(jīng)常考慮如何經(jīng)濟(jì)有效地選擇去耦電容的系統(tǒng)布局。

高速電路系統(tǒng)中的電源供電系統(tǒng)通常可以分成芯片、集成電路封裝結(jié)構(gòu)和PCB三個(gè)物理子系統(tǒng)。芯片上的電源柵格由交替放置的幾層金屬層構(gòu)成,每層金屬由X或Y方向的金屬細(xì)條構(gòu)成電源或地柵格,過孔則將不同層的金屬細(xì)條連接起來。

對(duì)于一些高性能的芯片,無論內(nèi)核或是IO的電源供電都集成了很多去耦單元。集成電路封裝結(jié)構(gòu),如同一個(gè)縮小了的PCB,有幾層形狀復(fù)雜的電源或地平板。在封裝結(jié)構(gòu)的上表面,通常留有去耦電容的安裝位置。PCB則通常含有連續(xù)的面積較大的電源和地平板,以及一些大大小小的分立去耦電容元件,及電源整流模塊(VRM)。邦定線、C4凸點(diǎn)、焊球則把芯片、封裝和PCB連接在了一起。

整個(gè)電源供電系統(tǒng)要保證給各個(gè)集成電路器件提供在正常范圍內(nèi)穩(wěn)定的電壓。然而,開關(guān)電流和那些電源供電系統(tǒng)中寄生的高頻效應(yīng)總是會(huì)引入電壓噪聲。其電壓變化可以由下式計(jì)算得到:

![]()

這里ΔV是在器件處觀測到的電壓波動(dòng),ΔI是開關(guān)電流。Z是在器件處觀測到的整個(gè)電源供電系統(tǒng)電源與地之間的輸入阻抗。為了減小電壓波動(dòng),電源與地之間要保持低阻。在直流情況下,由于Z變成了純電阻,低阻就對(duì)應(yīng)了低的電源供電IR壓降。在交流情況下,低阻能使開關(guān)電流產(chǎn)生的瞬態(tài)噪聲也變小。當(dāng)然,這就需要Z在很寬的頻帶上都要保持很小。

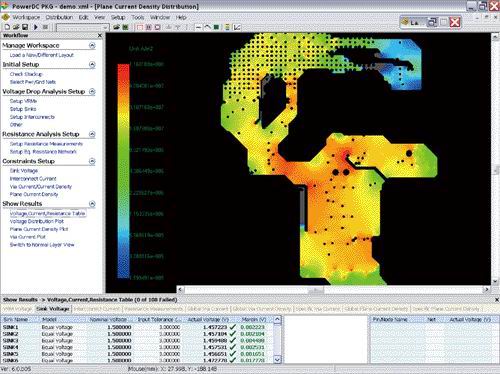

圖2:Sigrity PowerDC計(jì)算得到電源板層上的電流分布。

注意到電源和地通常用來作為信號(hào)回路和參考平面,因此電源供電系統(tǒng)與信號(hào)分布系統(tǒng)之間有著很緊密的關(guān)系。然而,由于篇幅的限制,同步開關(guān)噪聲(IO SSO)引入的電源供電系統(tǒng)的噪聲現(xiàn)象和電流回路控制問題將不在這里討論。以下幾節(jié)將忽略信號(hào)系統(tǒng),而單純注重電源供電系統(tǒng)的分析。

直流IR壓降

由于芯片的電源柵格(Power Grid)的特征尺寸很小(幾微米甚至更小),芯片內(nèi)的電阻損耗嚴(yán)重,因此芯片內(nèi)的IR壓降已經(jīng)被廣泛地研究。而在下面幾種情況下,PCB上的IR壓降(在幾十到幾百毫伏的范圍內(nèi))對(duì)高速系統(tǒng)設(shè)計(jì)同樣會(huì)有較大的影響。

電源板層上有Swiss-Chess結(jié)構(gòu)、Neck-Down結(jié)構(gòu)和動(dòng)態(tài)布線造成的板平面被分割等情況(圖1);電源板層上電流通過的器件管腳、過孔、焊球、C4凸點(diǎn)的數(shù)量不夠,電源平板厚度不足,電流通路不均衡等;系統(tǒng)設(shè)計(jì)需要低電壓、大電流,又有較緊的電壓浮動(dòng)的范圍。

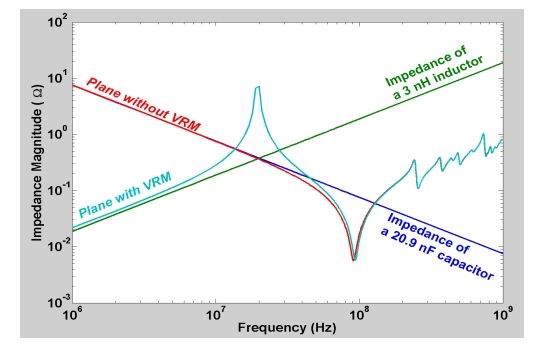

圖3:包括和不包括電源整流模塊的平板對(duì)輸入阻抗。

例如,一個(gè)高密度和高管腳數(shù)的器件由于有大量的過孔和反焊盤,在芯片封裝結(jié)構(gòu)及PCB的電源分配層上往往會(huì)形成所謂的Swiss-Chess結(jié)構(gòu)效應(yīng)。Swiss-Chess結(jié)構(gòu)會(huì)產(chǎn)生很多高阻性的微小金屬區(qū)域。根據(jù)![]() ,由于電源供電系統(tǒng)中有這樣的高阻電流通路,送到PCB上元器件的電壓或電流有可能會(huì)低于設(shè)計(jì)要求。因此一個(gè)好的直流IR壓降仿真模擬是估計(jì)電源供電系統(tǒng)允許壓降范圍的關(guān)鍵。通過各種各樣可能性的分析為布局布線前后提供設(shè)計(jì)方案或規(guī)則。

,由于電源供電系統(tǒng)中有這樣的高阻電流通路,送到PCB上元器件的電壓或電流有可能會(huì)低于設(shè)計(jì)要求。因此一個(gè)好的直流IR壓降仿真模擬是估計(jì)電源供電系統(tǒng)允許壓降范圍的關(guān)鍵。通過各種各樣可能性的分析為布局布線前后提供設(shè)計(jì)方案或規(guī)則。

布線工程師、系統(tǒng)工程師、信號(hào)完整性工程師和電源設(shè)計(jì)工程師還可以將IR壓降分析結(jié)合在約束管理器(constraint manager)中,作為對(duì)PCB上每一個(gè)電源和地網(wǎng)表進(jìn)行設(shè)計(jì)規(guī)則核查的最終檢驗(yàn)工具(DRC)。這種通過自動(dòng)化軟件分析的設(shè)計(jì)流程可以避免靠目測,甚至經(jīng)驗(yàn)所不能發(fā)現(xiàn)的復(fù)雜電源供電系統(tǒng)結(jié)構(gòu)上的布局布線問題。圖2展示了IR壓降分析可以準(zhǔn)確地指出一高性能PCB上電源供電系統(tǒng)中關(guān)鍵電壓電流的分布。

交流電源地阻抗分析

很多人知道一對(duì)金屬板構(gòu)成一個(gè)平板電容器,于是認(rèn)為電源板層的特性就是提供平板電容以確保供電電壓的穩(wěn)定。在頻率較低,信號(hào)波長遠(yuǎn)遠(yuǎn)大于平板尺寸時(shí),電源板層與地板的確構(gòu)成了一個(gè)電容。

然而,當(dāng)頻率升高時(shí),電源板層的特性開始變得復(fù)雜了。更確切地說,一對(duì)平板構(gòu)成了一個(gè)平板傳輸線系統(tǒng)。電源與地之間的噪聲,或與之對(duì)應(yīng)的電磁場遵循傳輸線原理在板之間傳播。當(dāng)噪聲信號(hào)傳播到平板的邊緣時(shí),一部分高頻能量會(huì)輻射出去,但更大一部分能量會(huì)反射回去。來自平板不同邊界的多重反射構(gòu)成了PCB中的諧振現(xiàn)象。

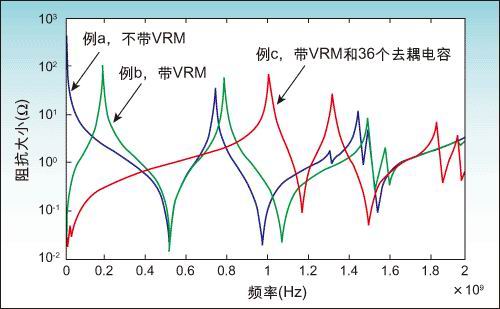

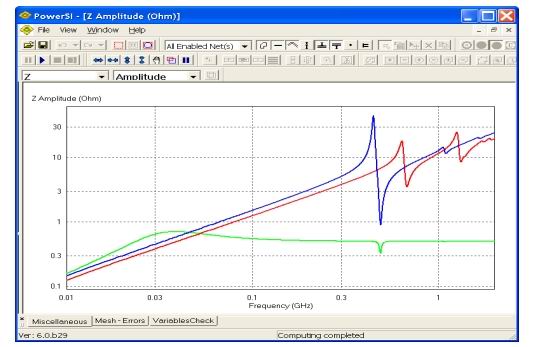

圖4:三種設(shè)置情況下 PowerSI計(jì)算得到的PCB輸入阻抗曲線。(a)不包含電源整流模塊;(b)包含電源整流模塊;(c)包含電源整流模塊和一些去耦電容。

在交流分析中,PCB的電源地阻抗諧振是個(gè)特有的現(xiàn)象。圖3展示了一對(duì)電源板層的輸入阻抗。為了比較,圖中還畫了一個(gè)純電容和一個(gè)純電感的阻抗特性。板的尺寸是30cm×20cm,板間間距是100um,填充介質(zhì)是FR4材料。板上的電源整流模塊用一個(gè)3nH的電感來代替。顯示純電容阻抗特性的是一個(gè)20nF的電容。從圖上可以看出,在板上沒有電源整流模塊時(shí),在幾十兆的頻率范圍內(nèi),平板的阻抗特性(紅線)和電容(藍(lán)線)一樣。在100MHz以上,平板的阻抗特性呈感性(沿著綠線)。到了幾百兆的頻率范圍后,幾個(gè)諧振峰的出現(xiàn)顯示了平板的諧振特性,這時(shí)平板就不再是純感性的了。

至此,很明顯,一個(gè)低阻的電源供電系統(tǒng)(從直流到交流)是獲得低電壓波動(dòng)的關(guān)鍵:減少電感作用,增加電容作用,消除或降低那些諧振峰是設(shè)計(jì)目標(biāo)。

為了降低電源供電系統(tǒng)的阻抗,應(yīng)遵循以下一些設(shè)計(jì)準(zhǔn)則:

1. 降低電源和地板層之間的間距;

2. 增大平板的尺寸;

3. 提高填充介質(zhì)的介電常數(shù);

4. 采用多對(duì)電源和地板層。

然而,由于制造或一些其他的設(shè)計(jì)考慮,設(shè)計(jì)工程師還需要用一些較為靈活的有效的方法來改變電源供電系統(tǒng)的阻抗。為了減小阻抗并且消除那些諧振峰,在PCB上放置分立的去耦電容便成為常用的方法。

圖4顯示了在三種不同設(shè)置下,用Sigrity PowerSI計(jì)算得到的電源供電系統(tǒng)的輸入阻抗:

a. 沒有電源整流模塊,沒有去耦電容放置在板上。

b. 電源整流模塊用短路來模擬,沒有去耦電容放置在板上。

c. 電源整流模塊用短路來模擬,去耦電容放置在板上。

從圖中可見,例子a藍(lán)線,在集成電路芯片的位置處觀測到的電源供電系統(tǒng)的輸入阻抗在低頻時(shí)呈現(xiàn)出容性。隨著頻率的增加,第一個(gè)自然諧振峰出現(xiàn)在800MHz的頻率處。此頻率的波長正對(duì)應(yīng)了電源地平板的尺寸。

例子b的綠線,輸入阻抗在低頻時(shí)呈現(xiàn)出感性。這正好對(duì)應(yīng)了從集成電路芯片的位置到電源整流模塊處的環(huán)路電感。這個(gè)環(huán)路電感和平板電容一起引入了在200MHz的諧振峰。

例子c的紅線,在板上放置了一些去耦電容后,那個(gè)200MHz的諧振峰被移到了很低的頻率處(<20MHz),并且諧振峰的峰值也降低了很多。第一個(gè)較強(qiáng)的諧振峰則出現(xiàn)在大約1GHz處。由此可見,通過在PCB上放置分立的去耦電容,電源供電系統(tǒng)在主要的工作頻率范圍內(nèi)可以實(shí)現(xiàn)較低的并且是平滑的交流阻抗響應(yīng)。因此,電源供電系統(tǒng)的噪聲也會(huì)很低。

圖5:針對(duì)不同結(jié)構(gòu)仿真計(jì)算得到的輸入阻抗。不考慮芯片和封裝結(jié)構(gòu)(紅線);考慮封裝結(jié)構(gòu)(藍(lán)線);考慮芯片、封裝和電路板(綠線)。

在板上放置分立的去耦電容使得設(shè)計(jì)師可以靈活地調(diào)整電源供電系統(tǒng)的阻抗,實(shí)現(xiàn)較低的電源地噪聲。然而,如何選擇放置位置、選用多少以及選用什么樣的去耦電容仍舊是一系列的設(shè)計(jì)問題。因此,對(duì)一個(gè)特定的設(shè)計(jì)尋求最佳的去耦解決方案,并使用合適的設(shè)計(jì)軟件以及進(jìn)行大量的電源供電系統(tǒng)的仿真模擬往往是必須的。

協(xié)同設(shè)計(jì)概念

圖4實(shí)際上還揭示了另一個(gè)非常重要的事實(shí),即PCB上放置分立的去耦電容的作用頻率范圍僅僅能達(dá)到幾百兆赫茲。頻率再高,每個(gè)分立去耦電容的寄生電感以及板層和過孔的環(huán)路電感(電容至芯片)將會(huì)極大地降低去耦效果,僅僅通過PCB上放置分立的去耦電容是無法進(jìn)一步降低電源供電系統(tǒng)的輸入阻抗的。從幾百兆赫茲到更高的頻率范圍,封裝結(jié)構(gòu)的電源供電系統(tǒng)的板間電容,以及封裝結(jié)構(gòu)上放置的分立去耦電容將會(huì)開始起作用。到了GHz頻率范圍,芯片內(nèi)電源柵格之間的電容以及芯片內(nèi)的去耦電容是唯一的去耦解決方案。

圖5顯示了一個(gè)例子,紅線是一個(gè)PCB上放置一些分立的去耦電容后得到的輸入阻抗。第一個(gè)諧振峰出現(xiàn)在600MHz到700MHz。在考慮了封裝結(jié)構(gòu)后,附加的封裝結(jié)構(gòu)的電感將諧振峰移到了大約450MHz處,見藍(lán)線。在包括了芯片電源供電系統(tǒng)后,芯片內(nèi)的去耦電容將那些高頻的諧振峰都去掉了,但同時(shí)卻引入了一個(gè)很弱的30MHz諧振峰,見綠線。這個(gè)30MHz的諧振在時(shí)域中會(huì)體現(xiàn)為高頻翻轉(zhuǎn)信號(hào)的中頻包絡(luò)上的一個(gè)電壓波谷。

芯片內(nèi)的去耦是很有效的,但代價(jià)卻是要用去芯片內(nèi)寶貴的空間和消耗更多的漏電流。將芯片內(nèi)的去耦電容挪到封裝結(jié)構(gòu)上也許是一個(gè)很好的折衷方案,但要求設(shè)計(jì)師擁有從芯片、封裝結(jié)構(gòu)到PCB的整個(gè)系統(tǒng)的知識(shí)。但通常,PCB的設(shè)計(jì)師無法獲得芯片和封裝結(jié)構(gòu)的設(shè)計(jì)數(shù)據(jù)以及相應(yīng)的仿真軟件包。對(duì)于集成電路設(shè)計(jì)師,他們通常不關(guān)心下端的封裝和電路板的設(shè)計(jì)。但顯然采用協(xié)同設(shè)計(jì)概念對(duì)整個(gè)系統(tǒng)、芯片-封裝-電路板的電源供電系統(tǒng)進(jìn)行優(yōu)化分析設(shè)計(jì)是將來發(fā)展的趨勢。一些走在電子設(shè)計(jì)前沿的公司事實(shí)上已經(jīng)這樣做了。

參考文獻(xiàn)

International Technology Roadmap for Semiconductors, 2005 Edition。

Raymond Y.Chen, IBIS Asia Summit, 2005

http://www.eda.org/pub/ibis/summits/dec05/chen.pdf

[3]Jiayuan Fang, Jin Zhao, The Power of Planes - Low Impedance Power Delivery over Broad Frequencies, Printed Circuit Design & Manufacturing Magazine, Sept.2003.

[4]Om, P.Mandhana, Jin Zhao, "Comparative Study on Effectiveness of On-Chip, On-Package and PCB Decoupling for Core Noise Reduction by Using Broadband Power Delivery Network Models, " 55th Electronic Components & Technology Conference, May 31-June 3, 2005,

[5]Jin Zhao, Michael Leins, "Evaluation and Elimination of PCB Edge Radiation Introduced by Core Switching Noise and I/O Simultaneous Switching Noise, " Technical Presentation at 2005 IEEE International Symposium on Electromagnetic Compatibility, 8-12 Aug, 2005, Chicago, Illinois

[6]Please find related information at www.Sigrity.com

[7]John Kane, "On-Chip Power Integrity, Including Package Effects," SOC Central online articles, March 14, 2005.