引 言

隨著嵌入式系統(tǒng)應(yīng)用的迅速發(fā)展,PDA和移動電話等便攜式裝置深入到生產(chǎn)生活的各個角落,嵌入式系統(tǒng)市場有迅速增長趨勢。嵌入式系統(tǒng)一般是由電池來供給電能的,而且大多數(shù)嵌入式設(shè)備都有體積和重量的約束。減少電能消耗不僅能延長電池的壽命,縮短用戶更換電池的周期,而且能提高系統(tǒng)性能與減小系統(tǒng)開銷,甚至能起到保護環(huán)境的作用。

1 嵌入式系統(tǒng)功耗分析

研究微處理器的低功耗設(shè)計技術(shù),首先必須了解它的功耗來源。如圖1所示,從高層次仿真得出的結(jié)論可以看出,通過開關(guān)級功率模擬所獲得的高性能CPU的功率分布關(guān)系。其中,時鐘功耗所占比例最大,包括時鐘發(fā)生、驅(qū)動器、時鐘樹、鎖存器和所有時鐘負(fù)擔(dān)的器件;數(shù)據(jù)通路的功耗僅次于時鐘,主要包括執(zhí)行單元、總線和寄存器文件;片上存儲器的功耗主要由存儲器的大小以及存儲陣列的電路和物理結(jié)構(gòu)所決定;控制單元和I/O的功耗通常占整個芯片功耗的一小部分。

2 嵌入式系統(tǒng)低功耗設(shè)計

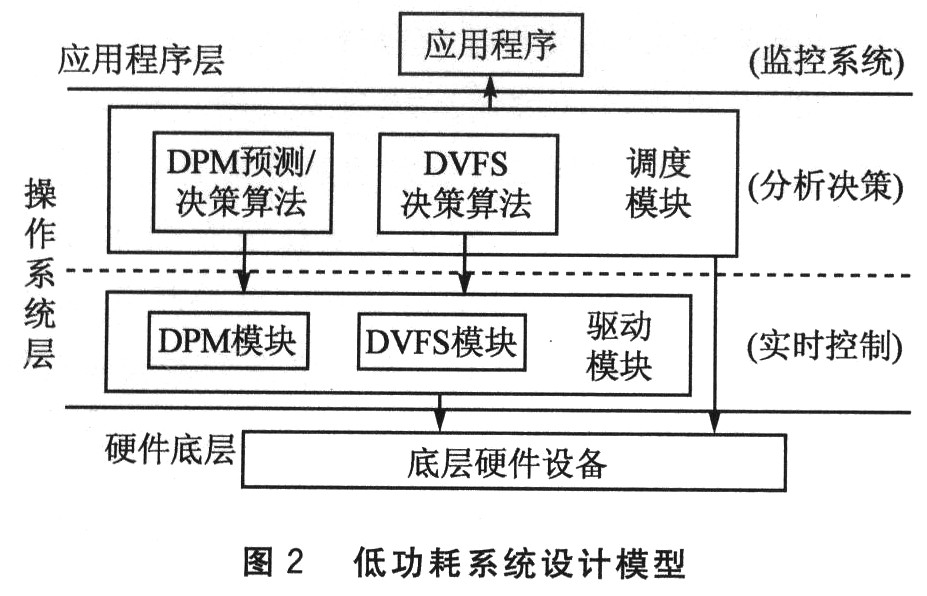

低功耗設(shè)計是一個復(fù)雜的綜合性課題。就流程而言,包括功耗建模、評估以及優(yōu)化等;就設(shè)計抽象層次而言,包括自硬件底層至應(yīng)用程序?qū)拥乃谐橄髮哟危壳暗凸脑O(shè)計大都在操作系統(tǒng)層實施,如圖2所示。同時,功耗優(yōu)化與系統(tǒng)速度和面積等指標(biāo)的優(yōu)化密切相關(guān),需要折中考慮。下面根據(jù)各部分在嵌入式系統(tǒng)中的不同層次,討論常用的低功耗設(shè)計技術(shù)及具體應(yīng)用。

2.1 低功耗硬件設(shè)計

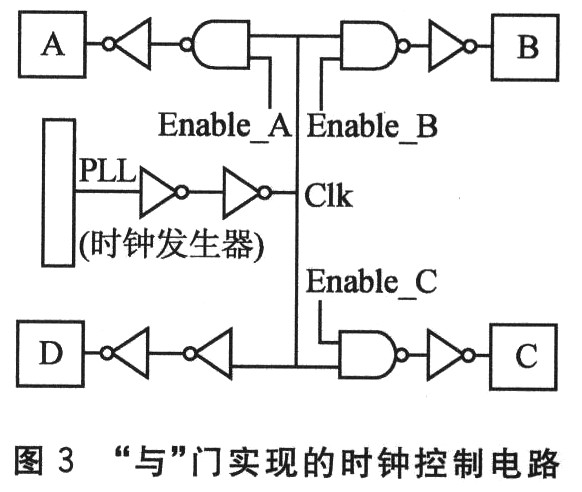

低功耗硬件設(shè)計是嵌入式系統(tǒng)降低功耗的重要內(nèi)容。因此,需要從系統(tǒng)內(nèi)部結(jié)構(gòu)設(shè)計、系統(tǒng)時鐘設(shè)計和低功耗模式等幾方面采用特定的方法(例如,門控時鐘和可變頻率時鐘、并行結(jié)構(gòu)與流水線技術(shù)、低功耗單元庫、低功耗狀態(tài)機編碼、Cache低功耗設(shè)計等)來實現(xiàn)系統(tǒng)硬件節(jié)能設(shè)計。下面介紹門控時鐘和可變頻率時鐘的應(yīng)用。時鐘是惟一在所有時間都充放電的信號,而且很多情況下引起不必要的門的翻轉(zhuǎn),因此降低時鐘的開關(guān)活動性將對降低整個系統(tǒng)的功耗產(chǎn)生很大的影響。門控時鐘包括門控邏輯模塊時鐘和門控寄存器時鐘。門控邏輯模塊時鐘對時鐘網(wǎng)絡(luò)進行劃分,如果在當(dāng)前的時鐘周期內(nèi),系統(tǒng)沒有用到某些邏輯模塊,則暫時切斷這些模塊的時鐘信號,從而顯著降低開關(guān)功耗。圖3為采用“與”門實現(xiàn)的時鐘控制電路。門控寄存器時鐘的原理是當(dāng)寄存器保持?jǐn)?shù)據(jù)時,關(guān)閉寄存器時鐘,以降低功耗。門控時鐘易引起毛刺,必須對信號的時序加以嚴(yán)格限制,并對其進行仔細(xì)的時序驗證。

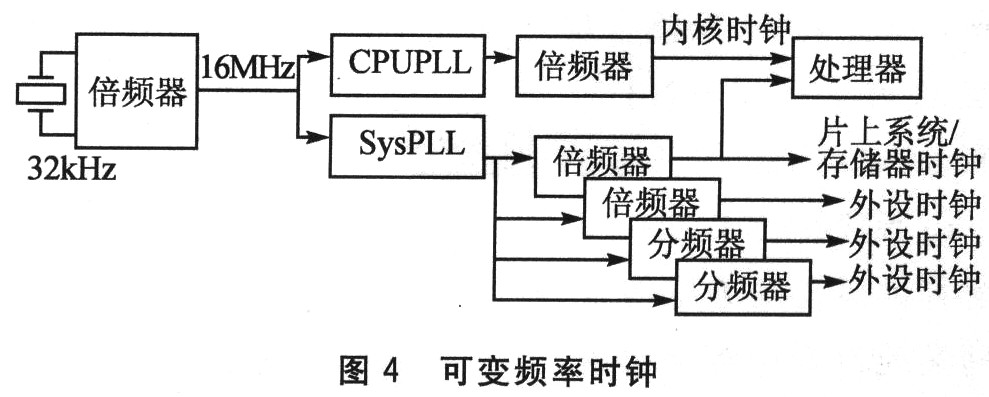

另一種常用的時鐘技術(shù)就是可變頻率時鐘。它可根據(jù)系統(tǒng)性能要求,配置適當(dāng)?shù)臅r鐘頻率以避免不必要的功耗。門控時鐘實際上是可變頻率時鐘的一種極限情況(即只有0和最高頻率兩種值),因此,可變頻率時鐘比門控時鐘技術(shù)更加有效,但需要系統(tǒng)內(nèi)嵌時鐘產(chǎn)生模塊PLL,增加了設(shè)計復(fù)雜度。圖4為在具有低功耗特性的嵌入式芯片上進行的時鐘系統(tǒng)設(shè)計方案。片上時鐘系統(tǒng)通過2個數(shù)字鎖相環(huán)CPUPLL和SysPLL來穩(wěn)定16 MHz的輸入時鐘,分別送到不同的倍頻器和分頻器。經(jīng)CPU-PLL的時鐘信號作為處理器內(nèi)核時鐘,經(jīng)SysPLL的時鐘信號作為處理器內(nèi)核之外的系統(tǒng)時鐘、存儲器時鐘和外設(shè)時鐘。

由于處理器芯片(如i.MX1)不支持電壓動態(tài)調(diào)節(jié),可通過配置片內(nèi)數(shù)字鎖相環(huán)實現(xiàn)內(nèi)核頻率動態(tài)調(diào)節(jié)。根據(jù)公式計算出系統(tǒng)頻率:

![]()

其中:fref是系統(tǒng)的低頻時鐘頻率,作為倍頻的參考頻率;MFI是倍頻因子的整數(shù)部分;MFN和MFD分別是倍頻因子的分子和分母;PD是預(yù)設(shè)分頻因子。

2.2 操作系統(tǒng)層

系統(tǒng)級低功耗設(shè)計一般是在操作系統(tǒng)層實現(xiàn)。因為操作系統(tǒng)管理系統(tǒng)所有軟硬件資源,并獲取系統(tǒng)的各種狀態(tài)信息,控制硬件設(shè)備的狀態(tài)。因此,在操作系統(tǒng)中實現(xiàn)全局功耗控制是最佳選擇。操作系統(tǒng)層面分成功耗驅(qū)動模塊和功耗調(diào)度模塊。

2.2.1 功耗驅(qū)動模塊

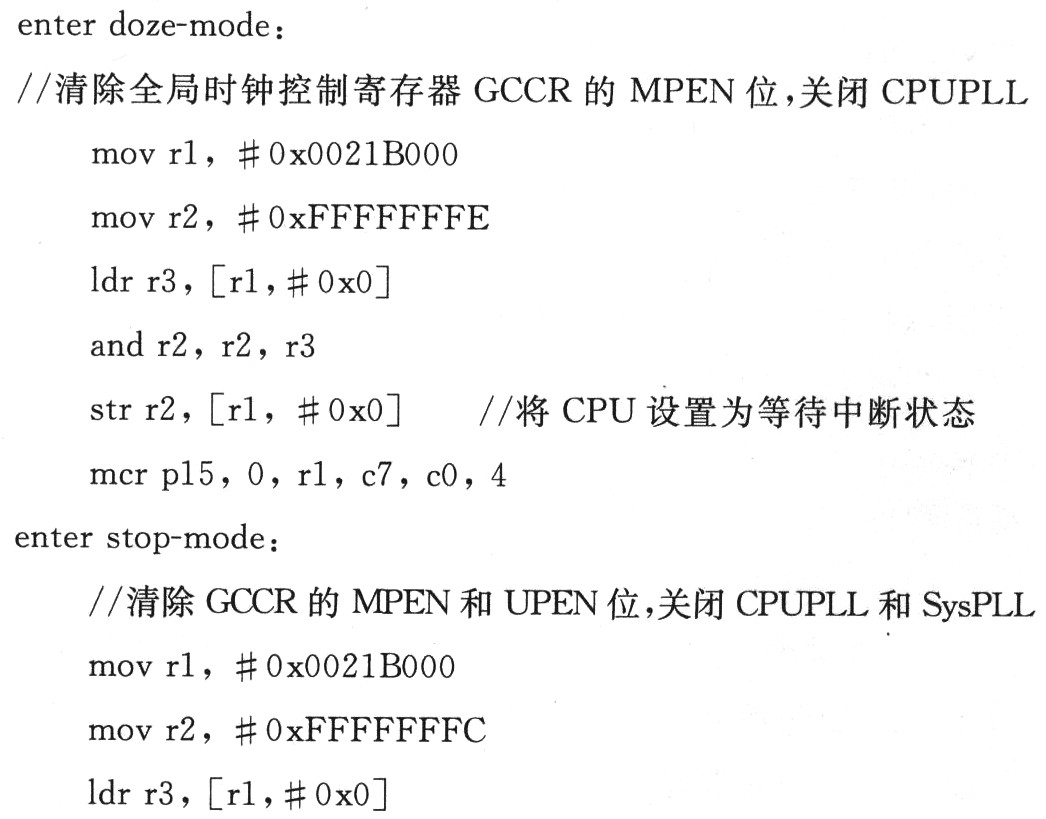

驅(qū)動模塊實現(xiàn)相對簡單,主要是對硬件操作。功耗模式轉(zhuǎn)換和頻率調(diào)節(jié)都是通過片上時鐘系統(tǒng)控制寄存器進行設(shè)置。因此,實質(zhì)上是對寄存器的設(shè)置。從睡眠模式或停止模式進入運行模式相對容易,只需向系統(tǒng)發(fā)出中斷信號,喚醒系統(tǒng)進入運行模式。而從運行模式到睡眠模式或停止模式相對復(fù)雜,其關(guān)鍵代碼如下:

2.2.2 功耗調(diào)度模塊

功耗調(diào)度模塊實現(xiàn)的關(guān)鍵技術(shù)在嵌入式Linux操作系統(tǒng)中有具體體現(xiàn)。在Linux操作系統(tǒng)中,任務(wù)的調(diào)度主要由進程調(diào)度(或任務(wù)調(diào)度)模塊 schedule()完成。schedule()掌握系統(tǒng)內(nèi)所有進程的運行狀態(tài),并對其執(zhí)行的優(yōu)先級進行管理調(diào)度。因此,系統(tǒng)級實現(xiàn)功耗控制,需要對嵌入式Linux內(nèi)核的schedule()模塊全面改寫,將DPM和DVS策略加入其中。設(shè)計思路為:由于Linux內(nèi)核提供的 cpu_usage_stat結(jié)構(gòu)記錄了處理器運行時間的分配情況,可以通過讀取這些參數(shù)計算出當(dāng)前系統(tǒng)的運行比例,即通過cpu_scan函數(shù)來實現(xiàn)具體的操作。cpu_scan函數(shù)是處理器設(shè)備驅(qū)動的主要部分,它在固定的時間片內(nèi)調(diào)用,時間片的大小可以根據(jù)需要在5~1D0 ms之間選取。該函數(shù)通過調(diào)用cpu_dvs函數(shù)和cpu_dmp函數(shù)來評估系統(tǒng)的狀態(tài),這兩個函數(shù)分別是可變電壓技術(shù)和動態(tài)功耗管理的實現(xiàn)。

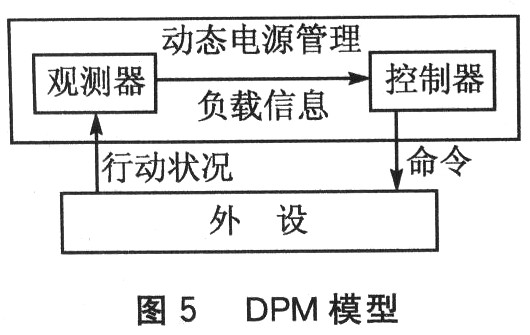

(1)DPM策略

DPM策略在低功耗嵌入式Linux系統(tǒng)的實現(xiàn)上分為觀測器和控制器兩部分,如圖5所示。我們在實現(xiàn)過程中采用了Timeout算法。該算法實現(xiàn)簡單,預(yù)測準(zhǔn)確性也較高。統(tǒng)計表明,只要合理地設(shè)計Timeout,這種假設(shè)的可信度為95%。采用了Timeout算法的cpu_dmp函數(shù)在此不再具體解釋。但在動態(tài)電源管理實現(xiàn)過程中容易出現(xiàn)一個喚醒信號發(fā)送給一個等待隊列中的進程后,該進程不能夠立即被調(diào)度執(zhí)行,從而造成事件丟失的情況。為了避免這種情況的出現(xiàn),Llow被設(shè)置成比Lmax稍小的值。當(dāng)事件數(shù)量到達Llow時,即使事件處理進程被喚醒后不能馬上轉(zhuǎn)入執(zhí)行,由于Llow

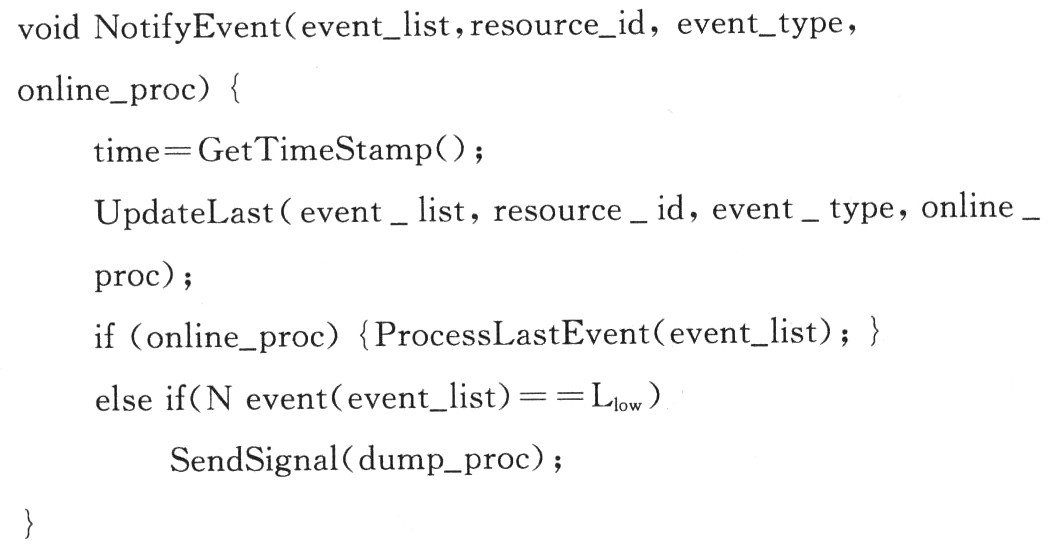

更新事件列表算法代碼如下:

顯式資源需要對驅(qū)動程序作一些修改,即在驅(qū)動程序發(fā)送執(zhí)行命令前和硬件完成服務(wù)并通過驅(qū)動程序告訴內(nèi)核設(shè)備就緒后這兩個時間點,插入一個NotifyEvent()函數(shù)調(diào)用。具體的代碼插入點根據(jù)不同類型的設(shè)備和對服務(wù)開始與結(jié)束的不同定義而不同。

根據(jù)觀測器得到的系統(tǒng)資源訪問歷史記錄計算出優(yōu)化策略之后,控制模塊將在通過電源管理機發(fā)出控制命令給相應(yīng)的硬件完成服務(wù),并通過驅(qū)動程序告訴內(nèi)核設(shè)備就緒后這兩個時間點插入一個NotifyEvent()函數(shù)調(diào)用。

(2)DVS策略

目前,嵌入式系統(tǒng)降低功耗多采用動態(tài)電壓縮放技術(shù)Ⅲ,即系統(tǒng)運行時可以通過設(shè)置可編頻率寄存器控制處理器的工作頻率。實驗觀察發(fā)現(xiàn),系統(tǒng)的運行負(fù)荷具有明顯的非平穩(wěn)特性,短時間內(nèi)可能具有很高的執(zhí)行負(fù)荷,但絕大部分時間維持輕負(fù)荷狀態(tài)。DVS技術(shù)根據(jù)嵌入式系統(tǒng)這一特點,在系統(tǒng)負(fù)荷較重時將處理器設(shè)置為最高執(zhí)行速度,以保證系統(tǒng)的計算能力;而在系統(tǒng)負(fù)荷較輕時動態(tài)降低處理器的工作頻率,以降低處理器的執(zhí)行功耗,從而實現(xiàn)系統(tǒng)計算性能與功耗的優(yōu)化控制,如圖 6所示。DVS的預(yù)測通過采用了基于時間間隔AVGn算法的cpu_dvs函數(shù)實現(xiàn)。該函數(shù)讀取CPU使用信息,按照AVGn算法來估算系統(tǒng)的運行負(fù)荷,并根據(jù)返回給cpu_scan函數(shù)的結(jié)果實現(xiàn)具體的動態(tài)電壓縮放。

AVGn算法分析了多種簡單或復(fù)雜的估計算法和平滑技術(shù)。其基本思想是采用指數(shù)平滑平均值方法,即預(yù)測即將到來的間隔的n個運行百分比的加權(quán)平均值。但AVGn算法存在一個問題就是,逐檔改變頻率導(dǎo)致系統(tǒng)不能及時地響應(yīng)負(fù)載變化,還需要大量深入細(xì)致的研究。

2.3 應(yīng)用程序?qū)?br />

在基于微處理器、微控制器的系統(tǒng)中,軟件起到了引導(dǎo)硬件活動的主導(dǎo)作用。也就是說,軟件對系統(tǒng)的能量消耗有很大的影響。直到目前,還沒有有效且精確的方法可用來評估軟件設(shè)計對能量消耗所起的效應(yīng)。沒有能量評估,就無法對軟件進行優(yōu)化進而減少電能消耗。引起CPU電能消耗的眾多因素中,至少有2個受軟件的影響極大——存儲系統(tǒng)與系統(tǒng)總線。在嵌入式系統(tǒng)的低功耗軟件設(shè)計中,主要考慮這2個因素。

3 總 結(jié)

功耗已經(jīng)成為嵌入式系統(tǒng)設(shè)計中優(yōu)先要考慮的問題,隨著處理器速度越來越快,如何降低功耗已經(jīng)成為衡量嵌入式系統(tǒng)性能優(yōu)良的一個重要方面。因此,在低功耗嵌入式系統(tǒng)設(shè)計過程中要考慮各部分具體的低功耗設(shè)計方法,同時也要充分發(fā)揮各抽象層的低功耗技術(shù)優(yōu)勢。

本文介紹的低功耗嵌入式系統(tǒng)中仍有很多不足,有待進一步探索:①DPM隨機決策模型和求解算法,并沒有解答最優(yōu)策略是否存在、若存在最優(yōu)策略具有什么特性等基本問題,也沒能從理論上解釋“實踐中超時策略可以取得優(yōu)良節(jié)能效果”的原因。②本文的DVS策略采用與AVGn算法類似的假設(shè)條件,在實際應(yīng)用中這些條件過于苛刻。如何將本文DVS策略的思想應(yīng)用到特定的非理想情況的嵌入式系統(tǒng)中,尚需進一步研究。