80C186XL16位嵌入式微處理器是Intel公司在嵌入式微處理器市場(chǎng)的上導(dǎo)產(chǎn)品之一,已廣泛應(yīng)用于電腦終端、程控交換和工控等領(lǐng)域。在該嵌入式微處理器片內(nèi),集成有DRAM RCU單元,即DRAM刷新控制單元。RCU單元可以自動(dòng)產(chǎn)生DRAM刷新總線周期,它工作于微處理器的增益模式下。經(jīng)適當(dāng)編程后,RCU將向?qū)⑻幚砥鞯腂IU(總線接口)單元產(chǎn)生存儲(chǔ)器讀請(qǐng)求。對(duì)微處理器的存儲(chǔ)器范圍編程后,BIU單元執(zhí)行刷新周期時(shí),被編程的存儲(chǔ)器范圍片選有效。

存儲(chǔ)器是嵌入式計(jì)算機(jī)系統(tǒng)的重要組成部分之一。通常采用靜態(tài)存儲(chǔ)器,但是在系統(tǒng)需要大容量存儲(chǔ)器的情況下,這種方式將使成本猛增。如果采用DRAM存儲(chǔ)器,則可以大幅度降低系統(tǒng)設(shè)計(jì)成本;但DRAM有復(fù)雜的時(shí)序要求,給系統(tǒng)設(shè)計(jì)帶來(lái)了很大的困難。

為了方便地使用DRAM,降低系統(tǒng)成本,本文提出一種新穎的解決方案:利用80C186XL的時(shí)序特征,采用CPLD技術(shù),并使用VHDL語(yǔ)言設(shè)計(jì)實(shí)現(xiàn)DRAM控制器。

一、80C186XL RCU單元的資源

80C186XL的BIU單元提供20位地址總線,RCU單元也為刷新周期提供20位地址總線。80C186XL能夠產(chǎn)生刷新功能,并將刷新?tīng)顟B(tài)編碼到控制信號(hào)中。

嵌入式系統(tǒng)中DRAM控制器的CPLD解決方案" border="0" src="http://files.chinaaet.com/images/20100810/b8388cb9-aab1-4b7a-8f87-a7aee2db3cd9.jpg" />

圖1是RCU單元的方框圖。它由1個(gè)9位遞減定時(shí)計(jì)數(shù)器、1個(gè)9位地址計(jì)數(shù)器、3個(gè)控制寄存器和接口邏輯組成。當(dāng)RCU使能時(shí),遞減定時(shí)計(jì)數(shù)器每一個(gè)CLKOUT周期減少1次,定時(shí)計(jì)數(shù)器的值減為1時(shí),則產(chǎn)生刷新總線請(qǐng)求,遞減定時(shí)計(jì)數(shù)器重載,操作繼續(xù)。刷新總線周期具有高優(yōu)先級(jí),旦80C186XL總線有空,就執(zhí)行刷新操作。

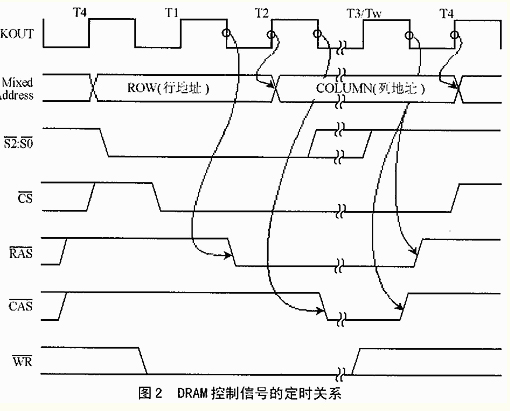

設(shè)計(jì)者可將刷新總線周期看成是“偽讀”周期。刷新周期像普通讀周期一樣出現(xiàn)在80C186XL總線上,只是沒(méi)有數(shù)據(jù)傳輸。從引腳BHE/RFSH和A0的狀態(tài)可以判別刷新周期,如表1所列。刷新總線周期的時(shí)序要求如圖2所示。

表1 刷新周期的引腳狀態(tài)

二、80C186XL DRAM控制器的設(shè)計(jì)與運(yùn)行

DRAM存在著大量、復(fù)雜的時(shí)序要求,其中訪問(wèn)時(shí)間的選擇、等待狀態(tài)以及刷新方法是至關(guān)重要的。DRAM控制器必須正確響應(yīng)80C186XL的所有總線周期,必須能將DRAM的部周期和其它訪問(wèn)周期分辨出來(lái),其訪問(wèn)速度必須足夠快,以避免不必要的等待周期。

在設(shè)計(jì)時(shí),我們采用XC95C36-15 CPLD[2]以及4Mbits的V53C8258[3]DRAM作范例。15ns的CPLD,速度相對(duì)較高,價(jià)格比較便宜。用它設(shè)計(jì)成的DRAM控制器允許80C186XL的工作速度高達(dá)20MHz,并且XC95C36有異步時(shí)鐘選擇項(xiàng)。這種特性對(duì)本設(shè)計(jì)有很大的好處。

圖3是80C186XL DRAM控制器和存儲(chǔ)器的功能框圖。

DRAM控制器由80C186XL狀態(tài)信號(hào)S2、S1和S0的解碼來(lái)檢測(cè)總線的開(kāi)始、類型和結(jié)束。這些狀態(tài)線是在CLKOUT的上升沿開(kāi)始有效,在CLKOUT的下降沿失效的。DRAM控制器發(fā)出的RAS和CAS信號(hào)應(yīng)該在CLKOUT的下降沿同時(shí)有效,行列地址應(yīng)該在CLKOUT上升沿附近提供。

DRAM控制器應(yīng)該在CLKOUT的兩個(gè)沿都應(yīng)能正常操作。通過(guò)啟用XC95C36的異步時(shí)鐘選擇項(xiàng),每個(gè)XC95C36宏單元可以從可編程與陣列獲得時(shí)鐘。DRAM控制器使用80C186XL的CLKOUT信號(hào)作時(shí)鐘輸入。

DRAM控制器主要由兩個(gè)相互聯(lián)的狀態(tài)機(jī)構(gòu)成。這兩個(gè)狀態(tài)機(jī),使得DRAM的控制與80C186XL是否進(jìn)行等待狀態(tài)無(wú)關(guān)。狀態(tài)機(jī)A和地址多路控制信號(hào)(MUX)在CLKOUT的上升沿鎖存。狀態(tài)機(jī)B和RAS及CAS的邏輯在CLKOUT的下降沿鎖存。DRAM控制器完整的VHDL語(yǔ)言的源代碼可Email給[email protected]索取。

DRAM控制器的狀態(tài)圖如圖4所示,狀態(tài)機(jī)A和B的起始條件分別是A0和B0。狀態(tài)機(jī)A初始化DRAM控制器的序列,狀態(tài)機(jī)B終止該序列。

在T2的下降沿,RAS邏輯采樣狀態(tài)機(jī)A的狀態(tài),鎖存的地址線和總經(jīng)狀態(tài)信號(hào)。如果狀態(tài)機(jī)A在A1狀態(tài)(存儲(chǔ)器讀、寫或刷新周期)并且總線周期為DRAM使用,則XC95C36插入RAS信號(hào)。

在T2的上升沿,狀態(tài)機(jī)A也采樣鎖存的地址線。如果總線周期被DRAM占用,狀態(tài)機(jī)A將從狀態(tài)A1轉(zhuǎn)移到A2,否則狀態(tài)機(jī)A轉(zhuǎn)換到A3。至此控制轉(zhuǎn)移到狀態(tài)機(jī)B。MUX邏輯采樣RAS和BHE引腳的狀態(tài)。如果RAS有效(指示DRAM在訪問(wèn)),并且總線周期下是刷新周期,XC95C36將插入MUX。MUX在行列地址之間切換,以便進(jìn)行DRAM的讀寫操作。

在T3的下降沿,狀態(tài)機(jī)B采樣狀態(tài)機(jī)A。如果狀態(tài)機(jī)A處于狀態(tài)A2(DRAM訪問(wèn))或狀態(tài)A3(存儲(chǔ)器讀或?qū)懀皇荄RAM訪問(wèn)),狀態(tài)機(jī)B從狀態(tài)B0轉(zhuǎn)到B1。如果總線周期是一個(gè)DRAM訪問(wèn)周期,XC95C36繼續(xù)保持RAS有效。CAS邏輯采樣MUX的狀態(tài)、鎖存地址A0、BHE和總線周期狀態(tài)。如果MUX有效(指示DRAM讀或?qū)懀⑶以L問(wèn)低字節(jié),則XC95C36插入LCAS;如果MUX有效,并且微處理器訪問(wèn)高字節(jié),XC95C36插入U(xiǎn)CAS。DRAM讀訪問(wèn)和DRAM刷新訪問(wèn)不同之處在于:對(duì)刷新來(lái)說(shuō),不需要MUX、UCAS和LCAS。

在T3的上升沿,狀態(tài)機(jī)A等待狀態(tài)機(jī)B中斷此序列。如果MUX有效(DRAM讀或?qū)懀鼘⒈3钟行А?/p>

有下一個(gè)降沿,狀態(tài)機(jī)B采樣總線狀態(tài)信號(hào)。如果狀態(tài)信號(hào)仍然有效,則此狀態(tài)為等待狀態(tài)Tw,狀態(tài)機(jī)B保持在狀態(tài)B1。如果這個(gè)狀態(tài)是等待狀態(tài),并且RAS有效(DRAM訪問(wèn)),RAS保持有效;如果狀態(tài)為等待狀態(tài),并且UCAS和LCAS有效(DRAM讀或?qū)懀琔CAS和LCAS保持有效。

在等待狀態(tài)的上升沿,狀態(tài)機(jī)A繼續(xù)等待狀態(tài)機(jī)B來(lái)中斷此序列。如果MUX有效(DRAM讀或?qū)懀瑒t它在T3狀態(tài)里保持有效。

如果微處理器狀態(tài)信號(hào)無(wú)效,這個(gè)狀態(tài)則是一個(gè)T4狀態(tài),狀態(tài)機(jī)B從B1轉(zhuǎn)到B2.如果狀態(tài)是一個(gè)T4狀態(tài),并且RAS有效(DRAM訪問(wèn)),則RAST4狀態(tài),并且RAS有效(DRAM訪問(wèn)),則RAS邏輯也檢測(cè)無(wú)效狀態(tài)信號(hào),并且XC95C36關(guān)閉RAS信號(hào);如果狀態(tài)是一個(gè)T4狀態(tài),并且UCAS和LCAS有效(DRAM讀或?qū)懀瑒tCAS邏輯也采樣總線狀態(tài)信號(hào);如果狀態(tài)信號(hào)無(wú)效,則XC95C36關(guān)閉UCAS和LCAS信號(hào)。

在T4的上升沿,狀態(tài)機(jī)A采樣狀態(tài)機(jī)B的狀態(tài)。在狀態(tài)機(jī)B處于B2狀態(tài)的情況下,狀態(tài)機(jī)A從A2狀態(tài)(DRAM訪問(wèn))或A3狀態(tài)(存儲(chǔ)器讀或?qū)懀皇荄RAM訪問(wèn))轉(zhuǎn)到A0。如果MUX有效,MUX邏輯檢查RAS的狀態(tài);如果RAS無(wú)效(指示一個(gè)終止周期),XC95C36關(guān)閉MUX。

在下一個(gè)CLKOUT下降沿,狀態(tài)機(jī)B無(wú)條件地從狀態(tài)B2轉(zhuǎn)到B0,終止DRAM序列。控制轉(zhuǎn)移給狀態(tài)機(jī)A。

三、80C186XL RCU單元的編程

要使DRAM正常工作,就必須對(duì)80C186XL中與DRAM刷新有關(guān)的寄存器進(jìn)行正確編程。這些寄存器包括:刷新時(shí)鐘間隔寄存器(RFTIME寄存器)、刷新基地址寄存器(RFBASE寄存器)和刷新控制寄存器(RFCON寄存器)。

刷新時(shí)鐘間隔寄存器(RFTIME寄存器)的編程公式為:Trefresh×fcpu/(Rrow+Rrows×補(bǔ)償因子)。V53C8258的技術(shù)參數(shù)規(guī)定,其刷新周期Trefresh為8ms,存儲(chǔ)陣列行數(shù)Rrows為512。考慮到RCU取得總線控制權(quán)的延時(shí),補(bǔ)償因子取0.05。因此,微處理器在fcpu=20MHz工作頻率下,RFTIME寄存器的取值為:0.008×20×10 6/(512+512×0.05),約為297.

刷新基地址寄存器(RFBASE寄存器)的編程。該寄存器的高7位,規(guī)定了DRAM容量大小。系統(tǒng)使用兩片V53C8258情況下,RFBASE的取值為00H,DRAM占用微處理器的存儲(chǔ)空間的00000H~7FFFFH(512KB)。

最后通過(guò)將刷新控制寄存器(RFCON寄存器)的REN位置位,來(lái)啟動(dòng)刷新控制單元。

若使用80C186XL的節(jié)電模式,則要求重新編程這些值。在寫節(jié)電控制寄存器前,必須先用要時(shí)鐘分頻值去除原先設(shè)置在刷新間隔寄存器的值,來(lái)重新設(shè)置寄存器。

四、結(jié)束語(yǔ)

現(xiàn)在DRAM、CPLD的價(jià)格非常低,這樣設(shè)計(jì)者有機(jī)會(huì)在嵌入式計(jì)算機(jī)系統(tǒng)設(shè)計(jì)中考慮采用DRAM。80C186XL嵌入式微處理器廣泛應(yīng)用于嵌入式計(jì)算機(jī)、程控通信和工業(yè)控制系統(tǒng)中,具有良好的性價(jià)比,其性能和功能是80C31、80C196等單片機(jī)無(wú)法比擬的,并能充分利用大量的PC平臺(tái)軟件。本解決方案已在家庭電子證券產(chǎn)品中采用,獲得了良好的經(jīng)濟(jì)效益和社會(huì)效益。

掌握CPLD技術(shù)和VHDL語(yǔ)言設(shè)計(jì)技巧是提升產(chǎn)品技術(shù)含量的重要途徑。上述CPLD還留在一些引腳和內(nèi)部資源未使用,只要設(shè)計(jì)者將VHDL源代碼稍微作一些修改,就可以用這些引腳控制新增加的DRAM,提供總線準(zhǔn)備輸出信號(hào)或DMA響應(yīng)信號(hào)。

如果采用引腳數(shù)和宏單元較多的XC9672或XC95108CPLD,就可以將D觸發(fā)器(74HC74)、多路地址切換器(74HC157)、數(shù)據(jù)收發(fā)器(74HC245)和地址總線鎖存器(74HC373)等其它分立邏輯器件的功能全部集成到CPLD中,這樣系統(tǒng)集成度和可靠性將更加提高。