Altera于2008年第二季度推出Stratix® IV和HardCopy® IV器件系列標(biāo)志著世界上首款40-nm FPGA和業(yè)界唯一40-nm ASIC 無風(fēng)險移植途徑的誕生,。Altera 通過三年周密的規(guī)劃和開發(fā),,并與代工線合作伙伴臺積電(TSMC) 協(xié)作,最終獲得成功,,交付定制邏輯器件展示了無可爭議的產(chǎn)品領(lǐng)先優(yōu)勢,。Altera 隨后于2009 年第一季度發(fā)布Arria® II GX 和Stratix IV GT FPGA 系列,實現(xiàn)了業(yè)界最全面的收發(fā)器系列產(chǎn)品,。表1 所示為Altera 開發(fā)世界上首款40-nm FPGA 的歷史過程,。

40-nm 工藝節(jié)點非常重要,它為Altera 在性能最好、密度最大,、功耗最低,、性價比最高FPGA 和HardCopyASIC 上保持領(lǐng)先優(yōu)勢打下了堅實的基礎(chǔ)。

40-nm 工藝技術(shù)的重要性

40-nm 工藝要比以前包括65-nm 節(jié)點和最近的45-nm 節(jié)點在內(nèi)的工藝技術(shù)有明顯優(yōu)勢,。最引人注目的優(yōu)勢之一是其更高的集成度,,半導(dǎo)體生產(chǎn)商可以在更小的物理空間中實現(xiàn)更強的功能。國際電子器件大會(IEDM) 報告了密度提高所得到的實際結(jié)果,,主要的半導(dǎo)體生產(chǎn)商展示了他們在工藝技術(shù)上努力的結(jié)果,。

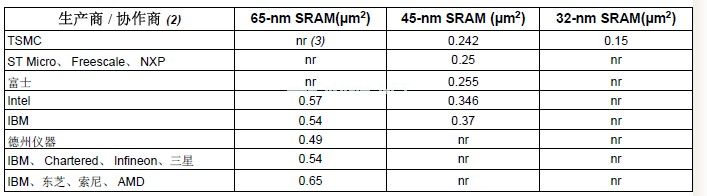

對SRAM 單元大小進行了基準(zhǔn)測試,表2 列出了上次IEDM 大會報道的最近工藝節(jié)點的SRAM 單元大小(以45-nm 工藝單元大小遞增的順序列出),。如表中所示,,工藝技術(shù)的提高使半導(dǎo)體生產(chǎn)商能夠在更小的面積上實現(xiàn)更強的功能。

注釋:

(1) 來源:Real World Technologies, “Process Technology Advancements at IEDM 2007”

(2) 僅列出了報道65-nm 或者45-nm SRAM 單元大小的公司/ 組織

(3) nr = 沒有報道

表1. Altera 40-nm 器件的開發(fā)過程

日期里程碑

2005 年第一季度Altera 啟動40-nm FPGA 和HardCopy ASIC 系列開發(fā),,在40-nm 工藝上開始與TSMC 合作,。

2005 年第四季度Altera 的第一組9 種40-nm 器件測試芯片投片

2006 年第二季度測試芯片結(jié)構(gòu)評估

2007 年第四季度TSMC 發(fā)布產(chǎn)品級45-nm 工藝,加強與Altera 的合作,。

2008 年第一季度TSMC 發(fā)布40-nm 工藝

2008 年第二季度Altera 發(fā)布世界上首款40-nm FPGA,, Stratix IV 器件系列和首款40-nm HardCopy IV ASIC。

2009 年第一季度Altera 發(fā)布最全面的收發(fā)器系列產(chǎn)品,,包括Arria II GX 和Stratix IV GT FPGA,。

表2. 65-nm 和45-nm 工藝節(jié)點報道的最小SRAM 單元 (1)

在40-nm 工藝節(jié)點實現(xiàn)世界上最先進的定制邏輯器件Altera 公司

40-nm 工藝還具有明顯的性能優(yōu)勢。40 nm晶體管邏輯門長度比65 nm 邏輯門長度短38.5%,,比45-nm 工藝邏輯門長度短11%,。相應(yīng)的低阻抗提高了40 nm 的驅(qū)動能力,意味著性能更好的晶體管,。

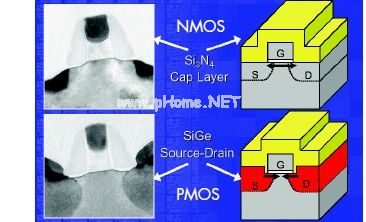

Altera 使用應(yīng)變硅技術(shù)進一步提高了性能,。例如, Altera 器件利用了NMOS 晶體管保護層的拉伸應(yīng)變以及

PMOS 晶體管源極和漏極攙雜硅鍺的壓縮應(yīng)變( 參見圖1),。這些應(yīng)變硅技術(shù)將電子和空穴的移動能力提高了

30%,,使晶體管性能提高了近40%。

圖1. 40 nm 應(yīng)變硅技術(shù)實現(xiàn)了性能更好的晶體管

密度和性能的提高意義非常大,,而當(dāng)今系統(tǒng)開發(fā)人員面臨的最大設(shè)計問題之一是功耗,。40-nm 節(jié)點在這方面也有一定的優(yōu)勢,更小的工藝尺寸減小了產(chǎn)生動態(tài)功耗的雜散電容,。特別是,, TSMC 的40-nm 工藝技術(shù)比45-nm 工藝技術(shù)有功功率降低了15%。

然而,,如果不采取措施,,工藝尺寸的減小會增大待機功耗,。為解決這些問題以及其他越來越多的功耗問題,Altera 采取了積極的措施來降低40-nm 器件的有功功耗和待機功耗,。

結(jié)合領(lǐng)先的工藝和器件體系結(jié)構(gòu)滿足關(guān)鍵的系統(tǒng)設(shè)計需求過渡到40-nm 節(jié)點實現(xiàn)了摩爾定律預(yù)言的密度和性能優(yōu)勢,。利用這些工藝優(yōu)勢并結(jié)合器件體系結(jié)構(gòu)創(chuàng)新,Altera 繼續(xù)為業(yè)界提供密度最大,、性能最好的定制邏輯器件,。由此, Altera® Stratix IV FPGA 和HardCopy IVASIC 分別能夠提供650K邏輯單元(LE) 和13M ASIC 邏輯門,。在性能方面,,Altera 40-nm器件系列邏輯性能達到了600-MHz,收發(fā)器性能高達8.5 Gbps,,同時,, 1.6 Gbps 的LVDS I/O 和1066 Mbps 的單端I/O 性能都是業(yè)界最好的,所有這些都不以犧牲信號完整性為代價,。

除了最高的密度和最好的性能,, Altera 還致力于實現(xiàn)最低的功耗。當(dāng)今小外形緊湊封裝,、便攜性以及功效的發(fā)展趨勢推動了對低功耗的需求,。產(chǎn)品系統(tǒng)外形非常薄,,體積非常小,,限制了空氣對流、熱沉以及其他的散熱管理解決方案,。此外,,很多應(yīng)用首先考慮的問題是功率元件的工作成本,這促使低功耗成為最明顯的競爭優(yōu)勢,,是很多應(yīng)用中必須要考慮的問題,。設(shè)計目標(biāo)在這方面的變化使得功耗成為選擇系統(tǒng)元件時首先要考慮的標(biāo)準(zhǔn)。

FPGA 供應(yīng)商的器件在功能越來越強的電路板上發(fā)揮的作用也越來越大,,在很多情況下要實現(xiàn)系統(tǒng)核心功能,,器件功耗管理的難度也隨之增大。需要很大的投入才能在提高性能和降低功耗上達到平衡,。

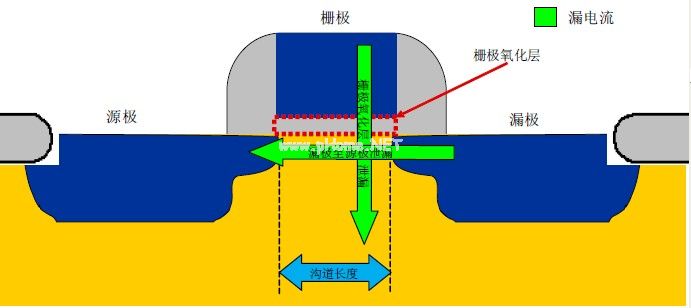

在深亞微米,,隨著向高級工藝的過渡,由于靜態(tài)功耗顯著增大,,半導(dǎo)體功耗成為非常關(guān)鍵的問題,。物理距離減小更容易出現(xiàn)電流泄漏。漏極至源極泄漏和柵極泄漏都與溝道長度和邏輯門氧化層厚度成反比,,隨著長度和厚度的減小會顯著增大( 圖2),。

NMOS

PMOS

Altera 公司 在40-nm 工藝節(jié)點實現(xiàn)世界上最先進的定制邏輯器件

圖2. 晶體管源極漏電流

源極至漏極泄漏也被稱為亞閾值泄漏,,是漏電流的主要因素。在這里,,即使晶體管邏輯門關(guān)斷,,電流也會從晶體管源極流向漏極。由于晶體管越來越小,,很難防止出現(xiàn)這類電流,,因此,在其他參數(shù)都相同的條件下,,較小的40-nm 晶體管比大工藝尺寸的晶體管更容易出現(xiàn)源極至漏極泄漏,,而且漏電流更大。

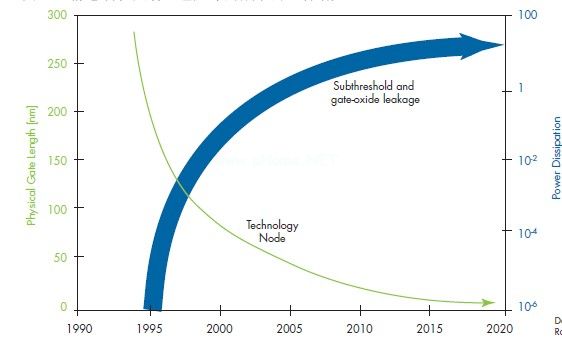

晶體管閾值電壓(Vt) 也會影響源極至漏極泄漏的大小,。晶體管Vt 是溝道開始傳導(dǎo)柵極和源極之間電流的電壓值,。較小的高速晶體管需要較低的Vt 通過柵極控制來保持晶體管打開和關(guān)斷的速率,但是由于晶體管溝道不能徹底關(guān)斷,,這也會增加漏電流,。另一問題是柵極氧化層的厚度,它和攙雜一起也會影響Vt,。較薄的氧化層使晶體管能夠更迅速地開關(guān),,但是也增加了從柵極到基底氧化層的漏電流。隨著工藝尺寸的減小,,邏輯門長度越來越短,,這些漏電流在增大,如圖3 所示,。

圖3. 靜態(tài)功耗隨著工藝尺寸的減小而顯著增大

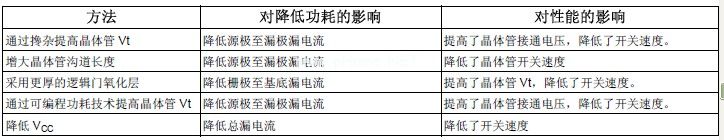

Altera 主要采用5 種方法來降低漏電流,,如表3 所示。

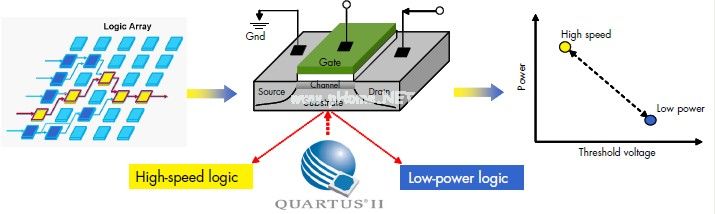

所有方法都對性能有影響,,使晶體管不能以最大速率工作,。然而, Altera 進行了明智的選擇,,在晶體管級以性能換取低功耗,,維持器件總體性能不變。通過分析除了上面介紹的5 種方法,, Altera 采用了其獨特的可編程功耗技術(shù)來降低靜態(tài)功耗,。這一專利功能內(nèi)置在Stratix IV 器件芯片中,使Quartus® II 開發(fā)軟件能夠根據(jù)設(shè)計要求,,改變晶體管Vt,,以平衡性能和功耗。圖4所示為可編程功耗技術(shù)的高級實現(xiàn),, Quartus II 軟件根據(jù)時序驅(qū)動的編輯功能分析用戶FPGA 設(shè)計,,選擇邏輯陣列中的哪些晶體管應(yīng)該采用高速模式,,哪些應(yīng)該采用低功耗模式。通過改變跨過反向偏置電壓的晶體管Vt,,減小了時序不重要通路上的晶體管泄漏( 增大Vt),,從而實現(xiàn)了低功耗,同時在需要的地方保持高性能不變,。

圖4. 可編程功耗技術(shù) (1) 通過設(shè)置晶體管反向偏置,,平衡了功耗/ 性能。

注釋:

(1) 這是可編程功耗技術(shù)非常簡單的“模型”,。實際情況各種各樣,,并擁有專利。

為降低器件的動態(tài)功耗,,在40-nm 器件上,, Altera 將以前器件系列使用的1.1V 內(nèi)核電壓降到了0.9V。晶體

管開關(guān)期間消耗的功率與V2C ( 其中,, C 是電容) 成正比,,因此,降低供電電壓會導(dǎo)致動態(tài)功耗按平方比

例下降,。

減小內(nèi)核電壓也會影響晶體管性能,,但是Altera 再次利用了40-nm 節(jié)點的高性能特性來保持器件級性能不變。如前所述,,和以前的工藝節(jié)點相比,, Altera 在40-nm 節(jié)點某些晶體管上具有更強的驅(qū)動能力, IC 設(shè)計人員能夠在驅(qū)動能力和降低功耗上達到平衡,。

此外,, Altera 在其收發(fā)器上降低了每個發(fā)送器和接收器通道的功耗,,進一步降低了總功耗,。Altera Stratix

IV FPGA還通過動態(tài)片內(nèi)匹配(OCT) 技術(shù)降低了有功功耗。采用動態(tài)OCT后,,可以根據(jù)需要來接通或者關(guān)斷Altera 器件中的匹配電阻,。在存儲器讀/ 寫周期中,關(guān)斷不需要的匹配電阻,,去掉了電阻上的壓降,,對于72 位接口,功耗能夠降低1.2 瓦,。

表3. Altera 降低漏電流采取的方法對降低功耗的影響對性能的影響通過攙雜提高晶體管Vt 降低源極至漏極漏電流提高了晶體管接通電壓,,降低了開關(guān)速度。增大晶體管溝道長度降低源極至漏極漏電流降低了晶體管開關(guān)速度采用更厚的邏輯門氧化層降低柵極至基底漏電流提高了晶體管Vt,,降低了開關(guān)速度,。通過可編程功耗技術(shù)提高晶體管Vt 降低源極至漏極漏電流提高了晶體管接通電壓,,降低了開關(guān)速度。降低VCC 降低總漏電流降低了開關(guān)速度

總之,, Altera 在Arria II GX 器件上采取低功耗技術(shù)后,,實現(xiàn)了帶有3.75-Gbps 收發(fā)器、功耗最低的FPGA,,其功耗比競爭器件低65%,。對于Stratix IV FPGA,采取低功耗措施后,,和65-nm Stratix III FPGA 中實現(xiàn)的相似設(shè)計相比,,總功耗( 待機功耗 + 動態(tài)功耗) 平均降低了30%。

從技術(shù)領(lǐng)先到平穩(wěn)提高產(chǎn)量成功推出首款40-nm FPGA 是非常重要的事件,,但是Altera 的目標(biāo)不止于此,,還要象以前工藝節(jié)點產(chǎn)品那樣,實現(xiàn)高質(zhì)量可靠交付,。通過努力,, Altera 依靠其可靠的開發(fā)實踐,包括強大的測試芯片計劃,、嚴格的器件檢驗程序以及在提高產(chǎn)量上的獨特優(yōu)勢,,獲得了極大的成功。所有這些方面都得到了業(yè)界堅實的代工線合作伙伴的有力支持,。

Altera 的代工線合作伙伴TSMC 是代工線市場的領(lǐng)先者,。在專業(yè)代工線領(lǐng)域,TSMC 占據(jù)了50%以上的世界市場份額,,年度研究和開發(fā)投入超出最相近競爭對手55%,。這些投入使TSMC 在光刻和可生產(chǎn)性設(shè)計(DFM) 方面占據(jù)了業(yè)界領(lǐng)先位置,進一步保證了TSMC 能夠成功交付高級工藝節(jié)點產(chǎn)品,。最重要的是,,在40-nm 節(jié)點, TSMC 是浸入式光刻技術(shù)的領(lǐng)先者,,該工藝結(jié)合光刻透鏡和清澈液體,,透過分辨率更高的光線,實現(xiàn)了更小,、封裝更緊湊的器件,。浸入式光刻是大部分半導(dǎo)體公司開發(fā)45-nm 節(jié)點及后續(xù)節(jié)點技術(shù)所選用的工藝,普遍認為也是32-nm 節(jié)點要采用的技術(shù),。

和TSMC 一起,, Altera 積極組織了多個聯(lián)合工藝開發(fā)團隊,以解決工藝開發(fā)面臨的各種問題,,包括功耗/性能,、建模,、測試芯片規(guī)劃、存儲器,、可靠性,、聚乙烯熔絲、DFM,、RF/ 模擬,、ESD 和封裝等。所有團隊在雙方產(chǎn)品交付和先進性上達成一致,,精誠合作,,堅持到底。

業(yè)界最可靠的測試芯片技術(shù)Altera 的實踐表明,,在130nm,、90nm 和65-nm 器件生產(chǎn)中,對于新半導(dǎo)體工藝體系結(jié)構(gòu)和器件特性的早期評估以及精細加工,,測試芯片技術(shù)是非常有價值的工具,。這一策略使Altera 的器件產(chǎn)量穩(wěn)步上升,已經(jīng)證明是可編程邏輯行業(yè)最具特色的一點,。在40-nm 節(jié)點,, Altera 以可靠的9 種測試芯片計劃為其最新一代產(chǎn)品獲得成功再次建立了強大的基礎(chǔ)。

由于需要大量的模板,,采用測試芯片意味著較大的投入,。Altera 與TSMC 密切合作,保持了工藝效率,,降低了成本,。例如, TSMC 自己制造大量的測試晶片,,全面進行特性測試,,調(diào)整制作方法,然后監(jiān)控產(chǎn)品,。

通過密切合作,,在代工線晶片早期階段實現(xiàn)了“背負式”測試結(jié)構(gòu),,縮短了Altera 產(chǎn)品投產(chǎn)時間,,使客戶能夠盡早使用最先進的技術(shù)。同樣的,,在Altera 的幫助下,, TSMC 能夠有機會使用其模板進行更多的測試。結(jié)果對雙方都有好處,。

通過采集并分析測試芯片數(shù)據(jù),, Altera 深入研究了各種隨機和系統(tǒng)偏差的影響,,開發(fā)設(shè)計策略來降低甚至消除這些不利影響。Altera 在測試芯片上的大量投入幫助客戶避免了前沿半導(dǎo)體設(shè)計中的風(fēng)險,。對風(fēng)險管理的關(guān)注展示了Altera 在可靠交付新技術(shù)產(chǎn)品上的承諾,, Altera 不會中斷或者以有限的產(chǎn)量向客戶供貨,也不會提供達不到要求的產(chǎn)品,。

系統(tǒng)檢驗過程

除了測試芯片階段以外,, Altera 還在開發(fā)和生產(chǎn)階段進行嚴格的檢驗,確保所有芯片產(chǎn)品符合設(shè)計要求,。檢驗過程包括以下步驟:

1. Altera 的IC 設(shè)計團隊進行大量仿真,,包括統(tǒng)計手段,確保設(shè)計達到功能,、性能和功耗規(guī)范,。

2. 通過嚴格的檢驗程序,Altera CAD 和布局組確保設(shè)計完全符合Altera 和TSMC 的模板標(biāo)準(zhǔn),,成功實現(xiàn)設(shè)

計,。

3. 跨功能團隊對關(guān)鍵管芯區(qū)域進行可生產(chǎn)設(shè)計(DFM) 分析,保證能夠可靠生產(chǎn),。這涉及到仔細分析設(shè)計布

局,,利用工藝技術(shù)經(jīng)驗,去掉邊緣產(chǎn)品,,對布局進行優(yōu)化,,以實現(xiàn)最大產(chǎn)量。

在40-nm 工藝節(jié)點實現(xiàn)世界上最先進的定制邏輯器件Altera 公司

4. TSMC 保證了可靠的模板生產(chǎn),。大批量生產(chǎn)的最終產(chǎn)品不會出現(xiàn)模板尺寸邊緣和缺陷導(dǎo)致的產(chǎn)量或者功能問題,。

5. Altera 與TSMC合作,確保芯片能夠按要求制造,,符合所有相應(yīng)的線內(nèi)物理規(guī)范(層厚度,、線寬等)和端線電氣規(guī)范( 晶體管特性、金屬線阻抗等),。

6. Altera 產(chǎn)品工程組在晶片級和封裝單元級進行全套的特性測試,,確保最終產(chǎn)品符合所有規(guī)定的功能、性能和功耗規(guī)范,。他們還分析非功能單元,,與Altera 其他團隊一起確定產(chǎn)量下降的原因,反饋給TSMC,,進行改進,。

7. Altera 的應(yīng)用組從用戶角度來測試器件,驗證所有的器件特性,使用Quartus II 軟件開發(fā)配置文件,,對器件進行編程,,測試I/O 電壓電平,檢驗所有結(jié)構(gòu)單元的功能,。

8. Altera 可靠性測試組負責(zé)測試芯片和最終產(chǎn)品,,在嚴格的環(huán)境中進行測試,在最終發(fā)售給客戶之前,,確保最終產(chǎn)品的短期和長期質(zhì)量,。

Altera 的每一新器件系列均采用了這一流程,并不斷進行改進,。在所有產(chǎn)品中采用這些嚴格的測試和檢驗流程,, Altera 保證了產(chǎn)品具有最好的質(zhì)量、可靠性以及可用性,。

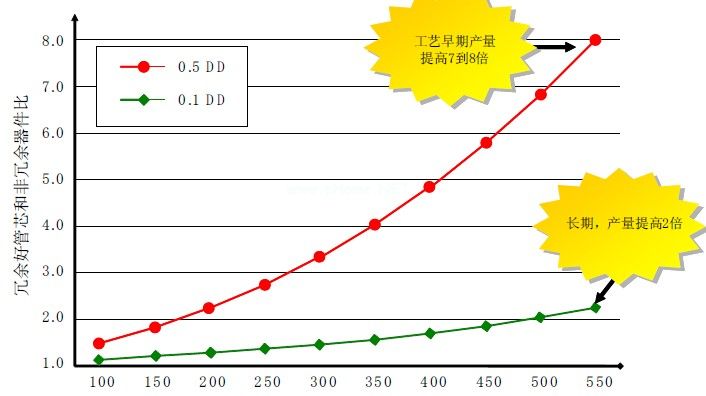

獨特的冗余技術(shù)提高了器件產(chǎn)量Altera 是唯一使用專利冗余技術(shù)的可編程邏輯供應(yīng)商,。在提高器件產(chǎn)量和器件可用性上,冗余是非常有效的方法,。Altera 在其FPGA 中嵌入“冗余”列電路來實現(xiàn)這一技術(shù),。如果確定某一列存在制造缺陷,利用電熔絲停止使用該列,,激活冗余列,。這一技術(shù)保留了管芯,從而提高了硅晶片的總產(chǎn)量,。

在工藝或者器件使用的早期階段,,較大的管芯更容易受到缺陷的影響,因此,,冗余技術(shù)對大管芯更有效,。在大管芯器件中采用冗余技術(shù)能夠?qū)a(chǎn)量提高8 倍。通過這種方式,,冗余技術(shù)提高了工藝早期的產(chǎn)量,,迅速降低了成本,提高了可用性,。隨著制造工藝的成熟和缺陷密度的增大,,冗余技術(shù)將繼續(xù)扮演重要角色,幫助Altera 在今后繼續(xù)提高產(chǎn)量( 如圖5 所示),??傮w上,冗余技術(shù)在Altera 目前的產(chǎn)品質(zhì)量中發(fā)揮了關(guān)鍵作用,,使Altera 能夠比其他可編程邏輯供應(yīng)商更迅速的提供大批量質(zhì)量可靠的產(chǎn)品,,特別是高密度產(chǎn)品,。

圖5. 在產(chǎn)品生命周期中,,冗余技術(shù)實現(xiàn)了更高的產(chǎn)量,。

Altera 保證當(dāng)前規(guī)范下的半導(dǎo)體產(chǎn)品性能與Altera 標(biāo)準(zhǔn)質(zhì)保一致,但是保留對產(chǎn)品和服務(wù)在沒有事先通知時的變更權(quán)利,。除非與Altera公司的書面條款完全一致,,否則Altera 不承擔(dān)由使用或者應(yīng)用此處所述信息、產(chǎn)品或者服務(wù)導(dǎo)致的責(zé)任,。Altera 建議客戶在決定購買產(chǎn)品或者服務(wù),,以及確信任何公開信息之前,閱讀Altera 最新版的器件規(guī)范說明,。

101 Innovation Drive

San Jose, CA 95134

www.altera.com

在40-nm 工藝節(jié)點實現(xiàn)世界上最先進的定制邏輯器件Altera 公司在這些技術(shù)的支持下,,以及以前節(jié)點的良好記錄——所有90-nm 器件按計劃交付,世界上首款低成本65-nm FPGA,,Cyclone III 系列在投片后三個月交付,,由此,Altera 能夠可靠的交付40-nm 產(chǎn)品,。Altera 在65nm上的記錄,,以Cyclone III FPGA為代表,在TSMC兩條啟動不到一年的300-mm GigaFabs上進行生產(chǎn),,這表明Altera 可以平穩(wěn)的進行量產(chǎn),。

結(jié)論

40-nm 工藝帶來了新的設(shè)計挑戰(zhàn),在這方面出現(xiàn)錯誤的代價非常高,。每一代產(chǎn)品的模板成本會增加50%,,在40-nm 節(jié)點高達3 百萬美元。同樣重要的是,,由于邏輯門數(shù)量和芯片復(fù)雜度的提高,,設(shè)計成本也隨之增加,而且比模板成本增加得更快,。這些困難把大部分公司擋在了40-nm 設(shè)計之外,,只有少數(shù)企業(yè)能夠在這一節(jié)點展開設(shè)計。而Altera 的業(yè)務(wù)模式使其能夠采用最先進的半導(dǎo)體工藝進行大量的投入來開發(fā)產(chǎn)品,,并推向市場,。Altera經(jīng)過在規(guī)劃和開發(fā)上多年的努力,并通過與業(yè)界領(lǐng)先獨立代工線的協(xié)作,,最終獲得成功,, Altera 的Arria IIGX FPGA、Stratix IV FPGA和HardCopy IV ASIC 系列最早實現(xiàn)了40-nm技術(shù)的廣泛應(yīng)用,,這是其他企業(yè)目前還做不到的,。結(jié)果, Altera 客戶能夠通過最先進的定制邏輯產(chǎn)品來滿足當(dāng)今系統(tǒng)設(shè)計對功能、性能,、密度和功耗最迫切的需求,。