引 言

Leon2是GaislerResearch公司于2003年研制完成的一款32位、符合IEEE-1754(SPARCVS)結(jié)構(gòu)的處理器IP核。它的前身是歐空局研制的Leon以及ERC32。Leon2的目標(biāo)主要是權(quán)衡性能和價格、高的可靠性、可移植性、可擴展性、軟件兼容性等.其內(nèi)部硬件資源可裁剪(可配置)、主要面向嵌入式系統(tǒng),可以用FPGA/CPLD和ASIC等技術(shù)實現(xiàn)。Leon2處理器的片上資源如下:分離的指令和數(shù)據(jù)Cache、硬件乘法器和除法器、中斷控制器、具有跟蹤緩沖器的調(diào)試支持單元(DSU)、2個24位定時器、2個通用異步串口(UART)、低功耗模式、看門狗電路、16位I/O端口、靈活的存儲控制器、以太網(wǎng)MAC和PCI接口。Leon2的VHDL模塊可以在大多數(shù)綜合工具上進行綜合,可以在任何符合VHDL-87標(biāo)準(zhǔn)的仿真器上進行仿真;采用AMBA AHB/APB總線結(jié)構(gòu)的用戶設(shè)計新模塊,可以很容易加入到Leon2中,完成用戶的定制應(yīng)用。

Leon2在歐洲和美國都有眾多的應(yīng)用者;國內(nèi)航天部77l所和中科院國家天文臺等單位正在研制基于Leon2的應(yīng)用系統(tǒng)。為了使Leon2得到國內(nèi)業(yè)界的了解和進一步的應(yīng)用,本文將從Leon2的結(jié)構(gòu)、技術(shù)特點、軟硬件的開發(fā)過程和應(yīng)用實例等四個方面進行介紹。在技術(shù)特點中,主要介紹了它所遵循的SPARCV8規(guī)范、采用的AMBH2.0內(nèi)部系統(tǒng)總線協(xié)議、容錯設(shè)計方法和VHDL編程風(fēng)格等。

1 Leon2的結(jié)構(gòu)

圖1是Leon2的片上結(jié)構(gòu)框圖。整個系統(tǒng)結(jié)構(gòu)由AMBA AHB和APB支撐,連接著SPARC處理器、Cache系統(tǒng)及片上外設(shè)等設(shè)備。

(1)處理器單元

處理器單元由整數(shù)單元IU、浮點單元FPU、協(xié)處理器單元CP構(gòu)成。整數(shù)單元的特點有:5級指令流水、分離的數(shù)據(jù)和指令Cache、支持2~32個寄存器窗口、可選的4個觀察口寄存器、可配置乘法器、可選的16×16位MAC(40位累加器)、基2除法器。可支持的浮點處理器有GaislerResearch的GRFPU,Sun Microsystems的Meiko FPU或其他通用浮點處理單元。Leon2提供了一個通用的用戶可定義的協(xié)處理器,同IU并行運行增強了系統(tǒng)功能。

(2)Cache子系統(tǒng)

可配置的模式有直接映射模式和2~4組相聯(lián)的多組相聯(lián)模式;可選的三種替換算法是LRU、LRR和偽隨機。

(3)片上外設(shè)

片上外設(shè)包括:2個中斷控制器、2個UART、2個Timer和1個Watchdog、16位的I/O口、存儲器控制器(PROM、SRAM、S13RAM)、PCI橋接器、Ethernet接口、高級片上調(diào)試支持單元(DSU)和跟蹤緩沖器等.中斷控制器可以最大處理46個內(nèi)部和外部中斷。2個串行通信口 (UART),支持8位數(shù)據(jù)幀、1位校驗位、1位停止位,支持硬件流控功能。調(diào)試支持單元(DSU)能夠把處理器設(shè)置到調(diào)試模式,通過它可以讀寫處理器的所有寄存器和Cache。DSU還包括一個跟蹤緩存,可以保存已執(zhí)行了的指令和AHB上傳輸?shù)臄?shù)據(jù)。

2 Leon2的技術(shù)特點

Leon2的技術(shù)特點主要有:采用SPARCV8結(jié)構(gòu)、采用內(nèi)部AMBA總線結(jié)構(gòu)、容錯設(shè)計和VHDL編程風(fēng)格。

2.1 SPARC V8

SPARC是可擴展處理器體系架構(gòu)的首字母縮略詞,是一個從RISC派生出的CPU指令集結(jié)構(gòu)(ISA)。指令集結(jié)構(gòu)是指:定義了指令、寄存器、指令和數(shù)據(jù)存儲器、指令執(zhí)行對寄存器和存儲器的影響、控制指令執(zhí)行的算法等內(nèi)容,但不定義時鐘周期、每條指令的執(zhí)行時鐘周期數(shù)(CPI)、數(shù)據(jù)通路等內(nèi)容。作為一個結(jié)構(gòu),SPARC允許在具有不同性能價格比的廣泛應(yīng)用中,實現(xiàn)不同系列的芯片和系統(tǒng),包括科學(xué)、工程、編程、實時和商業(yè)應(yīng)用等。SPARC的設(shè)計目標(biāo)是優(yōu)化編譯器和易于硬件流水線實現(xiàn)。

SPARC處理器由整數(shù)單元(IU)、浮點和協(xié)處理器單元(FPU和CP)構(gòu)成。它們各自都有自己的寄存器,其中IU有8個全局寄存器、2~3N個寄存器窗口(由用戶設(shè)定),浮點和協(xié)處理器單元的選擇依賴于具體應(yīng)用。

(1)寄存器窗口

它是SPARC的最大技術(shù)特點。SPARC處理器包括兩種寄存器:一種是通用寄存器,另一種是控制/狀態(tài)寄存器。IU的通用寄存器叫r寄存器。一個IU的實現(xiàn)可能包括40~520個32位r寄存器。這些寄存器又被分成8個全局寄存器,再加上2~32個與實現(xiàn)有關(guān)的16位寄存器組,每一個寄存器組又進一步分為8個輸入寄存器和8個輸出寄存器。圖2是一個8窗口寄存器結(jié)構(gòu)示意圖。在任何一個時刻,一條指令只能訪問8個全局寄存器和由當(dāng)前窗口指針(CWP)指定的當(dāng)前窗口。這個窗口是由8個輸入寄存器、8個局部寄存器和8個輸入寄存器構(gòu)成。從圖2中可以看出,兩個相鄰窗口的入和出寄存器是共享的。當(dāng)前是按窗口號順序(或前或后)轉(zhuǎn)換的,正好上一次的輸出寄存器成為當(dāng)前窗口的輸入寄存器,這樣可以減少存儲器讀寫和運行時的現(xiàn)場保護。

(2)支持的數(shù)據(jù)格式

基本有三種:8/16/32/64位有符號整數(shù)、8/16/32/64位無符號整數(shù)、32/64/128位浮點數(shù)。浮點數(shù)格式符合ANSI/IEEE Standard 754-1985。

(3)Traps

它是一種矢量化的、通過一個包含每個陷阱句柄的前4條指令的特殊陷阱表,將控制轉(zhuǎn)向監(jiān)視軟件。陷阱種類有精確陷阱、延遲陷阱和中斷陷阱。

(4)指令集

所有指令都編碼成32位格式,可以分成六個基本的類型,一共有72條指令。六種基本的指令分別是:①Load/store;②Arthmetic/logical/shift;③Control transfer;④Read/write control register;⑤Floating-point operate;⑥Coprocessor operate。

(5)存儲器模式

SPARC的存儲器模型定義了存儲器操作的語義,指定了處理器發(fā)射出這些操作的順序與這些指令被存儲器執(zhí)行的順序是如何進行關(guān)聯(lián)的。標(biāo)準(zhǔn)的存儲器模型叫作TSO(Total Store Ordering),所有的SPARC實現(xiàn)必須提供這個模型;另一個模型叫作PSO,它可以提供更高性能的存儲系統(tǒng)。

2.2 AMBA

AMBA(Advanced Microntroller Bus Architecture)規(guī)范,是一種已制定的、開放的規(guī)范,充當(dāng)著SoC設(shè)計的架構(gòu),正迅速成為SoC和IP庫開發(fā)事實上的標(biāo)準(zhǔn),為高性能嵌入式微控制器設(shè)計定義了一種片上通信標(biāo)準(zhǔn).AMBA規(guī)范中定義了三種不同的總線,即AHB、ASB和APBAHB是為高性能、高時鐘頻率的系統(tǒng)模塊提供的,擔(dān)任著高性能系統(tǒng)的背板總線、支持多處理器、片上各種存儲器和片外外部存儲器接口連接到低功耗輔助宏單元。ASB也是為高性能系統(tǒng)模塊提供,當(dāng)AHB的高性能特點無需要時,就可以用ASB來代替;它也支持多處理器、片上各種存儲器和片外外部存儲器接口連接到低功耗輔助宏單元。APB是為低功耗的外圍設(shè)備提供的,它優(yōu)化到為最小功耗和減小接口的復(fù)雜性來支持輔助功能。

圖3是AMBA總線微控制器的典型結(jié)構(gòu)。它含有一套高性能的背板總線,AHB或ASB;它能支撐外部存儲器帶寬,在這套總線掛接著CPU、片上存儲器和其他DMA設(shè)備。通過一個橋接器,可以把AHB和APB總線連接起來。APB上面連接著大多數(shù)的輔助設(shè)備,如UART、定時器、PIO等。

2.3 容錯問題

為了適用于航空航天的高可靠性應(yīng)用,Leon2采用多層次的容錯策略;奇偶校驗、TMR(三模冗余)寄存器、片上EDAC(檢錯和糾錯)、流水線重啟、強迫Cache不命中等.盡管現(xiàn)在幾乎所有CPU都有一些常規(guī)的容錯措施,如奇偶校驗、流水線重啟等,像IBM S/390 G5還采用了寫階段以前的全部流水線復(fù)制技術(shù).IntelItanium采用的混合ECC和校驗編碼等技術(shù);但遠沒有Leon2那樣,采用如此全面的容錯措施。

Leon2將時序(存儲)單元的狀態(tài)翻轉(zhuǎn)作為數(shù)字容錯的主要內(nèi)容,根據(jù)時序邏輯的不同特點和性質(zhì),采用了不同的容錯技術(shù)和手段.

①Cache的容錯。大的Cache對高性能CPU來說是至關(guān)重要的,而且位于處理器的關(guān)鍵(時間)通路上。為了減少復(fù)雜性和時間開銷,錯誤檢測的方法采用2位的奇偶校驗位,l位用作奇校驗,l位偶校驗,因此可以檢查所有的錯誤情況,在讀Cache的同時進行校驗。當(dāng)校驗出錯誤,強制Cache丟失,并從外部存儲去獲取數(shù)據(jù)。

②處理器寄存器文件的錯誤保護。寄存器文件是處理器內(nèi)部的寄存器堆,內(nèi)部的寄存器對于指令的運行速度和用戶程序設(shè)計的靈活程度都是很重要的。內(nèi)部寄存器的使用頻率很大,其狀態(tài)的正確性是也很關(guān)鍵。Leon2采用1、2奇偶校驗位和(32.7)BCH校驗和進行容錯。

③觸發(fā)器的錯誤保護。處理器的2500個觸發(fā)器均采用三模冗余的方式進行容錯,通過表決器來決出正確的輸出。

④外部存儲器的錯誤保護。采用掛上的EDAC單元實現(xiàn)。EDAC:采用標(biāo)準(zhǔn)的(32.7)BCH碼,每32位字可糾正1位錯誤和檢測2位錯誤。

⑤主檢測模式。是指兩個相同的處理器同時并行執(zhí)行相同的指令,只讓其中的主模式處理器輸出結(jié)果,不讓檢測模式的處理器輸出結(jié)果。在內(nèi)部,將檢測模式處理器的輸出同主模式處理器輸出進行比較,以檢查錯誤是否存在。這種工作模式,可以應(yīng)用于要求更高可靠性的情況。

⑥在軟件上,還要考慮Cache的清洗問題。因為上面介紹的五種方法,只有在對相應(yīng)的單元進行訪問時才進行錯誤檢查。如果存儲單元的數(shù)據(jù)不常使用,這些單元的錯誤會逐漸增加,因此必須使用一些軟件的方法來實現(xiàn)。

2.4 編碼風(fēng)格

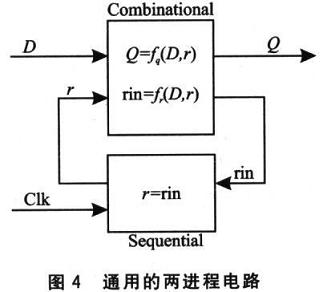

Leon2的VHDL編碼風(fēng)格,同傳統(tǒng)以并發(fā)執(zhí)行的并發(fā)進程(或并發(fā)語句)作為模塊、所謂的“數(shù)據(jù)流”編碼風(fēng)格不一樣,采用的是“二進程”的設(shè)計方法。這種編碼風(fēng)格克服了“數(shù)據(jù)流”編碼方式的可讀性差、抽象級低、仿真時間長等缺點。“二進程”編碼風(fēng)格的具體措施是:①所有的端口和信號聲明采用記錄的形式進行說明,如按輸入輸出分類進行記錄說明;②每個實體只有兩個進程,一個組合進程和一個時序進程;③在組合進程中全部采用變量(而不是信號),以使用結(jié)構(gòu)化的順序編碼方式;④在時序進程中通過時鐘同步,進行狀態(tài)的轉(zhuǎn)換。

“二進程”的編碼風(fēng)格的模型可用圖4來表示。它基本與狀態(tài)機模型一樣,只是組合進程部分,采用變量形式進行結(jié)構(gòu)化順序編碼,來完成下一個時鐘周期的輸出和下一個狀態(tài)進行計算。時序進程部分是在時鐘的作用下,完成狀態(tài)轉(zhuǎn)換和輸出驅(qū)動。

3 軟硬件開發(fā)

3.1 VHDL

Leon2除了VHDL源代碼外,還提供了頂層Makefile文件、Modelsim仿真器支持文件、Boot-monitor文件、VHDL測試文件、綜合支持文件、Leon2調(diào)試用的C語言源文件等,便于對Leon2進行硬件和軟件方面的測試。

Leon2的內(nèi)部結(jié)構(gòu)可以通過模塊配置,使處理器具有不同的功能結(jié)構(gòu)。配置的方式可以采用tkconfig腳本進行圖形界面的方式進行,也可以直接對包文件device.vhd進行手動編輯來完成。配置主要是通過修改一系列的常數(shù)的聲明值來實現(xiàn)的。Leon2中許多模塊功能是可以進行配置的,這些配置信息是在包文件Target.vhd里進行聲明的。

Leon2可配置的內(nèi)容包括:①所采用的綜合工具和目標(biāo)庫。綜合的技術(shù)可以是:Synplify、Synopsys-DC、Synopsys-FC2、XST和Leonardo等,目標(biāo)技術(shù)可以是Xilinx的Virtex和Virtex II(FPGA)、Atmel的ATC35和ACT25(0.35/0.25μm CMOS)、TSMC 0.25μm CMOS、UMC 0.25/0.18μm CMOS、以及Actel的ProAsie(FPGA)和Axeellerator(反熔絲FPGA)等。②整數(shù)單元IU的寄存器窗口、乘法器、除法器、快速跳轉(zhuǎn)和觀察點的配置。寄存器窗口可以設(shè)置為2~32個,但為了同交叉編譯器LECCS兼容必須配置為8個窗口,乘法器可以配置成迭交、16×16加流水寄存器、16×16、32×8.32×16、32×32等形式。③浮點處理單元FPU的配置,可以配置為使用meiko或是lth兩種浮點處理器之一。④Cache。Cache組的有效大小可以配置為1~64 KB,但必須是2的次冪,每行可以設(shè)置成4~8個字,組的數(shù)量可以是1~4。替換算法可以是隨機、LRR或LRU,并且指令Cache和數(shù)據(jù)Cache是獨立進行配置的。⑤存儲器控制器。⑥D(zhuǎn)ebug配置。⑦片上外設(shè)的配置,如中斷控制器、看門狗等。⑧引導(dǎo)配置。⑨AMHB總線的相關(guān)配置。⑩PCI配置。

Leon2有四個可綜合的頂層文件;

◇leon.vhd一一標(biāo)準(zhǔn)的Leon2頂層;

◇leon_pci.vhd一一標(biāo)準(zhǔn)的Leon2加上PCI接口構(gòu)成的頂層;

◇leon_eth.vhd一一標(biāo)準(zhǔn)的Leon2加上一個10/100 Mbps以太網(wǎng)MAC構(gòu)成的頂層;

◇leon_etn_pci.vhd一一標(biāo)準(zhǔn)的Leon2加上一個10/100 Mbps以太網(wǎng)MAC以及PCI接口構(gòu)成的頂層。

在上述四個頂層的下面,可以很容易地集成用戶自己的功能模塊。

3.2 系統(tǒng)軟件開發(fā)

同一般的嵌入式系統(tǒng)的軟件開發(fā)一樣,Leon2應(yīng)用系統(tǒng)的軟件開發(fā)需要采用交叉編譯環(huán)境來進行。Leon2應(yīng)用系統(tǒng)軟件開發(fā)主要采用LECCS(Leon/ERC32 GUN交叉編譯系統(tǒng))。LECCS是由Cynus、OAR和Gaisler研究公司開發(fā)的多平臺開發(fā)系統(tǒng),是基于GNU系列的可以自由獲取的、并帶有一系列附加“點”工具的開發(fā)系統(tǒng)。LECCS可以在Linux(-2.2.x或更高)、Solaris(-2.7或更高)和windows(Cygwin-1.1.7更高)等多種平臺上運行。要在Windows平臺上運行LECCS,必須安裝Cygwin。它一個是Unix層面模擬器。

LECCS包括如下程序包:GCC--3.2.3C/C++編譯器、RTEMS--4.6.0-βC/C++實時核、獨立C庫、GDB-5.3SPARC交叉調(diào)試器、遠程調(diào)試監(jiān)視器、GDB的DDD圖形前端(僅對Unix)、GDB的GDB-TK圖像前端(僅對Windows)、引導(dǎo)PROM的builder以及Leon調(diào)試支持單元監(jiān)視器等。還包括一些工具,如交叉匯編器、匯編預(yù)處理器、GNU連接器、二進制轉(zhuǎn)換器等等。

采用LECCS進行Leon2應(yīng)用系統(tǒng)軟件開發(fā)的過程如下:

①利用GCC編譯和鏈接程序;

②利用仿真器了SIM調(diào)試程序;

③在遠程目標(biāo)系統(tǒng)上調(diào)試程序;

④為獨立應(yīng)用產(chǎn)生引導(dǎo)PROM程序。

LECCS支持兩種類型的應(yīng)用:一種是通常的順序CC++程序,一種是基于R了EMS核的多任務(wù)實時CC++程序。

軟件仿真工具可以采用丁SIM。它是一個通用的SPARC架構(gòu)仿真器,可以對基于ERC-32和Leon的計算系統(tǒng)進行仿真,性能和使用方法可以參見TSIM用戶指南。Leon2為應(yīng)用系統(tǒng)的調(diào)試在硬件上作了極大的支持,那就是它的調(diào)試支持單元(DSU)和跟蹤緩沖器。具體使用時可參見Leon2用戶手冊和leon DSU Monitor用戶手冊。

4 Leon2的應(yīng)用

Leon2在國內(nèi)外都有應(yīng)用。

國外應(yīng)用很多,如基于Leon的數(shù)字聽寫機、指紋安全系統(tǒng)、GPS處理機、BIST(內(nèi)建自測試)等方面的產(chǎn)品。這里簡單介紹洛杉磯加州大學(xué)的ThumbPod指紋安全系統(tǒng),以及Nemerix公司的NJ1030型GPS基帶產(chǎn)品。ThumbPod安全系統(tǒng),是將人的指紋作為身份認證(數(shù)字身份)的安全系統(tǒng)。其原型的硬件系統(tǒng)由Xilinx的FPGA(XC2V1000)、Micron的 256 MHz-DDR-SDRAM、Authentec的AF-S2型手指感應(yīng)器等構(gòu)成。CPU采用Leon2處理器核,并通過Leon2的協(xié)處理器接口(CPI)掛接了AES(高級加密系統(tǒng))協(xié)處理器來執(zhí)行AES算法,以加快加密速度.系統(tǒng)的最大工作時鐘頻率可以達100 MHz,工作電壓可以是3.3/2.5/1.8/1.5 V等多種電壓。NJl030型GPS基帶產(chǎn)品,目標(biāo)是GPS的L1載波C/A碼處理,并提供對WAAS和EGNOS兩種增強系統(tǒng)的支持,可以和世界上領(lǐng)先的第三方的GPS-RF前端設(shè)備兼容。

國內(nèi),航天部771所和中科院國家天文臺都正在或計劃研制基于Leon2的星載數(shù)據(jù)處理系統(tǒng)。這種數(shù)據(jù)處理系統(tǒng),不再采用體積大、笨重而又功耗巨大的處理器芯片(如DSP),而是直接將Leon2放進FPGA。系統(tǒng)將大部分的處理功能硬件化,利用FPAG的豐富資源,將整個系統(tǒng)放入一片F(xiàn)PGA芯片內(nèi)。其中的Leon2只進行控制管理和一些必須的計算處理。國家天文臺正計劃研制基于Leon2的星載系統(tǒng),系統(tǒng)將處理每日采集到的1780 GB數(shù)據(jù)。這些數(shù)據(jù)通過預(yù)處理(圖像積分、輻射校正、幾何校正、磁圖處理)、小波壓縮、圖像格式等,使圖像壓縮到10GB左右,并下傳到地面站。

結(jié) 語

本文介紹了Leon2開源處理核的技術(shù)特點、軟硬件開發(fā)過程、國內(nèi)外的應(yīng)用實例。技術(shù)特點主要是SPARCV8規(guī)范、AMBH2.0總線結(jié)構(gòu)、容錯設(shè)計方法和VHDL編程風(fēng)格;對Leon2應(yīng)用系統(tǒng)的軟硬件開發(fā)工具和方法進行了介紹;在應(yīng)用實例中,介紹兩種國外的應(yīng)用和兩種國內(nèi)的應(yīng)用,其中包括作者正在進行研制的星載圖像處理系統(tǒng)。