摘 要: 介紹了一個實用IGBT驅動信號轉換電路的CPLD設計,并給出了該設計的仿真波形,。

關鍵詞: PWM CPLD IGBT VHDL 自頂向下

?

隨著國民經濟的不斷發(fā)展,,變頻調速裝置的應用越來越廣泛。如何打破國外產品的壟斷,,已成為一個嚴肅的課題擺在我國工程技術人員的面前,。

在某型號大功率變頻調速裝置中,,由于裝置的尺寸較大,考慮到結構和散熱的條件,,主控板上DSP產生的PWM信號需經過較長的距離才能送到IGBT逆變單元中,。為保證PWM信號傳輸?shù)臏蚀_性和可靠性,必須解決以下幾個問題:首先是抗干擾問題(變頻器工作時,,IGBT的開關動作會產生高頻干擾信號);其次是如何保證PWM信號的前,、后沿質量,減少IGBT開關動作的過渡過程;最后是如何減少布線電感,,盡可能縮短PWM信號傳輸距離,,避免過多的內部連線。

1 總體設計

原則上說,,從觸發(fā)電路到IGBT柵極和發(fā)射極的引線應做到既短又一致,。但隨著變頻調速裝置功率的不斷增大,裝置的尺寸也在增大,,散熱條件要求更高,。由于結構設計上的種種原因,真正做到這點有很多實際困難,。

DSP產生的PWM信號既可以采用串行方式又能以并行方式進行傳輸,,但這兩種方式都有著各自的特點。采用并行方式傳輸信號(即每一個IGBT模塊的柵控端都接一根信號線)會造成系統(tǒng)內部接線過多,、接地困難,,抗干擾性大大降低,這種情況尤以采用了多重化,、多電平技術的變頻裝置為甚,。若利用串行方式,PWM信號的傳輸速率又受到介質的極大限制,。在目前諸多傳輸介質中,,只有光纖具有損耗低、頻帶寬,、重量輕,、不受電磁干擾等突出優(yōu)點。GI型光纖用LED做光源時,,傳輸速率可達140Mbit/s,,傳輸損耗可忽略不計。IGBT的工作頻率通常很少用在15kHz以上,,因此以異步串行方式高速傳輸PWM信號時,,采用光纖作為傳輸介質是唯一的選擇。

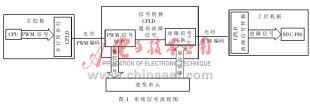

在串行的PWM信號送到IGBT的柵控端之前,,還需將該信號轉化為并行形式,。盡管采用普通的串/并轉換芯片可以實現(xiàn)上述功能,但這些芯片的最高工作頻率有限,,如74166的最高工作頻率為35MHz,,對于目前廣泛采用多重化和多電平技術的變頻裝置來講,這種工作頻率顯然有著較大的局限性,。尤其是在實時性,、快速性要求甚高的電機控制領域,不可能采用應答方式完成信號的傳輸,,因此接收端需要有較強的糾錯和容錯能力,。若采用普通的芯片,難以只用一兩片芯片完成上述功能,。但CPLD具有極強的靈活性,,內含128個宏單元,最高工作頻率可達167MHz(以Cypress CY37128為例),,可以只用一兩片芯片就能完成較復雜的邏輯功能,,因此CPLD與光纖的結合是解決大功率變頻器中信號傳輸?shù)淖詈眠x擇。系統(tǒng)信號流程圖如圖1所示,。

2 通訊方案

異步串行格式的一個數(shù)據(jù)幀包括1位起始位和8位數(shù)據(jù)位,,最后是停止位。起始位規(guī)定為0,,8位數(shù)據(jù)位由高到低順次發(fā)送,,前7位組成1個編碼字符,第八位為奇偶校驗位,。停止位可以選擇1位,、1![]() 位、2位,。從系統(tǒng)實際要求出發(fā),,我們對標準的異步串行格式進行了修改,將三相PWM信號進行編碼,,用以下數(shù)據(jù)格式發(fā)送到信號轉換單元:0-a3c3a2c2a1c1-V-1111,。其中0為起始位,a1,、a2,、a3分別對應三相逆變橋每個橋臂的柵控信號,,c1、c2,、c3分別對應三相逆變橋每個橋臂的封鎖信號,,V是一位校驗位,最后四個1為結束標志位,。信號轉換單元的CPLD接收到該信號后,,將此串行PWM信號轉換為并行形式。另一方面,,為保證逆變單元能夠正常工作,,還需將逆變單元故障信號送到上位機以供故障診斷。故障信號以以下串行編碼格式送出:0-a1a2a3a4a5a6-V-1111,,0為起始位,,a1、a2,、a3分別對應每個橋臂的驅動故障信號,,a4為過熱信號,a5,、a6為通訊故障信號,,V為校驗位,最后四個1為結束標志位,。上位機板上的CPLD將此信號轉換為并行形式,。事實上,PWM信號和故障信號的處理過程是相同的,。

位、2位,。從系統(tǒng)實際要求出發(fā),,我們對標準的異步串行格式進行了修改,將三相PWM信號進行編碼,,用以下數(shù)據(jù)格式發(fā)送到信號轉換單元:0-a3c3a2c2a1c1-V-1111,。其中0為起始位,a1,、a2,、a3分別對應三相逆變橋每個橋臂的柵控信號,,c1、c2,、c3分別對應三相逆變橋每個橋臂的封鎖信號,,V是一位校驗位,最后四個1為結束標志位,。信號轉換單元的CPLD接收到該信號后,,將此串行PWM信號轉換為并行形式。另一方面,,為保證逆變單元能夠正常工作,,還需將逆變單元故障信號送到上位機以供故障診斷。故障信號以以下串行編碼格式送出:0-a1a2a3a4a5a6-V-1111,,0為起始位,,a1、a2,、a3分別對應每個橋臂的驅動故障信號,,a4為過熱信號,a5,、a6為通訊故障信號,,V為校驗位,最后四個1為結束標志位,。上位機板上的CPLD將此信號轉換為并行形式,。事實上,PWM信號和故障信號的處理過程是相同的,。

對于異步串行通訊,,通常要保證發(fā)送的信號在接收端能被正確接收,往往采用兩類同步處理辦法:一類是使用硬件手段實現(xiàn)通信協(xié)議的部分功能,;另一類是使用各種短小的幀來實現(xiàn)通信功能,。在本系統(tǒng),由于實時控制對時間的要求,,不可能采用上述形式的通訊方案,。因此根據(jù)系統(tǒng)實際需要,數(shù)據(jù)傳輸采用起止式同步方案,,即用“0”代表起信號,,“1”代表止信號。在不發(fā)送信息時,,一直發(fā)送止信號,。第一個由“1”到“0”的轉換表示字符的開始收端檢測到這個轉換后控制位時鐘輸出,以便對接受信號進行碼位中點取樣判決,。

針對系統(tǒng)的實際要求,,為確保數(shù)據(jù)通訊的正確性,,在正常工作以前,DSP模塊必須向信號轉換單元固定發(fā)送一個標志字,。只有當信號轉換單元連續(xù)幾次正確收到標志字后,,才能建立正常通訊。在正常通訊時,,為避免隨機干擾的作用,只有在連續(xù)出現(xiàn)多次幀錯誤的情況下,,信號轉換單元才向上位機發(fā)出通訊故障信號,,以確保系統(tǒng)工作的穩(wěn)定性。

3 CPLD的實現(xiàn)

20世紀90年代,,引起數(shù)字系統(tǒng)設計方式發(fā)生突破性變革的技術是VHDL設計技術。VHDL [Very High Speed Integrated Circuit (VHSIC) Hardware Description Language]作為IEEE-1076標準所規(guī)范的硬件描述語言,,非常適用于可編程邏輯器件的應用設計,,并正在得以普及。采用自頂向下的設計方法,,是用VHDL設計系統(tǒng)硬件最突出優(yōu)點之一。

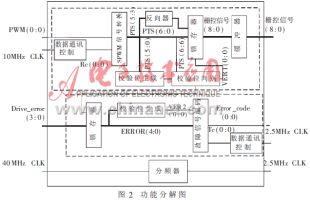

通過前面對數(shù)據(jù)流和通訊方案的分析,,按照自頂向下的原則,我們對信號處理單元進行功能分解,將其分解到下面的各個單元中,,見圖2。通過功能分解,,我們可以看到,單元內部構造可以分為三個部分:一部分對柵控信號進行處理,;另一部分對故障信號進行處理;最后一部分用于產生控制故障信號發(fā)送的時鐘,。

從圖2我們可以發(fā)現(xiàn)柵控信號處理部分與故障信號處理部分都含有功能相同單元:校驗位生成單元,、數(shù)據(jù)通信控制單元及鎖存單元,因此可以對以上這些單元進行參數(shù)化設計,。在參數(shù)化設計以前,我們還需要構造一些公共的基本元件,,如觸發(fā)器,、寄存器、計數(shù)器和同步器等,。這以后,,我們就可以對前面提到的功能相同的單元進行參數(shù)化設計。

在進行參數(shù)化設計以前,,我們需要對各功能單元的輸入輸出信號進行分析以確定信號使用的數(shù)據(jù)類型,。由于IGBT控制問題的特殊性,在這里我們統(tǒng)一使用Bit和Bit-vector型數(shù)據(jù),。Bit型數(shù)據(jù)只有兩種狀態(tài):“0”和“1”,,可以有效地防止多態(tài)數(shù)值系統(tǒng)給控制和編程帶來的麻煩。

在進行傳統(tǒng)的電子線路設計時,,設計師的工作是按電路原理圖將各個單元電路和器件連接起來,,形成一個完整的系統(tǒng)。而在利用VHDL設計電路時,,設計師所要完成的不過就是將那些用VHDL語言描述的單元電路和器件連接起來。在這個意義上,,利用VHDL語言進行設計與利用傳統(tǒng)方法設計沒有太大的區(qū)別,,但采用自頂向下的設計方法時,VHDL具有無可比擬的優(yōu)越性,。作為一種硬件描述語言, VHDL語言有別于一般的計算機語言,。它既有并行執(zhí)行的語句,,又有只能順序執(zhí)行的語句,。利用VHDL這種特性,我們可以將整個系統(tǒng)分成若干個相對比較獨立的模塊來進行電路設計,。在下面的程序中,進程COUNTER描述了一個16位計數(shù)器,,它通過對40MHz時鐘進行分頻,,產生進程CONTROLLER所需的2.5MHz時鐘,。進程CONTROLLER構造了一個發(fā)送控制計數(shù)器,它通過對進程COUNTER所產生的時鐘信號進行計數(shù),,產生故障信號的發(fā)送控制信號,。

CONTROLLER: PROCESS (reset, Tclk)

VARIABLE scit_v:BIT_VECTOR(5

DOWNTO 0):=″000000″;

BEGIN

IF (reset='0') THEN

scit_v:=″000000″;

ELSIF (Tclk'EVENT AND Tclk='1') THEN

IF(scit_v<=″000111″)THEN

IF(tdEMPTY_s='0')THEN

scit_v:=″001000″;

ELSE

scit_v:=″000000″;

END IF;

ELSE

scit_v:=scit_v+1;

END IF;

END IF;

scit<=scit_v;

END PROCESS;

COUNTER: PROCESS (clk, reset)

BEGIN

IF(reset='0') THEN

count_4<=″0000″;

ELSIF(clk'EVENTANDclk='1') THEN

count_4<=count_4+1;

END IF;

END PROCESS;

通過上面的程序,,對照圖2,我們可以看到整個設計分為三層:基本元件層-功能單元層-頂層,;用基本元件構成功能單元,,再由功能單元組成整個系統(tǒng),。每完成一個模塊的設計,,便對其進行仿真測試,逐步加入各個構造模塊,,模塊間通過一定的信號傳遞,,構成整個系統(tǒng)。采用這種方法,,仿真測試貫徹系統(tǒng)硬件設計的全過程,,從而可以在系統(tǒng)設計早期發(fā)現(xiàn)設計中存在的問題,。與傳統(tǒng)電路設計后期進行仿真相比可大大縮短系統(tǒng)的設計周期,節(jié)約大量的人力和物力,。

4 仿真與實驗結果

圖3是對上述芯片進行的仿真結果,,Data代表來自IGBT的故障信號,仿真時Data輸入值為“0101”,,即“5”,。由于通訊正常,a5a6為“11”,,因此上述六位產生校驗位為“1”,,Txd輸出為“0-1010110-1111”。Rxd輸入為“0-1101111-1111”,,Pcs(0,,2,4)三位輸出表達式為:aI AND cI ,,pcs(1,,3,,5)三位輸出表達式為:(NOT a1 )AND c1,,因此Pcs(0,1,,2,,3,4,,5)輸出為“011001”,,即“19”。通過對仿真結果的分析,,可以看到設計滿足功能需要,。該芯片已成功地用于某型號的大功率變頻調速裝置中。

通過上面的設計,,整個PWM信號與故障信號傳輸通路只需3片CPLD芯片就可實現(xiàn),。系統(tǒng)電路的體積大為縮小,從而提高了系統(tǒng)的可靠性。CPLD的應用縮短了系統(tǒng)的設計周期,,降低了開發(fā)成本,。CPLD與光纖的結合是解決PWM信號長距離傳輸中準確性和可靠性的有力保障。

參考文獻

1 張燕賓.SPWM變頻調速應用技術.北京:機械工業(yè)出版社,,1998

2 侯伯亨,,顧 新.VHDL硬件描述語言與數(shù)字邏輯電路設計(修訂板).西安:西安電子科技大學出版社,1997

3 Kevin Skahill.VHDL for programmable logic.Addison Wesley Longman,Inc.1996

4 郭梯云,劉增基,,王新梅等.數(shù)據(jù)傳輸.北京:人民郵電出版社,,1998