1 、引言

作為大型平板顯示設(shè)備的一種,LED 顯示屏以其使用壽命長、維護(hù)費(fèi)用低、功耗低等特點(diǎn)在顯示領(lǐng)域占有重要的位置。特別在近年,帶有紅、綠、藍(lán)三基色以及灰度顯示效果的全彩LED 顯示屏,以其豐富多彩的顯示效果而倍受業(yè)界關(guān)注,成為LED 顯示屏市場近年增長幅度比較大的產(chǎn)品。壽命、單位面積亮度、三基色的偏差程度、點(diǎn)距、對比度、灰度等級(包括灰度級數(shù)和線性度) 、掃描頻率等指標(biāo)性能是衡量或橫向比較大型顯示設(shè)備好壞的標(biāo)準(zhǔn)。而這些指標(biāo)性能的優(yōu)劣,很大程度上決定于掃描控制器的性能。因此對大屏幕全彩L ED 顯示掃描控制方法的研究有著重要的意義。

由于LED 的發(fā)光亮度與掃描周期內(nèi)的發(fā)光時間近似成正比,所以灰度等級的實(shí)現(xiàn)通常是由控制LED 的發(fā)光時間與掃描周期的比值,即采用調(diào)節(jié)占空比來實(shí)現(xiàn)的。全彩LED 顯示屏一般采用逐位點(diǎn)亮的掃描方式實(shí)現(xiàn)灰度圖像顯示。對于顯示灰度級數(shù)為8 位的LED 顯示屏,一般采用“19場掃描”原理來實(shí)現(xiàn)256 級灰度顯示。L ED顯示屏的顯示數(shù)據(jù)更新一般采用串行輸出方式,如采用595 進(jìn)行設(shè)計的靜態(tài)LED 全彩顯示屏,根據(jù)“19 場掃描”原理,對于分辨率等規(guī)格確定的屏體,當(dāng)串行移位時鐘確定時,顯示屏的刷新頻率和LED 的發(fā)光效率(一個掃描周期內(nèi),LED的最長點(diǎn)亮?xí)r間所占的比例) 也就被確定。本文提出了一種新的逐位點(diǎn)亮掃描方式,該方式對典型的“19場掃描”方式進(jìn)行了改進(jìn),可以在串行移位時鐘確定的條件下,在一定范圍內(nèi)對刷新率和發(fā)光效率進(jìn)行調(diào)節(jié),從而提高了產(chǎn)品根據(jù)實(shí)際的應(yīng)用環(huán)境和客戶要求進(jìn)行設(shè)計的靈活性。

2 、逐位點(diǎn)亮的灰度實(shí)現(xiàn)算法設(shè)計

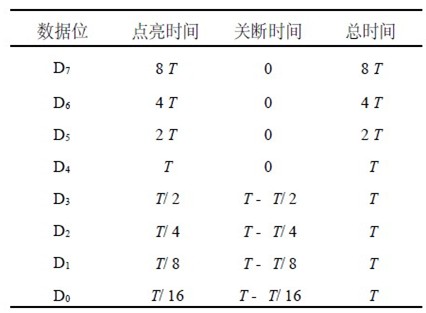

以8 位“19場掃描”理論為例,所謂逐位點(diǎn)亮,即從一個字節(jié)數(shù)據(jù)中依次從低位到高位或者從高位到低位提取出一位數(shù)據(jù),分8 次點(diǎn)亮對應(yīng)的像素,每一位對應(yīng)的點(diǎn)亮?xí)r間與關(guān)斷時間的占空比不同。如果點(diǎn)亮?xí)r間從低位到高位依次倍增,則合成的點(diǎn)亮?xí)r間將會有256 種組合。定義D0 位對應(yīng)的點(diǎn)亮?xí)r間加上關(guān)斷時間為一個時間單位,設(shè)為T ,可得表1 所示各位的點(diǎn)亮與關(guān)斷時間。

表1 “19場掃描”顯示時各位的點(diǎn)亮與關(guān)斷時間

在實(shí)際設(shè)計中, T也是對LED 顯示屏進(jìn)行一次串行數(shù)據(jù)更新所需要的時間。表1 所示的總時間是T 的整數(shù)倍,所以每個數(shù)據(jù)位所占用的總時間可以通過刷新一次屏幕數(shù)據(jù)來進(jìn)行定時。在進(jìn)行LED顯示屏設(shè)計時,整個顯示屏中LED 的亮與滅可以通過總控線EN 控制,當(dāng)點(diǎn)亮?xí)r間≥1 T時,EN 控制顯示屏處于常亮狀態(tài),而當(dāng)點(diǎn)亮?xí)r間< 1 T 時,可以通過控制EN 產(chǎn)生相應(yīng)占空比的控制波形來實(shí)現(xiàn)相應(yīng)位的亮度控制。可見,利用“19場掃描”原理,在串行移位時鐘和屏體具體規(guī)格確定的情況下,其刷新率也就被確定了,并且具有固定的發(fā)光效率η。

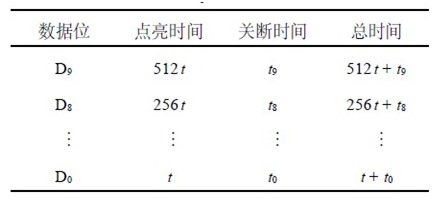

η =6 點(diǎn)亮?xí)r間6 總時間≈ 16 T19 T≈ 84 % (1)由灰度顯示的原理可以知道,能否實(shí)現(xiàn)灰度顯示,決定于各個數(shù)據(jù)位的點(diǎn)亮?xí)r間從低位到高位是否以2 的倍數(shù)遞增,而關(guān)斷時間的長短只會影響發(fā)光效率的大小。在進(jìn)行系統(tǒng)設(shè)計時,使用了8~10 位的非線性灰度校正,因此需要實(shí)現(xiàn)10位灰度掃描控制。定義“t”為點(diǎn)亮?xí)r間的一個時間單位,則可得表2 所示的時間分配。如果定義數(shù)據(jù)為“1”有效(點(diǎn)亮) “, 0”無效(熄滅) ,當(dāng)輸入數(shù)據(jù)從000H 到3FFH 變化時,點(diǎn)亮?xí)r間在0t~1 023t 變化,而亮度控制總時間則保持不變,從而實(shí)現(xiàn)了10 位占空比控制,采用這種灰度控制方法可以實(shí)現(xiàn)1 024 級的灰度顯示。與“19 場掃描”原理不同,本文控制點(diǎn)亮的時間不是通過屏幕刷新來實(shí)現(xiàn),而是采用單獨(dú)的計數(shù)器來進(jìn)行計時控制的。

表2 逐位點(diǎn)亮控制中各位數(shù)據(jù)點(diǎn)亮?xí)r間分配表

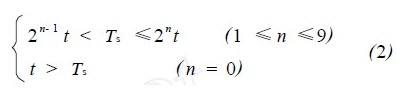

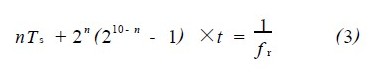

設(shè)使用串行方式更新整場視頻圖像一位數(shù)據(jù)所需要的時間為Ts ,如果Ts 滿足:

則完成一次串行數(shù)據(jù)更新所需要的時間在Dn - 1位所需要的點(diǎn)亮?xí)r間和Dn 位的點(diǎn)亮?xí)r間之間,這個時間也許小于一個時間t。由于串行數(shù)據(jù)更新時間和點(diǎn)亮?xí)r間可以部分重疊,設(shè)屏幕的刷新率(即顯示數(shù)據(jù)幀從顯示緩存讀出進(jìn)行屏幕顯示更新的頻率) 為f r ,可以得到式(3) 。

當(dāng)串行時鐘頻率和屏體參數(shù)確定, Ts 便可計算出來。此時,如果設(shè)定了屏幕的刷新率,結(jié)合式(2) 和式(3) ,對n 從0~9 進(jìn)行窮舉計算,可以得到同時滿足兩式條件的n 值,同時可以確定單位時間t 的值。由此得到的t 值,通過FPGA 進(jìn)行定時控制,便可實(shí)現(xiàn)一定刷新率的全彩灰度控制。

這里L(fēng)ED 的發(fā)光效率可以用式(4) 表示。

從式(3) 可知,當(dāng)串行移位時鐘頻率一定,即Ts 確定的情況下,刷新率f r 與單位時間t 成反比。而式(4) 表明,發(fā)光效率η和單位時間t 成正比。可見,刷新率和發(fā)光效率成反比關(guān)系,提高刷新率的同時必然要犧牲發(fā)光效率。因此,采用上述掃描方式,設(shè)計者可以根據(jù)實(shí)際應(yīng)用環(huán)境和客戶的要求在刷新率和發(fā)光效率兩者之間進(jìn)行適當(dāng)?shù)恼{(diào)整。

如果要求系統(tǒng)的全彩灰度控制符合“19 場原理”的顯示效果,則由表2 可得表3 所示的關(guān)斷時間t0 ~t9 的值。結(jié)合表3 中t0 ~ t9 的值,對表2中總時間各項進(jìn)行求和,便可得總時間為Ta =1 152t ,根據(jù)1 152t = 1/ f r 可得到t 值。

表3 逐位點(diǎn)亮控制中符合“19 場掃描”時各位數(shù)據(jù)關(guān)斷時間分配表在系統(tǒng)設(shè)計中,掃描板每個輸出端口分別控制16 ×48 分辨率的靜態(tài)顯示屏模塊,紅、綠、藍(lán)三色顯示數(shù)據(jù)采用3 根數(shù)據(jù)線分別輸出,串行移位時鐘頻率為6. 25 MHz ,顯示屏刷新頻率設(shè)計要求為120 Hz ,利用以上的結(jié)論可得:

Ts = 16×48×16125×106 s = 122188μs然后進(jìn)行窮舉計算,如表4 所示,可以得到單位時間t 的值為7. 780μs。

表4 對n 進(jìn)行窮舉計算得到單位時間t 的值根據(jù)式(4) ,可計算得到發(fā)光效率η = 1023tf r = 1023 ×71780 ×10- 6 s ×120Hz = 9515 %

3、 FPGA 電路設(shè)計

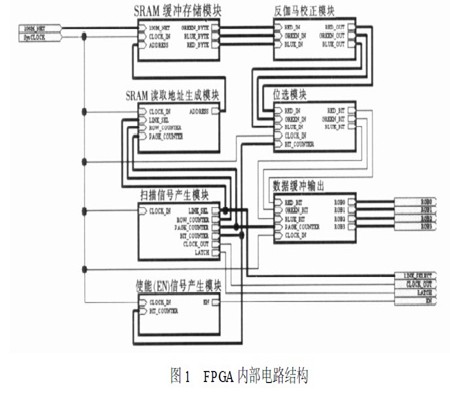

視頻圖像信號頻率高、數(shù)據(jù)量大,要求實(shí)時處理,加之全彩大屏幕LED 控制器實(shí)現(xiàn)的數(shù)字邏輯相當(dāng)復(fù)雜,采用CPLD/ FPGA 設(shè)計控制電路,可以簡化系統(tǒng)結(jié)構(gòu),便于調(diào)試。本文設(shè)計的掃描控制器應(yīng)用于大屏幕全彩LED 脫機(jī)視頻播放系統(tǒng)中。其中涉及到視頻信號的存儲和讀取、視頻數(shù)據(jù)的傳輸和接收、灰度顯示控制電路、LED 點(diǎn)陣顯示驅(qū)動電路等。本文主要對灰度顯示控制電路進(jìn)行討論,控制對象為以紅、綠、藍(lán)三色LED 組成的全彩靜態(tài)顯示屏。實(shí)現(xiàn)灰度顯示控制器的FPGA 內(nèi)部電路結(jié)構(gòu)如圖1 所示。

在LED 顯示屏掃描控制電路中,F(xiàn)PGA 是其中最主要的邏輯控制器件,主要實(shí)現(xiàn)視頻數(shù)據(jù)接收、非線性灰度校正和掃描信號產(chǎn)生功能。FP2GA 內(nèi)部各個電路模塊相互協(xié)調(diào)運(yùn)作,將數(shù)據(jù)輸入和顯示輸出連接起來,實(shí)現(xiàn)L ED 顯示屏的全彩視頻播放。

作為一個獨(dú)立的顯示系統(tǒng),普通的RS232 、RS485 總線方式已不能滿足L ED 顯示屏進(jìn)行多媒體視頻播放所要達(dá)到的高數(shù)據(jù)速率傳輸要求。以512 ×256 的全彩顯示屏為例,當(dāng)要求系統(tǒng)換幀頻率達(dá)到30 Hz 時,需要的數(shù)據(jù)傳輸速率高達(dá)94. 4 Mbp s。因此,在系統(tǒng)設(shè)計中,視頻數(shù)據(jù)的傳輸和接收采用RTL8201 設(shè)計的100 M 以太網(wǎng)控制器來完成。

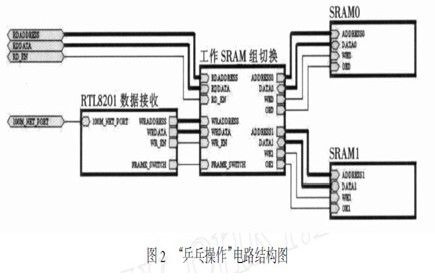

為了使視頻播放連續(xù)平滑,在數(shù)據(jù)接收過程中不能打斷顯示,這里采用兩組SRAM 進(jìn)行“乒乓操作”,使顯示數(shù)據(jù)的接收存儲和讀取能夠同時進(jìn)行, 從而實(shí)現(xiàn)視頻數(shù)據(jù)流的無縫緩沖和處理 , 如圖2 所示。換幀信號FRAME _SWITCH 是用來切換工作SRAM 組的,該信號決定兩組SRAM 哪一組處于讀狀態(tài),哪一組處于寫入狀態(tài)。RTL8201 數(shù)據(jù)接收模塊建立MII 接口,實(shí)現(xiàn)與RTL8201 的接口,把MII 接口傳送過來的半字節(jié)數(shù)據(jù)轉(zhuǎn)換成為24 位RGB 數(shù)據(jù),然后存儲在SRAM 里。RTL8201 每接收完一幀顯示數(shù)據(jù),則對換幀信號FRAME_ SWITCH 進(jìn)行求反,將兩組SRAM 的讀寫位置切換過來,使顯示屏顯示最新接收到的幀數(shù)據(jù),從而實(shí)現(xiàn)換幀操作。

由于LED 顯示屏包含4 列相互獨(dú)立的顯示模塊,因此掃描控制電路需要提供4 路RGB 數(shù)據(jù)輸出接口, 在圖1 中表示為RGB0 ~ RGB3 。

CLOCK_OUT 為移位時鐘信號輸出端口,RGB0~RGB3 在該時鐘的上升沿有效,各個端口的紅、綠、藍(lán)三色顯示數(shù)據(jù)通過時鐘脈沖信號分別逐位移入驅(qū)動芯片的顯示緩存。LA TCH 信號為串行數(shù)據(jù)輸出結(jié)束后需要進(jìn)行顯示刷新時的鎖存脈沖。EN 為灰度控制信號,當(dāng)EN 有效時,L ED 可以隨輸入數(shù)據(jù)的0 、1 狀態(tài)熄滅或者點(diǎn)亮,其有效時間寬度對應(yīng)為表2 所示的點(diǎn)亮?xí)r間。

EN 信號產(chǎn)生模塊為實(shí)現(xiàn)灰度圖像顯示的重要模塊,該模塊將輸入的位計數(shù)值轉(zhuǎn)換成為對應(yīng)位的點(diǎn)亮?xí)r間,并進(jìn)行相應(yīng)時間長度的亮度控制。

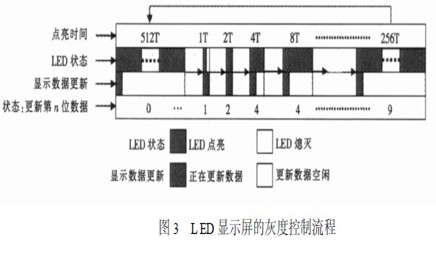

在本設(shè)計中,輸入的灰度信號為256 級,考慮到反γ非線性校正過程引起的灰度損失,將輸出的灰度級別定義為1 024 級,因此需要得到10 位灰度數(shù)據(jù)各個位對應(yīng)的點(diǎn)亮?xí)r間。依據(jù)“灰度實(shí)現(xiàn)原理”,10 位灰度數(shù)據(jù)各個數(shù)據(jù)位對應(yīng)的點(diǎn)亮?xí)r間從D0 ~D9 分別從1 T 倍增為512 T ,點(diǎn)亮總時間為1 023 T 。

由于驅(qū)動板中驅(qū)動芯片有二級緩存功能,所以更新數(shù)據(jù)和點(diǎn)亮L ED 這兩個控制過程可以部分重疊,從而得到圖3 所示的LED顯示屏灰度控制流程。更新第0 位數(shù)據(jù)時點(diǎn)亮?xí)r間為512 T 、更新第1 位數(shù)據(jù)時點(diǎn)亮?xí)r間為1 T ...依次類推,更新第n 位數(shù)據(jù)時,控制點(diǎn)亮的時間為上一次所更新的位所需要的點(diǎn)亮?xí)r間。

4、結(jié)論

討論了一種大屏幕全彩L ED 顯示屏設(shè)計的掃描控制器設(shè)計方案,通過對“19 場掃描”實(shí)現(xiàn)方法的分析,針對其不足之處,提出了一種新式的逐位點(diǎn)亮灰度控制方法。該控制方法使得在全彩LED 顯示屏的設(shè)計中,可以在L ED 的發(fā)光效率和刷新率之間進(jìn)行靈活的調(diào)整。本設(shè)計采用FP2GA 控制芯片為設(shè)計平臺來完成掃描控制電路的實(shí)現(xiàn),借助EDA 開發(fā)工具,降低了驅(qū)動電路的設(shè)計難度,縮短了項目的開發(fā)周期。