關(guān)鍵字:硬件設(shè)計;電壓測量;交流采樣;智能儀表

電力系統(tǒng)中電網(wǎng)電壓的測量與監(jiān)控影響電網(wǎng)系統(tǒng)調(diào)節(jié)和自動化管理。為實時監(jiān)控電網(wǎng)電壓,采用由微處理器控制的數(shù)字式測量儀表。在數(shù)字式測量初期,電網(wǎng)電壓測量大多采用整流后的直流量,但其測量精度直接受整流電路影響;整流電路參數(shù)調(diào)整困難,受波形因素影響較大;而交流采樣是按照一定規(guī)律采集被測信號的瞬時值,再用一定的數(shù)值計算法求得被測量的值。交流采樣取決于測量精度和測量速度。這里介紹一種基于交流采樣的電網(wǎng)電壓智能監(jiān)測硬件和軟件設(shè)計,可直觀準(zhǔn)確地反映電力系統(tǒng)的電能質(zhì)量。

2 系統(tǒng)硬件設(shè)計

2.1 系統(tǒng)硬件構(gòu)架

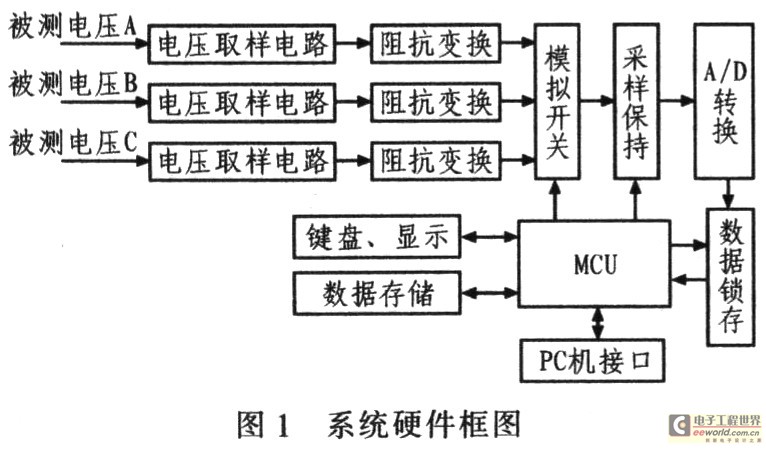

系統(tǒng)硬件電路由3部分組成:數(shù)據(jù)采集、單片機系統(tǒng)和接口,硬件框圖如圖1所示。

被測三相電壓分別加到取樣電路的輸入端,信號按比例變換后,再經(jīng)阻抗匹配網(wǎng)絡(luò),由16選1多路模擬開關(guān),采樣保持電路加到A/D轉(zhuǎn)換的輸入端。A/D轉(zhuǎn)換后的數(shù)據(jù)經(jīng)鎖存后輸入MCU,再由運算判斷被測電壓是否合格。同時,可將測量結(jié)果計入存儲器件。MCU通過對時鐘的操作,可實時將時間及測量結(jié)果顯示在VFD上,通過鍵盤調(diào)整時鐘。因系統(tǒng)中有存儲器件,可將歷史數(shù)據(jù)調(diào)出,在VFD顯示。可將測量儀通過PC機接口與微機連接,在微機上集中操作、監(jiān)控儀表。

2.2 系統(tǒng)電路設(shè)計

該儀表設(shè)計測量范圍為90~110 V,因此峰值電壓為![]() 通過匹配網(wǎng)絡(luò),峰值電壓變?yōu)?img border="0" height="44" src="http://files.chinaaet.com/images/20110924/7e7dd9f3-b11b-43aa-914b-c5de1e5d32f8.jpg" style="width: 109px; height: 44px" width="109" />所以,選取耦合線圈的初級與次級比為12:1,匹配網(wǎng)絡(luò)的輸出電壓則為-10~+10 V。

通過匹配網(wǎng)絡(luò),峰值電壓變?yōu)?img border="0" height="44" src="http://files.chinaaet.com/images/20110924/7e7dd9f3-b11b-43aa-914b-c5de1e5d32f8.jpg" style="width: 109px; height: 44px" width="109" />所以,選取耦合線圈的初級與次級比為12:1,匹配網(wǎng)絡(luò)的輸出電壓則為-10~+10 V。

采用輪詢方式設(shè)計,選用模擬多路開關(guān)器件CD4067B,分別選通3路被測電壓,通過同一測量電路分別測量3路。CD40-67B的輸入阻抗為50 Ω,其輸入端必須加匹配網(wǎng)絡(luò)。該器件輸入VP-P最大值為20 V,最大延遲時間60 ns。采樣保持電路采用LF398,該器件輸入VP-P最大值36V,滿足測量需求。A/D轉(zhuǎn)換器采用AD574A,該器件輸入電壓為+10 V,采樣位數(shù)為12位。采樣數(shù)據(jù)選用帶符號的二進制表示,最高位為符號位,后11位為數(shù)據(jù)位,采樣速度達35μs。AD574A可調(diào)節(jié)參考電壓,提高測量精度。經(jīng)A/D轉(zhuǎn)換后的數(shù)據(jù)經(jīng)74LS374鎖存后輸入MCU進行計算。MCU選用AT89C51,內(nèi)帶4KB片內(nèi)ROM,時鐘選用11.0592 MHz,可滿足計算需求。

時間參數(shù)采用HI1380串行時鐘記錄,該器件是帶有秒、分、時、月、年的串行時鐘保持器件,通過MCU操作該器件,可正確獲取時間參數(shù),用來統(tǒng)計電壓信息。電壓的統(tǒng)計信息保存在存儲器件內(nèi),方便調(diào)閱歷史信息。儀表使用24C64器件保存信息,該器件通過I2C總線完成操作,其容量為64 KB,可滿足記錄兩個月歷史信息的需求。

顯示部分使用16T202DAJ型VFD模塊,該模塊可用于字符操作,適合于儀表顯示。數(shù)據(jù)線選擇4位操作方式,通過MCU控制顯示時間、電壓信息及歷史信息。通過3個按鍵對MCU操作,可完成修改時間、調(diào)用歷史信息等操作。

接口使用SP490器件構(gòu)建,該器件為全雙工的RS-485電平收發(fā)器,通過與MCU的串口連接,可被PC機操作,從而實現(xiàn)儀表的遠程操作、集中監(jiān)控等功能。

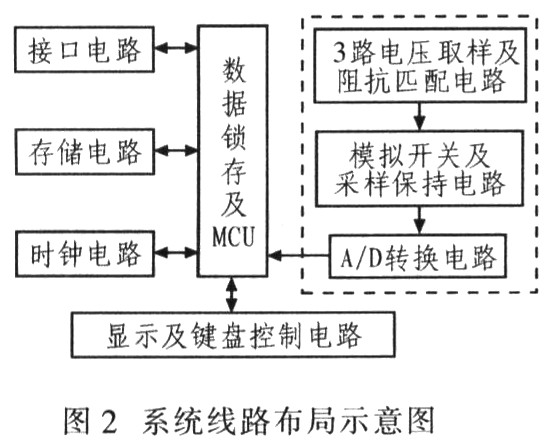

2.3 系統(tǒng)線路布局

圖2為系統(tǒng)線路布局示意圖。PCB板按信號流程布局,信號由機箱后面板輸入,經(jīng)過電壓采樣、模擬開關(guān)、采樣保持和A/D轉(zhuǎn)換后將輸入的模擬信號變?yōu)閿?shù)字信號。圖2中的虛線部分是模擬電路。

A/D轉(zhuǎn)換后的數(shù)字信號輸入MCU處理,MCU控制時鐘、存儲器件、顯示模塊操作和接口電路部分為純數(shù)字電路。儀表與PC機接口在機箱后面板,而顯示及鍵盤操作在機箱前面板。

要特別注意對電源的處理,數(shù)字電路的電源會干擾模擬電路,從而使測量誤差增大。模擬電源均增加了電感和電容濾波,信號地和電源地分開,連接時用電感濾波。通過PCB板的合理布局及電源電路的特別處理,可降低電源和信號干擾,減少測量誤差。

3 系統(tǒng)軟件設(shè)計

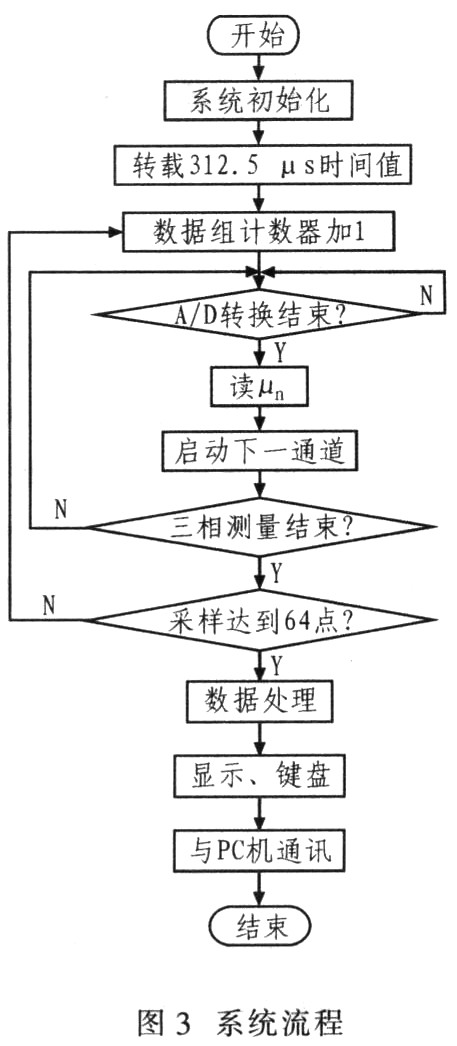

整個系統(tǒng)軟件設(shè)計流程如圖3所示。

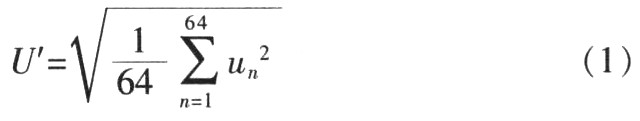

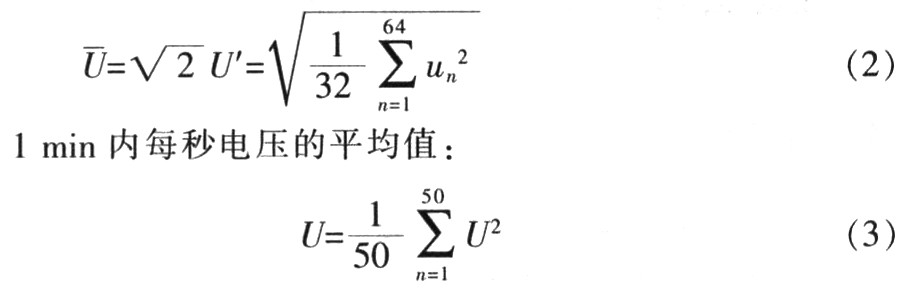

由離散化公式可知,根據(jù)一個周期內(nèi)不同時刻的電壓采樣值及采樣點數(shù)可計算出電壓的有效值。根據(jù)周期T,選擇適當(dāng)?shù)牟蓸哟螖?shù)N,以確定采樣時間間隔。由于AT89C51的主頻為11.059 2.MHz和AD574的轉(zhuǎn)換速度為35μs,并考慮到電力參數(shù)精度要求,采樣周期定為312.5μs,即每個周期內(nèi)采樣64點。另外,阻抗匹配網(wǎng)絡(luò)的輸入電壓與輸出電壓比為![]() 所以阻抗匹配網(wǎng)絡(luò)輸出端的電壓為:

所以阻抗匹配網(wǎng)絡(luò)輸出端的電壓為:

式中,un為第n時刻的瞬時采樣電壓。

則所測電壓為:

根據(jù)式(3),可計算出被測信號電壓,從而可統(tǒng)計出每天的電壓合格時間。

4 結(jié)束語

該系統(tǒng)是基于交流采樣設(shè)計的電力參數(shù)監(jiān)測儀器。通過簡單改變,測量電流、功率等電網(wǎng)參數(shù),所有結(jié)果可在VFD上顯示。該系統(tǒng)具有結(jié)構(gòu)簡單、成本低廉等優(yōu)點。在數(shù)據(jù)處理、轉(zhuǎn)換等方面,具有實時性好、系統(tǒng)抗干擾能力強、可擴展性好等特點,易于在類似的丁業(yè)以及民用的測控系統(tǒng)推廣使用。