摘要:加法運(yùn)算是數(shù)字系統(tǒng)中最基本的算術(shù)運(yùn)算。為了能更好地利用加法器實(shí)現(xiàn)減法、乘法、除法、碼制轉(zhuǎn)換等運(yùn)算,提出用Multisim虛擬仿真軟件中的邏輯轉(zhuǎn)換儀、字信號發(fā)生器、邏輯分析儀,對全加器進(jìn)行功能仿真設(shè)計(jì)、轉(zhuǎn)換、測試、分析,強(qiáng)化Multisim的使用,并通過用集成全加器74LS283實(shí)現(xiàn)兩個一位8421碼十進(jìn)制數(shù)的減法運(yùn)算,掌握了全加器的應(yīng)用方法。測試證明,全加器功能的擴(kuò)展和應(yīng)用,利用Multisim軟件的仿真設(shè)計(jì)能較好地實(shí)現(xiàn)。

關(guān)鍵詞:全加器74LS283D;邏輯轉(zhuǎn)換儀XLC;邏輯分析儀XLA;字信號發(fā)生器XWG;Multisim軟件

數(shù)字系統(tǒng)的基本任務(wù)之一就是進(jìn)行算術(shù)運(yùn)算。而常見的加、減、乘、除等運(yùn)算均可以利用加法運(yùn)算來實(shí)現(xiàn)。所以,加法器就成為數(shù)字系統(tǒng)中最基本的運(yùn)算單元,可廣泛用于構(gòu)成其他邏輯電路。

1 全加器的基本概念

加法器是一種常見的組合邏輯部件,有半加器和全加器之分。半加器是只考慮兩個加數(shù)本身,而不考慮來自低位進(jìn)位的邏輯電路,就是兩個相加數(shù)最低位的加法運(yùn)算。全加器不僅考慮兩個一位二進(jìn)制數(shù)相加,還要考慮與低位進(jìn)位數(shù)相加的運(yùn)算電路。兩個數(shù)相加時(shí),除最低位之外的其余各位均是全加運(yùn)算電路。

2 仿真軟件的特點(diǎn)

Multisim是一個專門用于電路設(shè)計(jì)與仿真的EDA工具軟件。Muhisim起源于20世紀(jì)80年代加拿大In-teractive Image Technologies公司推出的電子仿真軟件EWB5·0(Electronics Workbench)。它以界面形象直觀、操作方便、分析功能強(qiáng)大、易學(xué)易用等突出優(yōu)點(diǎn),迅速被推廣應(yīng)用。

Multisim仿真軟件能將電路原理圖的創(chuàng)建、電路的仿真分析及結(jié)果輸出都集成在一起,并具有繪制電路圖所需的元器件及其仿真測試的儀器,可以完成從電路的仿真設(shè)計(jì)到電路版圖生成的全過程,從而為電子系統(tǒng)的設(shè)計(jì)、電子產(chǎn)品的開發(fā)和電子系統(tǒng)工程提供一種全新的手段和便捷的方法。

3 全加器仿真設(shè)計(jì)分析

全加器是屬于數(shù)字電子技術(shù)中的組合邏輯電路,其功能設(shè)計(jì)可以根據(jù)組合邏輯電路的設(shè)計(jì)方法來完成。通常有確定輸入輸出變量的個數(shù)和狀態(tài)、列真值表、卡諾圖化簡出邏輯表達(dá)式、選擇器件畫出邏輯圖。現(xiàn)在使用Multisim仿真軟件,在組合電路分析設(shè)計(jì)時(shí),將邏輯關(guān)系5種表達(dá)方式中的真值表、邏輯表達(dá)式、邏輯圖任意一種寫入軟件內(nèi),就可以很方便地完成功能分析和設(shè)計(jì)。

3.1 全加器功能仿真分析

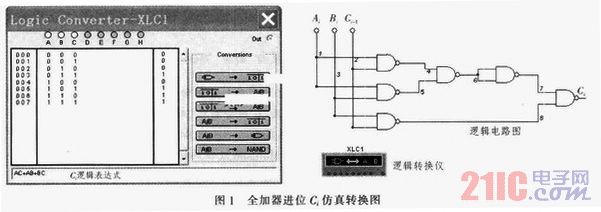

設(shè)計(jì)一個一位二進(jìn)制數(shù)的全加器,其過程是根據(jù)設(shè)計(jì)要求,首先確定輸入、輸出變量的個數(shù)和狀態(tài)。那么該全加器就有3個輸入變量,分別是兩個加數(shù)Ai、Bi和一個低位進(jìn)位Ci-1,兩個輸出變量本位的和Si,以及向高位的進(jìn)位Gi。現(xiàn)在利用Multisim仿真軟件,不需要再進(jìn)行列真值表、卡諾圖化簡、畫邏輯圖等步驟。只要將確定出的輸入變量個數(shù),直接在Multisim仿真軟件中虛擬仿真儀器邏輯轉(zhuǎn)換儀的真值表內(nèi)選中,輸出變量結(jié)果在表中調(diào)準(zhǔn),就能方便地轉(zhuǎn)換出邏輯關(guān)系的其他表示結(jié)果,如圖1所示。

邏輯轉(zhuǎn)換儀XLC(Logic Converter)是Multisim仿真軟件特有的仿真儀器,實(shí)驗(yàn)室并不存在這樣的實(shí)際儀器,目前在其他電路仿真軟件中也沒有。邏輯轉(zhuǎn)換儀可以在真值表、邏輯表達(dá)式、邏輯圖之間進(jìn)行轉(zhuǎn)換。在設(shè)計(jì)電路時(shí),直接將所設(shè)計(jì)電路的真值表輸入邏輯轉(zhuǎn)換儀,就能得到相應(yīng)的邏輯表達(dá)式和邏輯圖等。

實(shí)現(xiàn)全加器邏輯功能,將全加器和輸出S及進(jìn)位輸出Gi的真值表分別寫入邏輯轉(zhuǎn)換儀,選中并點(diǎn)擊邏輯轉(zhuǎn)換儀XLC1圖標(biāo),出現(xiàn)邏輯轉(zhuǎn)換儀面板,在其最上方有A-H 8個輸入變量選擇,全加器輸入3個變量A、B、C,點(diǎn)擊選中對應(yīng)的小圓圈變白,并在下方表格內(nèi)自動生成輸入變量的全部組合,在表格右邊一列點(diǎn)擊鼠標(biāo)調(diào)整輸出的值0、1或X,真值表寫入后操作邏輯轉(zhuǎn)換儀的圖標(biāo)![]() ,就自動在邏輯轉(zhuǎn)換儀面板的左下方轉(zhuǎn)換出與進(jìn)位Ci真值表對應(yīng)的標(biāo)準(zhǔn)與或邏輯表達(dá)式或最簡與或表達(dá)式,圖1中是最簡與或表達(dá)式Ci=AiCi-1+AiBi+BiCi-1或最簡表達(dá)式

,就自動在邏輯轉(zhuǎn)換儀面板的左下方轉(zhuǎn)換出與進(jìn)位Ci真值表對應(yīng)的標(biāo)準(zhǔn)與或邏輯表達(dá)式或最簡與或表達(dá)式,圖1中是最簡與或表達(dá)式Ci=AiCi-1+AiBi+BiCi-1或最簡表達(dá)式![]() 。操作邏輯轉(zhuǎn)換儀的圖標(biāo)

。操作邏輯轉(zhuǎn)換儀的圖標(biāo)![]() ,得到全加器進(jìn)位Ci的與或邏輯圖或與非邏輯圖,圖1中是與非邏輯電路圖。

,得到全加器進(jìn)位Ci的與或邏輯圖或與非邏輯圖,圖1中是與非邏輯電路圖。

采用同樣的方法,將全加器本位和Si的真值表寫入邏輯轉(zhuǎn)換儀,操作邏輯轉(zhuǎn)換儀相應(yīng)的圖標(biāo),可以準(zhǔn)確地得到全加器本位和Si的標(biāo)準(zhǔn)與或表達(dá)式或最簡與或表達(dá)式,![]()

![]() ,及其相應(yīng)的邏輯電路圖。

,及其相應(yīng)的邏輯電路圖。

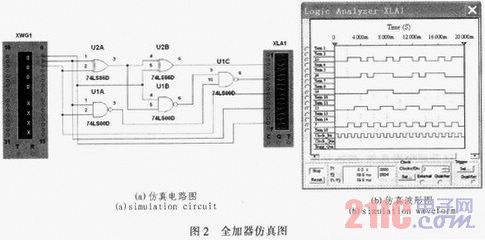

通過邏輯轉(zhuǎn)換儀設(shè)計(jì)出全加器的功能,進(jìn)行仿真測試,如圖2所示。是根據(jù)設(shè)計(jì)得到邏輯表達(dá)式或邏輯圖,按照最簡仿真電路圖圖2(a),利用Multisim仿真軟件中字信號發(fā)生器XWG(Word Generator,又稱數(shù)字邏輯信號源)這個能產(chǎn)生32路(位)同步邏輯信號的儀器,用來對數(shù)字邏輯電路進(jìn)行測試。XWG1產(chǎn)生全加器3個輸入變量的二進(jìn)制邏輯組合。使用時(shí),對字信號發(fā)生器面板上的各個選項(xiàng)和參數(shù)進(jìn)行適當(dāng)設(shè)置,才能使其正常工作和顯示。全加器仿真測試時(shí)參數(shù)設(shè)計(jì)地址為0000~0007、控制按循環(huán)輸出及逐個加1遞增方式編碼、選擇內(nèi)部觸發(fā)方式、輸出頻率為1 kHz,作為電路信號。邏輯分析儀XIA(Logic Analyzer)可以同步記錄和顯示16路邏輯信號,用于對數(shù)字邏輯信號進(jìn)行高速采集和時(shí)序分析。XLA1測試全加器輸入輸出的仿真波形,如圖2(b)所示,圖中波形從上至下分別是全加器輸出和Si、進(jìn)位Ci、輸入Ai、Bi及低位進(jìn)位Ci-1。從對應(yīng)關(guān)系上觀察分析實(shí)際結(jié)果與理論設(shè)計(jì)相吻合,而且無競爭和冒險(xiǎn)現(xiàn)象產(chǎn)生。從輸入變量波形的對應(yīng)關(guān)系可見,字信號發(fā)生器XWG的輸出,隨著輸出端子號的增加頻率按照二分頻在衰減,如圖2(b)所示,每增加一個輸出端,頻率就衰減二分之一。所以在使用XWG時(shí),輸入的對應(yīng)關(guān)系一定要準(zhǔn)確,否則就仿真不出結(jié)果。

3.2 集成全加器仿真分析

在實(shí)際應(yīng)用中廣泛采用的是集成全加器,代號74LS283。它是一個四位全加器,可以實(shí)現(xiàn)四位加法運(yùn)算和功能擴(kuò)展應(yīng)用。全加器74LS283功能仿真電路如圖3(a)所示。為了能夠監(jiān)測判斷出集成芯片的完好狀態(tài),將兩個加數(shù)中的一個及低位進(jìn)位均設(shè)置為高電平“1”接電源VCC,這樣全加器輸出的和就應(yīng)該與另一個加數(shù)完全相同,仿真結(jié)果如圖3(b)所示。圖中從上至下分別顯示的波形是加數(shù)B4、B3、B2、B1,本位和S4、S3、S2、S1,最高位進(jìn)位C4。仿真測試時(shí)字信號發(fā)生器參數(shù)設(shè)計(jì)地址從0000~000F,其余設(shè)置同上。圖3結(jié)果表明全加器74LS283的芯

片完好,功能準(zhǔn)確。

利用全加器74LS283芯片仿真兩個四位二進(jìn)制數(shù)的加法運(yùn)算電路圖,如圖4(a)所示。為確保兩個加數(shù)頻率變化不一致形成便于測試的輸入輸出結(jié)果,在與字信號發(fā)生器連接時(shí)把同一位的兩個加數(shù)接在不同的端子上,并設(shè)置好相應(yīng)的參數(shù),就能得到如圖4(b)所示的仿真波形圖。圖中從上至下波形是加數(shù)A4、A3、A2、A1,本位和S4、S3、S2、S1,最高位進(jìn)位C4,另一個加數(shù)B4、B3、B2、B1。從仿真波形結(jié)果分析符合全加運(yùn)算的規(guī)律和特點(diǎn),滿足全加運(yùn)算的結(jié)果。

3.3 全加器功能應(yīng)用仿真設(shè)計(jì)

全加器除了可完成二進(jìn)制加法運(yùn)算外,還可以實(shí)現(xiàn)二進(jìn)制減法運(yùn)算、乘法運(yùn)算,BCD碼的加、減法,碼制轉(zhuǎn)換,數(shù)碼比較,奇偶校驗(yàn)等應(yīng)用。用集成全加器74LS283實(shí)現(xiàn)兩個一位8421碼十進(jìn)制數(shù)的減法運(yùn)算功能仿真,如圖5所示。

根據(jù)減去一個正數(shù),等于加上一個負(fù)數(shù)的概念,將一位十進(jìn)制數(shù)的減法變成加法。在數(shù)字電子技術(shù)中,這種運(yùn)算可以用機(jī)器數(shù)的原碼、反碼、補(bǔ)碼來實(shí)現(xiàn)。對于一個正數(shù)其原碼、反碼、補(bǔ)碼是一樣的,而對于一個負(fù)數(shù)其補(bǔ)碼是在原碼基礎(chǔ)上符號位不變,其余各位取反為反碼,再在最低位加1形成的。原碼、反碼在計(jì)算后都要進(jìn)行修正,而補(bǔ)碼符號位進(jìn)位自然丟失,可直接還原出真值。

圖5中全加器的加數(shù)B4、B3、B2、B1,是由字信號發(fā)生器輸出經(jīng)反相器(按位取反)后輸入的。并且全加器最低位進(jìn)位設(shè)為1,實(shí)現(xiàn)了按位取反再加1,組成A減B的運(yùn)算電路。

利用補(bǔ)碼轉(zhuǎn)換為加法運(yùn)算后,8421碼十進(jìn)制數(shù)的計(jì)數(shù)規(guī)律是逢十進(jìn)一,而全加器74LS283是四位二進(jìn)制逢十六進(jìn)一,兩者進(jìn)位關(guān)系不同,當(dāng)和數(shù)大于9時(shí)8421碼產(chǎn)生進(jìn)位,而十六進(jìn)制不產(chǎn)生。為此,由74LS00和74LS10構(gòu)成結(jié)果修正電路。當(dāng)和數(shù)大于9時(shí),該電路輸出1,為加法運(yùn)算增加修正數(shù)6(第二個全加器的加數(shù)B=0110)實(shí)現(xiàn)進(jìn)位。當(dāng)和數(shù)小于9時(shí),該電路輸出0,修正數(shù)為0。從測試結(jié)果得知,此電路實(shí)現(xiàn)具有修正功能的一位8421碼十進(jìn)制減法運(yùn)算。圖5中顯示6-6=0。在仿真測試時(shí),兩個字信號發(fā)生器的地址參數(shù)設(shè)定為0000-0009。

4 結(jié)束語

Multisim仿真軟件為工程技術(shù)設(shè)計(jì)仿真、電子技術(shù)教學(xué)、實(shí)訓(xùn)、演示提供了強(qiáng)大、靈活、便捷、生動的虛擬仿真工具。通過對全加器功能及應(yīng)用的虛擬仿真設(shè)計(jì)、測試、分析,既熟練掌握仿真軟件中儀器儀表的使用,也鍛煉分析問題解決問題的能力,同時(shí)還能準(zhǔn)確地驗(yàn)證所設(shè)計(jì)仿真測試的內(nèi)容和方法,為進(jìn)一步利用Multisim軟件開發(fā)設(shè)計(jì)仿真新項(xiàng)目打下基礎(chǔ)。