隨著軟件無線電的發(fā)展,對于濾波器" title="濾波器">濾波器的處理速度要求越來越高。傳統(tǒng)的FIR濾波器一般采用通用DSP處理器,但是DSP處理器采用的是串行運算,而FPGA" title="FPGA">FPGA是現(xiàn)場可編程陣列,可以實現(xiàn)專用集成電路,另外還可以采用純并行結(jié)構(gòu)及考慮流水線結(jié)構(gòu),因此在處理速度上可以明顯高于DSP處理器。本文采用并行分布式算法在FPGA上設計并實現(xiàn)了高速處理的32階FIR低通濾波器,在此過程中利用Matlab的數(shù)值計算與分析功能來提高設計效率。

在數(shù)字信號處理中,數(shù)字濾波器的應用是極其廣泛和重要的單元。與模擬濾波器相比,數(shù)字濾波器可以克服模擬濾波器所無法克服的電壓漂移,溫度漂移以及噪聲等問題。數(shù)字濾波器根據(jù)沖擊響應函數(shù)的特性,可以分為IIR濾波器和FIR濾波器兩種。由于FIR濾波器只有零點、系統(tǒng)穩(wěn)定等諸多優(yōu)點。

1 FlR低通濾波器的窗函數(shù)實現(xiàn)

理想的濾波器頻率響應中傅里葉反變換ha(n)一定是無限長的序列,而且是非因果的,而實際要設計的濾波器h(n)是有限長的,因此要用有限長來逼近無限長的,其方法就是用一個有限長度的窗口函數(shù)序列ω(n)來截取,即:

![]()

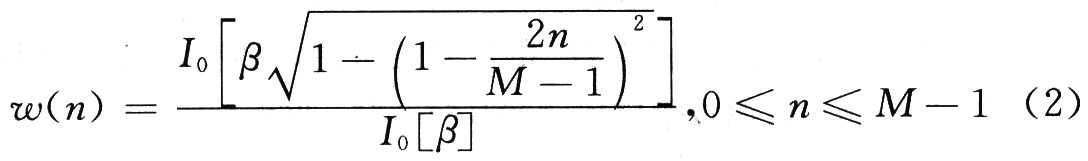

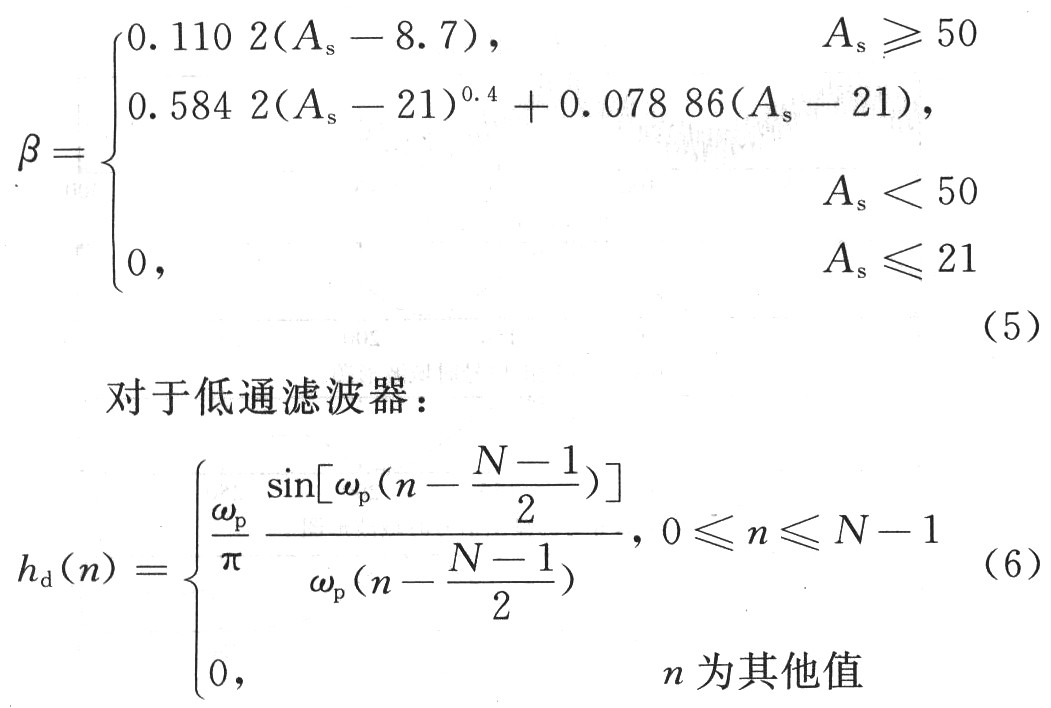

常見的窗函數(shù)有矩形窗、巴特利特窗、漢寧窗、哈明窗、布萊克曼窗、凱澤窗。其中,凱澤窗提供了可變的過渡帶寬。本文采用凱澤窗對FIR濾波器進行設計,其窗函數(shù)表達式為:

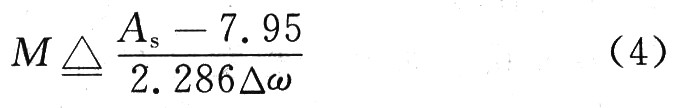

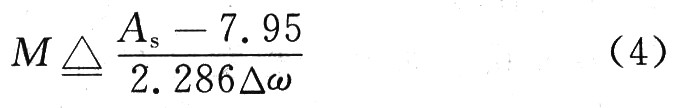

I0[·]為第一類變形零階貝賽爾函數(shù),形狀參數(shù)β為依賴于濾波器階數(shù)M的參數(shù),用來調(diào)整主瓣寬度與旁瓣衰減,選擇M可產(chǎn)生各種過渡帶寬和接近最優(yōu)的阻帶衰減。給定通帶截止頻率ωp,阻帶起始頻率ωs,阻帶衰減As,凱澤窗設計中有經(jīng)典公式可供使用,如下:

過渡帶寬:

濾波器階數(shù):

形狀參數(shù):

假設低通數(shù)字濾波器設計指標如下:

![]()

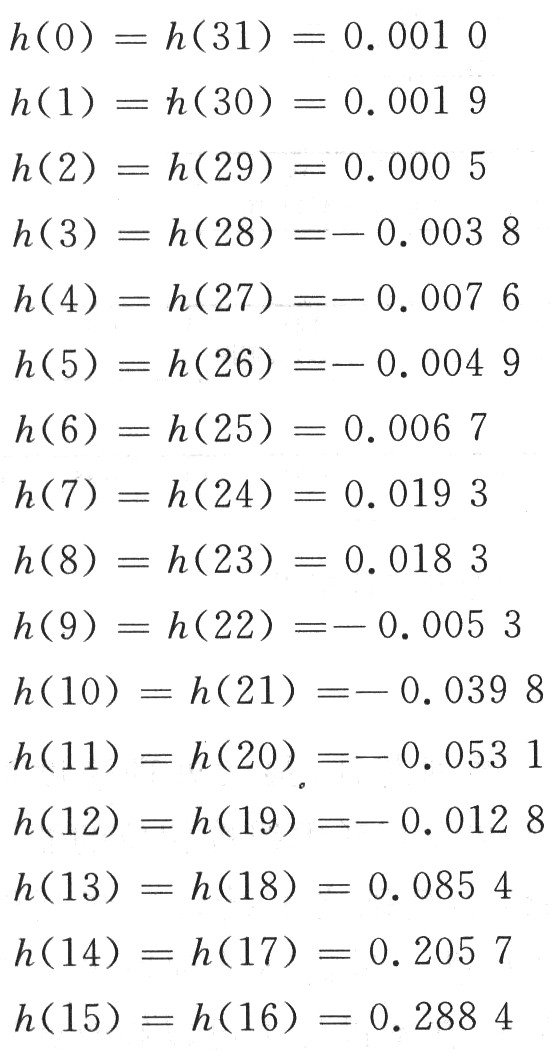

采用上面介紹的凱澤窗,利用Matlab編程計算得到32階FIR低通濾波器參數(shù)如下:

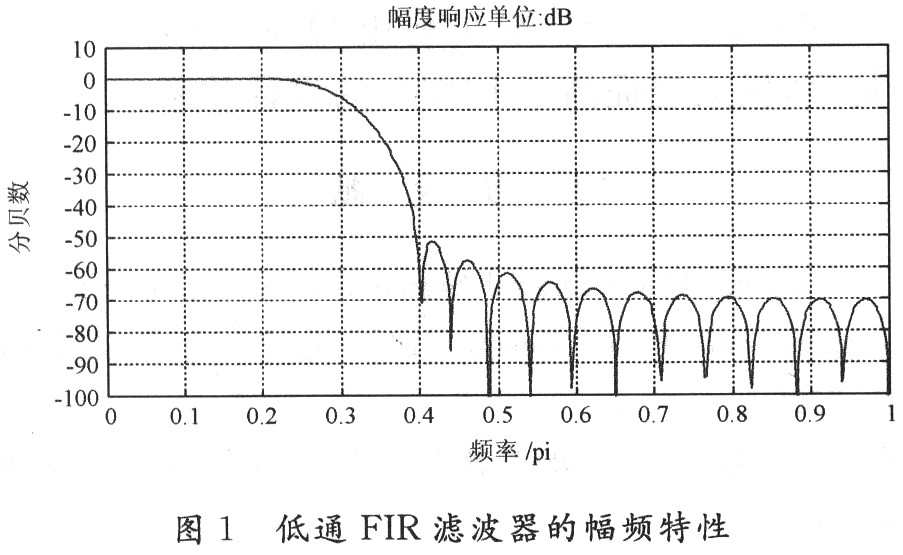

32階FIR低通濾波器幅頻特性圖如圖1所示。

上述求得的系數(shù)是浮點型的,而在FPGA設計中使用的數(shù)據(jù)是定點型的,所以在設計濾波器之前要將系數(shù)轉(zhuǎn)化為定點型,即系數(shù)的量化。為了兼顧精度和所占用的資源,本文的系數(shù)用12位二進制來量化,得到的整數(shù)系數(shù)結(jié)果如下:

2 并行分布式算法原理及FPGA設計

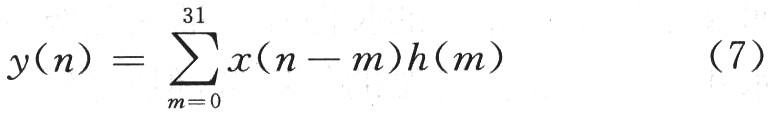

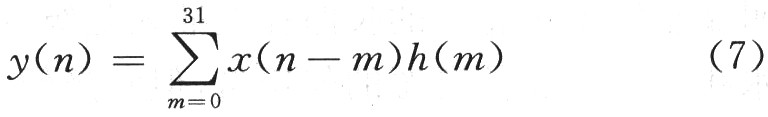

32階FIR濾波器的差分方程表達式為:

式中:x(n)為輸入;y(n)為輸出;h(n)為濾波器系數(shù)。

設x(n)用二進制可表示為:

其中,最高位為符號位。則式(7)可寫為:

式(10)為并行分布式算法,由上可以看出并行分布式算法是將濾波器表達式重新排列,分別加權(quán)求和。與傳統(tǒng)算法最大的不同之處是在FPGA設計過程中以查找表代替乘法器,即根據(jù)輸入數(shù)據(jù)的不同,將對應的濾波器系數(shù)預先求和保存在ROM中,也就是將每一項的乘法求和通過并行結(jié)構(gòu)查表尋值完成,提高運行速度。

具體FPGA實現(xiàn)時,首先將12位的輸人數(shù)據(jù)并行輸入到12列32位移位寄存器分別寄存,然后以寄存器中的值為地址,對應于查找表的結(jié)果,按照式(10),每列進行相應二次冪加權(quán),最后各列累加,在第32個數(shù)據(jù)完全輸入之后得到正確的濾波器輸出。可以將32位的查找表劃分為四個8位的查找表,從而降低對ROM的需求。

在本設計中可采用多級流水線技術,也就是將在明顯制約系統(tǒng)速度的長路徑上插入幾級寄存器,雖然流水線會影響器件資源的使用量,但它降低了寄存器間的傳播時延,允許維持高的系統(tǒng)時鐘速率。

3 FPGA仿真與驗證

FPGA(Field-Programmable Gate Array),即現(xiàn)場可編程門陣列,它是在PAL、GAL、CPLD等可編程器件的基礎上進一步發(fā)展的產(chǎn)物。它是作為專用集成電路(ASIC)領域中的一種半定制電路而出現(xiàn)的,既解決了定制電路的不足,又克服了原有可編程器件門電路數(shù)有限的缺點。

FPGA采用了邏輯單元陣列LCA(Logic Cell Array)這樣一個概念,內(nèi)部包括可配置邏輯模塊CLB(Configurable Logic Block)、輸出輸入模塊IOB(Input Output Block)和內(nèi)部連線(Interconnect)三個部分。 現(xiàn)場可編程門陣列(FPGA)是可編程器件。與傳統(tǒng)邏輯電路和門陣列(如PAL,GAL及CPLD器件)相比,F(xiàn)PGA具有不同的結(jié)構(gòu),F(xiàn)PGA利用小型查找表(16×1RAM)來實現(xiàn)組合邏輯,每個查找表連接到一個D觸發(fā)器的輸入端,觸發(fā)器再來驅(qū)動其他邏輯電路或驅(qū)動I/O,由此構(gòu)成了即可實現(xiàn)組合邏輯功能又可實現(xiàn)時序邏輯功能的基本邏輯單元模塊,這些模塊間利用金屬連線互相連接或連接到I/O模塊。

由于直接將大量數(shù)據(jù)進行硬件仿真驗證很不方便,因此利用Matlab產(chǎn)生一個采樣頻率為100 MHz,頻率分別為1 MHz與30 MHz的兩個正弦信號相加后,作為輸入信號。vec文件,導入到QuartusⅡ中進行仿真,時序功能仿真結(jié)果如圖2所示。

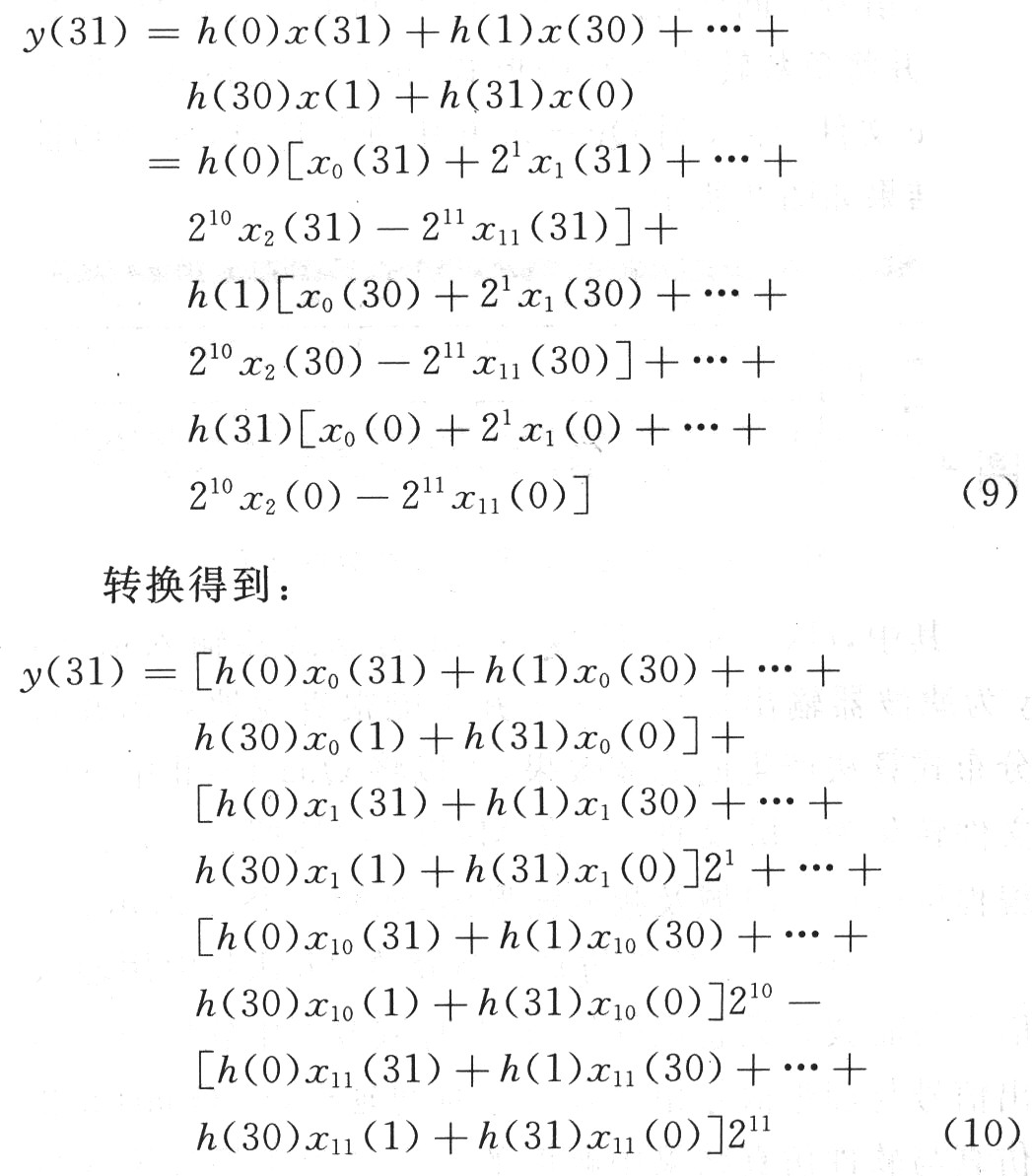

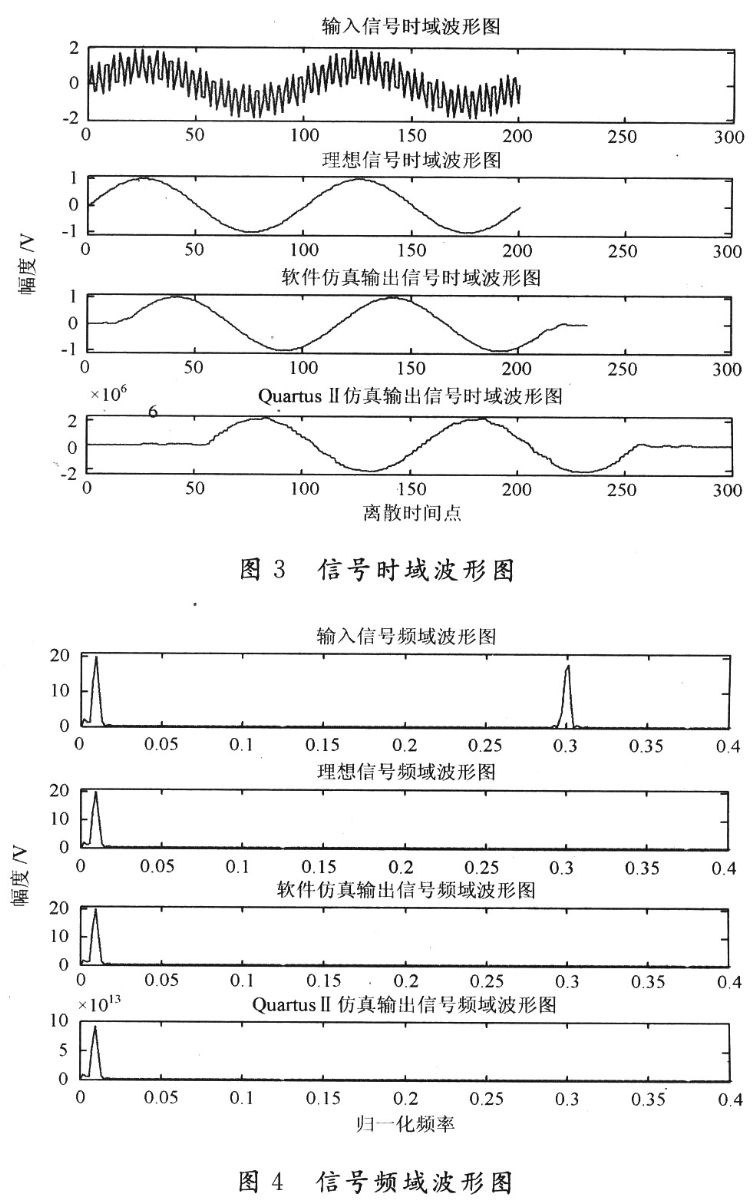

其中,clk為時鐘信號,x_in為濾波器輸入信號,y為濾波器輸出信號。圖2并不能很直觀地看出并行分布式算法產(chǎn)生的濾波效果,可以將QuartusⅡ中。vwf文件轉(zhuǎn)化為。tbl文件,在Matlab中按照一定形式編程可以得到時域及頻域波形圖,如圖3,圖4所示。

圖3,圖4中,軟件仿真是直接在Matlab中用輸入信號與濾波系數(shù)卷積得到的,在時域波形中軟件仿真輸出信號與理想信號相比有一定時間延遲,而QuartusⅡ仿真與軟件仿真結(jié)果中幅度的差別是由于硬件輸入量化產(chǎn)生的。

從時域或者頻域波形圖可以看出,頻率為30 MHz的信號被濾除掉,只有頻率為1 MHz的信號通過濾波器,達到了濾波的目的。

4 結(jié) 語

本設計選用Stratix系列芯片,最大處理速度可以達到200 MHz以上。本文沒有考慮線性相位" title="線性相位">線性相位的濾波器對稱性,在考慮線性相位的基礎之上結(jié)合一些其他算法可以降低器件數(shù)量和進一步提高處理速度。由于FPGA器件的可編程特性,在本設計中可以修改濾波器參數(shù),得到高速處理的高通或者帶通數(shù)字濾波器,具有一定實用價值。另外,本文利用QuartusⅡ與Matlab聯(lián)合仿真,極大地提高了FPGA的設計效率。