1 電磁干擾(EMI)分析

1.1 電磁干擾的概念及途徑

電磁干擾產(chǎn)生于干擾源,他是一種來自外部和內(nèi)部的并有損于有用信號(hào)的電磁現(xiàn)象。干擾經(jīng)過敏感元件、傳輸線、電感器、電容器、空間場(chǎng)等形式的途徑并以某種形式作用,其干擾效應(yīng)、現(xiàn)象普遍存在,形式各異,稱之為傳導(dǎo)干擾,他按帶不帶信息可以分為信息傳導(dǎo)干擾源和電磁噪聲傳導(dǎo)干擾源兩類。信息傳導(dǎo)干擾源是指帶有的無用信息對(duì)模擬通道的干擾。電磁噪聲傳導(dǎo)干擾源是指不帶任何信息的電磁噪聲對(duì)變頻系統(tǒng)的干擾。

傳導(dǎo)電磁干擾傳輸通道可以分為電容傳導(dǎo)耦合(或稱電場(chǎng)耦合)、電阻傳導(dǎo)耦合(或公共阻抗耦合)及電感傳導(dǎo)耦合(或互感耦合)。電容傳導(dǎo)耦合是指干擾源和信號(hào)傳輸線(包括印制電路線)之間通過導(dǎo)線以及部件的電容互相交鏈而構(gòu)成的電磁傳導(dǎo)耦合。電阻傳導(dǎo)耦合是指干擾源和信號(hào)傳輸線(包括印制電路線)之間通過公共阻抗上的電流或電壓交鏈而構(gòu)成的傳導(dǎo)電磁耦合。電感傳導(dǎo)耦合實(shí)質(zhì)上是磁場(chǎng)耦合。

1.2 數(shù)字變頻調(diào)速系統(tǒng)電磁干擾問題

數(shù)字變頻調(diào)速系統(tǒng)中這3種情況都存在,電阻傳導(dǎo)耦合和電感傳導(dǎo)耦合的表現(xiàn)尤為明顯,主要是參考地的設(shè)計(jì)、印制線路板的設(shè)計(jì)和高低壓的隔離,模擬接口電路中易受到功率電路的影響。DSP的電磁兼容特性主要反映在管腳信號(hào)電氣特性上。DSP的輸入輸出信號(hào)多數(shù)是數(shù)字信號(hào),其外部接口電路也多數(shù)是數(shù)字電路,包括功率器件IPM也工作在開關(guān)狀態(tài),整個(gè)系統(tǒng)具有明顯的數(shù)字電路特征,只有電流反饋環(huán)路是模擬信號(hào),通過DSP的片內(nèi)A/D轉(zhuǎn)換器將模擬信號(hào)轉(zhuǎn)成數(shù)字信號(hào)進(jìn)行處理,再控制PWM的輸出來實(shí)現(xiàn)閉環(huán)控制。在本設(shè)計(jì)中電磁干擾的表現(xiàn)具體分析為以下幾點(diǎn)。

(1)瞬態(tài)脈沖干擾對(duì)數(shù)字電路的影響

數(shù)字信號(hào)處理器以二進(jìn)制碼為基礎(chǔ)。用高、低電平來表示二進(jìn)制數(shù)據(jù),并通過各種電路來描述信號(hào)特征,從而達(dá)到控制對(duì)象的目的。瞬態(tài)脈沖干擾將嚴(yán)重地影響了數(shù)據(jù)傳輸和控制狀態(tài),對(duì)于數(shù)字電路本身雖然具有很強(qiáng)的抗干擾能力,但在高頻率電路中易受到攜帶高能量的脈沖干擾,其干擾部位表現(xiàn)在時(shí)鐘發(fā)生器、總線數(shù)據(jù)傳輸、PWM控制信號(hào)。IPM內(nèi)部的IGBT高速工作在開關(guān)狀態(tài)將產(chǎn)生很強(qiáng)的開關(guān)噪聲,通過地線、電源線、分布電容、分布電感的耦合帶入低壓數(shù)字電路中,有時(shí)嚴(yán)重地干擾了TMS320F240數(shù)字信號(hào)處理器的運(yùn)算,表現(xiàn)為失控、程序跑飛和死機(jī)。

(2)分布電感、電容對(duì)信號(hào)的影響

基于DSP控制的系統(tǒng)設(shè)計(jì),控制部分通常選用TMS320F240EVM評(píng)估板,控制電路印制板的設(shè)計(jì)簡化了很多,只有IPM驅(qū)動(dòng)板的電路設(shè)計(jì)和印制板要仔細(xì)地分析信號(hào)間的分布電容、分布電感的影響。但要注意考慮的是評(píng)估板與驅(qū)動(dòng)板間的信號(hào)總線分布電感的影響,他可能會(huì)造成信號(hào)的延時(shí)和加長PWM控制信號(hào)的上、下降時(shí)間,從而導(dǎo)致IPM模塊中的上、下橋臂IGBT共通,這樣將造成IPM模塊不可恢復(fù)的永久損壞。

(3)電源對(duì)系統(tǒng)的影響

電源是多種干擾信號(hào)影響系統(tǒng)正常工作的途徑,主要有以下幾點(diǎn)影響:

內(nèi)阻不可能為零,凡是共電源的部分其干擾信號(hào)都可以通過電源內(nèi)阻互竄;電網(wǎng)線上是外部干擾(如:雷電、電磁發(fā)射)進(jìn)入的渠道;電源負(fù)載的斷開與接通將在電網(wǎng)上形成很大沖擊,感性負(fù)載的沖擊更為嚴(yán)重;電源本身將產(chǎn)生許多干擾信號(hào),特別是IGBT高速開關(guān)產(chǎn)生的開關(guān)噪聲。

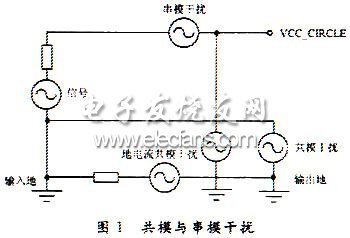

干擾信號(hào)在系統(tǒng)中存在2種形態(tài),即共模與串模干擾信號(hào)。在數(shù)字系統(tǒng)中常用此來表征干擾作用的存在,如圖1所示。串模干擾又稱正態(tài)干擾,他是指串聯(lián)于信號(hào)回路中的干擾,產(chǎn)生于傳輸線的互感,其與頻率有關(guān),常用濾波和改善采樣頻率來減少。共模干擾又稱共態(tài)干擾,是干擾電壓同時(shí)加到兩條信號(hào)線上出現(xiàn)的干擾,因此線路傳輸結(jié)構(gòu)保持平衡能很好地抑制共模干擾。另外,消除地電流,能消除共模干擾,辦法是一點(diǎn)接地或浮空隔離(用脈沖變壓器、扼流圈或光電耦合器截?cái)嗟仉娏?。

2 硬件抗干擾技術(shù)

2.1 電源系統(tǒng)的電磁兼容設(shè)計(jì)

電源系統(tǒng)包含低壓輔助電源和主電源。低壓輔助電源是指DSP及其相關(guān)的接口電路所需的+5 V,土12 V,和IPM驅(qū)動(dòng)電路的4組+15 V隔離電源。主電源是指用于電機(jī)驅(qū)動(dòng)可調(diào)速的AC/DC/AC電源,他與低壓輔助電源相互隔離,不共地。電源系統(tǒng)采用的抗干擾措施有:

(1)電網(wǎng)輸入的交流電應(yīng)加EMI抑制濾波器,即由共態(tài)扼流圈L,電容C,電阻R組成的低通濾波器。他不僅能防止電網(wǎng)的串模、共模干擾信號(hào)進(jìn)入電源,而且還有效地防止系統(tǒng)本身產(chǎn)生的干擾進(jìn)入電網(wǎng),有利于環(huán)保。

(2)IGBT大電流通斷時(shí),電路中伴有電壓性和電流性的浪涌,由于du/dt,di/dt很大,故浪涌干擾信號(hào)的高頻成分很高,在IPM電源輸入端應(yīng)并聯(lián)小容量的高頻電容,以消除寄生振蕩。

(3)功率輸入輸出電源連接線采用絞線連接,這樣能減小環(huán)路的電流產(chǎn)生電磁場(chǎng)的輻射。

(4)低壓與高壓利用互感器、光耦信號(hào)和地線隔離,以阻斷共模干擾。按電源輸出的干擾的持續(xù)時(shí)間Δt的不同來選擇抑制對(duì)策;

Δt>1 s屬于過電壓、欠電壓,停電干擾。采用不間斷電源(UPS)和穩(wěn)壓的辦法抑制;

Δt>10 ms屬于浪涌、下陷、降出干擾,這類干擾電壓的幅度大、變化快,不是燒壞系統(tǒng)就是形成振蕩,需要用快速響應(yīng)的浪涌吸收器、電壓瞬態(tài)抑制二極管(TVS)來防止;

Δt為微秒級(jí),屬于尖峰電壓干擾,由于持續(xù)時(shí)間短,一般不會(huì)燒壞系統(tǒng),但能破壞DSP的源程序的運(yùn)行,使邏輯功能混亂,信號(hào)線應(yīng)遠(yuǎn)離干擾源和加屏蔽;

Δt為納秒級(jí),屬于射頻干擾,對(duì)DSP和數(shù)字信號(hào)的危害不嚴(yán)重,一般在IC的電源輸入端加高頻去耦電容即可。

2.2 接口電路的抗干擾措施

DSP的外圍電路工作方式各不相同,速度也各有快慢,信息的交換受DSP數(shù)字信號(hào)處理器的控制。各種任務(wù)均由接口去完成,接口信號(hào)受到干擾將影響到系統(tǒng)的控制結(jié)果。接口的干擾又來自其相連接的傳輸線,包含了印制板的電路線設(shè)計(jì)和電路板與電路板間的連接。電路板與電路板間的連接最常用的傳輸線有扁平電纜、雙絞線和同軸電纜等,從抗干擾的角度看,雙絞線是一種抵抗電磁干擾性能較好的傳輸線,其相交的回路中兩線的往返電流感應(yīng)作用相抵消,因此作用距離達(dá)10 m,用于電源的輸出和輸入部分。DSP產(chǎn)生的PWM控制信號(hào)作用于IPM,采用光耦隔離,因?yàn)楣怦畹墓材R种票群芨撸行У胤乐沽丝刂齐娐泛蚉WM變換器間的共模干擾,其原理圖如圖2所示。

2.3 總線的抗干擾措施

(1)采用三態(tài)門式的總線提高抗干擾能力。由于DSP總線的直流負(fù)載能力有限,如果不夠,就需要通過緩沖器再與芯片相連接;

(2)總線上數(shù)據(jù)沖突的防止措施:CPU與隨機(jī)存儲(chǔ)器的連接是由總線收發(fā)器通過內(nèi)部雙向數(shù)據(jù)總線實(shí)現(xiàn)的,內(nèi)部數(shù)據(jù)總線上會(huì)在某瞬間產(chǎn)生沖突,解決方法是縮小隨機(jī)存儲(chǔ)器存取數(shù)據(jù)的時(shí)間即縮小選通時(shí)間;

(3)克服總線上瞬間不穩(wěn)定的措施:當(dāng)兩個(gè)相位相反的控制信號(hào)在時(shí)間上存在偏差時(shí),一個(gè)由低電平變?yōu)楦唠娖剑硪粋€(gè)還來不及由高電平變?yōu)榈碗娖剑瑑蓚€(gè)均是高阻狀態(tài),這一瞬間如果總線的負(fù)載是TTL電路,他將因自身的泄漏電流使總線電壓不穩(wěn)定;若負(fù)載全是CMOS或NMOS,則有幾百兆歐的斷開狀態(tài),很容易耦合干擾。用上拉電阻連接到電源,使總線在此瞬間處于高電位,這樣增強(qiáng)了總線的抗干擾能力。其上拉電阻常選擇1Ω。

2.4 功率輸出的電磁兼容設(shè)計(jì)

功率輸出部分是由IPM、驅(qū)動(dòng)電路和泵升電路組成的電源變換器。運(yùn)用PWM算法,DSP產(chǎn)生的6組PWM信號(hào)通過光電耦合器的隔離傳輸,再通過IPM驅(qū)動(dòng)電路控制IPM內(nèi)部的IGBT開關(guān)工作。直流電源端加吸收電容,可以抑制開關(guān)噪聲。在系統(tǒng)設(shè)計(jì)中應(yīng)保證低壓控制電路盡可能地遠(yuǎn)離功率電路,以保證低壓地信號(hào)不受到電磁幅射和耦合。

2.5 印制電路板抗干擾措施

實(shí)踐證明,印制電路板的設(shè)計(jì)對(duì)抗干擾和保證系統(tǒng)的工作穩(wěn)定有重要影響。印制電路板加電后,印制線上的電流將產(chǎn)生電磁波輻射到空間,電路中的高速元件、晶體振蕩器等器件也將產(chǎn)生電磁輻射。在高速處理的數(shù)字系統(tǒng)中,當(dāng)2倍的延遲時(shí)間大于脈沖的上升沿或下降沿時(shí),印制電路板中的數(shù)字信號(hào)傳輸線應(yīng)當(dāng)按分布參數(shù)的傳輸線的要求考慮匹配,如一般轉(zhuǎn)換速度較快的TTL電路,印制線長度大于10 cm以上時(shí)就要加終端匹配措施。COMS電路的轉(zhuǎn)換速度比較慢,印制線長度可放寬5~6倍。根據(jù)電磁輻射模型公式:

E=263×10-6(f2AI)/r

式中:E為印制電路板空間r處的輻射場(chǎng)強(qiáng);f為印制電路板上的工作電流的頻率;A為印制電路板上的環(huán)路面積;I為印制電路板上的電流。

由上式可以看出,減小f,A,I均可以降低印制電路板上的電場(chǎng)發(fā)射。為了更好地抑制干擾,印制電路板的設(shè)計(jì)中應(yīng)考慮以下一些問題:

(1)布線原則:數(shù)字信號(hào)線和模擬信號(hào)線分開,強(qiáng)弱信號(hào)分開,直流電源線正交,發(fā)熱元件應(yīng)遠(yuǎn)離集成電路,磁性元件要屏蔽,每個(gè)IC芯片的電源端對(duì)地端要有去耦電容,引線要短;

(2)印制板的大小應(yīng)適中,邏輯元件相互靠近,與易產(chǎn)生干擾的器件遠(yuǎn)離。印制電路板的接地線應(yīng)盡量寬,這不僅僅是因?yàn)槟軠p少損耗,而且也能減少線的電感分量,從而減小共模干擾。如果是雙層布線或多層布線時(shí)應(yīng)遵循電源和地為中間層、頂層和底層的電線相互正交,盡量少走平行線。

(3)印制電路板上電源輸入端跨接10~100μF的電解電容,對(duì)易受電路中干擾信號(hào)影響和有暫態(tài)狀陡峭變化電流的器件,其與地之間接入高頻特性好的去耦電容,如RAM,ROM芯片動(dòng)作時(shí)電流變化大,應(yīng)在每片的電源端加O.01μF的陶瓷電容以旁路高頻。

3 軟件抗干擾技術(shù)

軟件抗干擾既能提高效能、節(jié)省硬件,又能解決硬件解決不了的問題。大量的干擾源雖然不能造成硬件的破壞,但卻使系統(tǒng)的工作不穩(wěn)定、數(shù)據(jù)不可靠、運(yùn)行失常、程序“跑飛”,嚴(yán)重時(shí)可導(dǎo)致DSP的控制失靈、發(fā)生嚴(yán)重事故。由于故障是暫時(shí)、間歇、隨機(jī)的,用硬件解決比較困難,而軟件可借助以下的技術(shù)予以解決:

(1)利用陷阱技術(shù)防止干擾造成的亂序現(xiàn)象擴(kuò)展下去;

(2)利用時(shí)間冗余技術(shù),屏蔽干擾信號(hào),即多次采樣輸入、判斷,以提高輸入的可靠性;利用多次重復(fù)輸出來判斷,提高輸出信息的可靠性;重新初始化,強(qiáng)行恢復(fù)正常工作,以免I/O的輸入輸出不正常;查詢中斷源的狀態(tài),防止干擾造成誤中斷;在不需要的時(shí)間里屏蔽中斷,以減少因干擾引起的誤中斷;

(3)容錯(cuò)技術(shù):采用一些特定的編碼,對(duì)數(shù)據(jù)進(jìn)行檢查,判斷是否因存放受干擾,然后從邏輯上對(duì)錯(cuò)誤進(jìn)行糾正;

(4)指令冗余:對(duì)重要的指令可重復(fù)寫多個(gè);

(5)標(biāo)志法:設(shè)特征標(biāo)志、識(shí)別標(biāo)志,常在內(nèi)部數(shù)據(jù)區(qū)的保護(hù)中應(yīng)用;

(6)數(shù)字濾波技術(shù):主要針對(duì)模擬信號(hào)受到干擾。