雖然25Gbps背板規(guī)范并未被發(fā)布,相關(guān)的SerDes也還未量產(chǎn),但光通信廠商早就開始了40Gbps DQPSK的應(yīng)用,將PCB上單一通道的速率推進(jìn)到20Gbps。背板方面,雖然國(guó)內(nèi)廠商只能拿到15Gbps的SerDes,但毫無(wú)疑問,不用多久,20Gbps以上的SerDes也會(huì)被開放。因此,本文將試圖對(duì)25Gbps無(wú)源通道設(shè)計(jì)時(shí)遇到的挑戰(zhàn)(尤其是在信號(hào)完整性方面)進(jìn)行分析和探討。

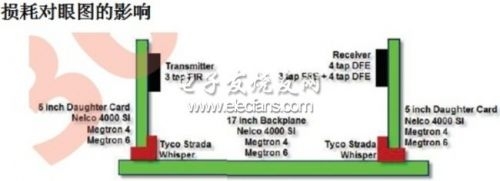

一個(gè)完整的25Gbps鏈路的構(gòu)成通常如圖1所示。

圖1:25Gbps完整鏈路示意,TP1~TP4為測(cè)試點(diǎn)。

25Gbps鏈路也是一個(gè)典型的點(diǎn)對(duì)點(diǎn)拓?fù)洌l(fā)射端和接收端均做了信號(hào)處理,即我們通常所說(shuō)的均衡。一般發(fā)射端被稱為加重,接收端被稱為均衡。其中發(fā)射端的加重又分為預(yù)加重和去加重;接收端的均衡又分為模擬均衡和數(shù)字均衡,分別為CTLE和DFE。發(fā)射端和接收端的均衡通常被用來(lái)補(bǔ)償數(shù)據(jù)在有損鏈路中傳輸時(shí)的損耗,以便在接收端獲得張開的眼圖以及符合規(guī)范的BER。25G無(wú)源通道主要被用于芯片間(chip-chip),芯片與模塊間(chip- module)或者背板的應(yīng)用中。在信號(hào)完整性方面遇到的挑戰(zhàn)主要包括傳輸損耗、反射和串?dāng)_。

對(duì)抗傳輸損耗

無(wú)源通道就像一個(gè)低通濾波器,總是會(huì)降低傳輸信號(hào)的幅度。信號(hào)在通過連接器、PCB走線、過孔、IC引腳和線纜等無(wú)源鏈路中的每一部分時(shí),總會(huì)造成幅度上的損失和抖動(dòng)的累積。當(dāng)信號(hào)到達(dá)接收端時(shí),眼圖通常已經(jīng)閉合(圖2、圖3)。作為鏈路的設(shè)計(jì)者,通常需要設(shè)法降低傳輸過程中的損耗,這也被稱為插損。以背板為例,25Gbps無(wú)源通道的損耗主要由高速連接器、過孔和走線造成。

圖2:CEI-25 LR鏈路示意圖。

圖3:興森快捷高速實(shí)驗(yàn)室25Gbps眼圖實(shí)測(cè):分別對(duì)應(yīng)于發(fā)射端、一半通道長(zhǎng)度以及接收端測(cè)得的眼圖。

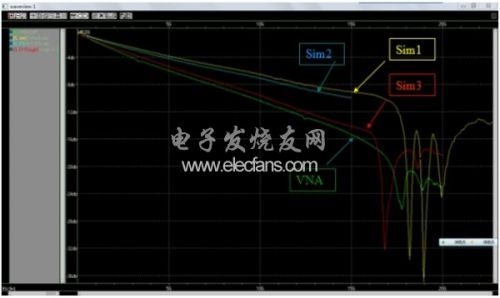

一旦選定了連接器,其本身的插損也就被確定下來(lái)。大多數(shù)背板連接器都采用壓接方式設(shè)計(jì),所以設(shè)計(jì)者唯一要做的就是盡可能地優(yōu)化過孔,將過孔的插損減到最小。由于連接器廠商一般會(huì)推薦連接器的布局(layout)方式,設(shè)計(jì)者能做的就是將過孔的分支(stub)減至最小,常見的方法有背鉆。除此之外,在實(shí)際的板級(jí)設(shè)計(jì)中,經(jīng)常會(huì)遇到表面微帶線轉(zhuǎn)換到帶狀線的做法,針對(duì)這種狀況要找出最優(yōu)的過孔實(shí)在不易。因?yàn)檫^孔在高速率下的模型非常復(fù)雜,而影響過孔的主要因素有孔徑、孔深、反焊盤和過孔鍍銅厚度。通常使用仿真軟件仿真不同過孔的S參數(shù),從而找出最優(yōu)的過孔。另外,過孔性能與頻率相關(guān)。在不同的上升沿下,過孔所表現(xiàn)的性能并不一樣,這時(shí)需要設(shè)計(jì)者對(duì)其做出一定的權(quán)衡和取舍。事實(shí)上,仿真和實(shí)測(cè)結(jié)果之間一般存在著誤差,并且有時(shí)誤差會(huì)相當(dāng)大,這一差異產(chǎn)生的原因是由于實(shí)際制造工藝并不能像仿真時(shí)那樣理想,在信號(hào)速率越高時(shí)越是如此。

不斷的仿真和測(cè)試可以幫助設(shè)計(jì)者找出最優(yōu)的過孔(圖4)。興森快捷公司在CPCA期間展示的100G以太網(wǎng)板,就是經(jīng)過兩版仿真和實(shí)測(cè)驗(yàn)證才找出的適合單通道28G速率的信號(hào)過孔。如果放在以前,在28G速率時(shí)竟然還能打孔設(shè)計(jì),這幾乎是天方夜譚。很多公司的設(shè)計(jì)規(guī)范里都有規(guī)定,10G速率的PCB布線不能打孔,這就是因?yàn)檫^孔的參數(shù)特性很難控制,人們?nèi)鄙俦匾氖侄魏蜅l件對(duì)其進(jìn)行研究和驗(yàn)證。為此,興森快捷的高速實(shí)驗(yàn)室投入了大量的人力與物力,致力于高速無(wú)源鏈路的研究,努力幫助客戶打通高速無(wú)源鏈路的設(shè)計(jì)瓶頸。

圖4:某板材損耗的仿真和實(shí)測(cè)對(duì)比:需要進(jìn)行多次仿真修正,才能縮小理論和實(shí)測(cè)之間的差距。

PCB布線是影響傳輸損耗的另一個(gè)關(guān)鍵因素。線上損耗的主要原因有:趨膚效應(yīng)、介質(zhì)損耗、銅箔粗糙度和波纖效應(yīng),這幾個(gè)因素均和信號(hào)的速率相關(guān)。在設(shè)計(jì)的初始階段,設(shè)計(jì)者便會(huì)借助軟件來(lái)計(jì)算PCB布線的阻抗和損耗。軟件通常都不會(huì)單獨(dú)考慮銅箔粗糙度的影響,或者將此影響歸類到趨膚效應(yīng)。而事實(shí)上,銅箔粗糙度和趨膚效應(yīng)存在著區(qū)別。當(dāng)速率達(dá)到10Gbps時(shí),銅箔粗糙度的影響便不可忽略。經(jīng)過興森快捷的高速實(shí)驗(yàn)室的測(cè)試驗(yàn)證,在25Gbps速率下,高粗糙度銅箔所產(chǎn)生的額外損耗往往會(huì)比低粗糙度銅箔高出很多。而在PCB制造時(shí),PCB廠商通常都會(huì)默認(rèn)為采用普通銅箔,也就是高粗糙度銅箔,這在高速設(shè)計(jì)時(shí)是常被忽略的地方。因?yàn)橐话愕腜CB工廠都不會(huì)去研究銅箔粗糙度的影響,興森快捷公司在這方面所做的研究工作已處于業(yè)界的前列。

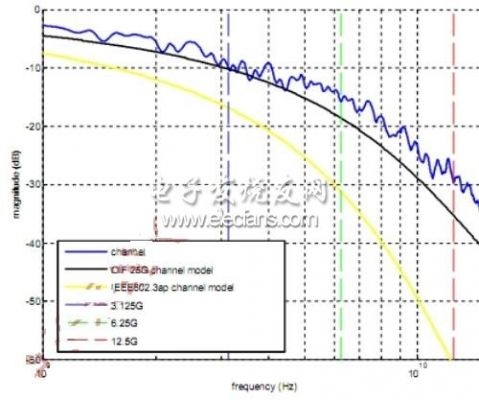

介質(zhì)的損耗將隨著頻率的升高而越變?cè)酱?圖5),這時(shí)能否找到一款性價(jià)比高的板材將成為成功的關(guān)鍵。因?yàn)椋谌绱烁叩乃俾氏拢词共捎靡郧坝糜?0G BASE KR的改性FR4板材(如 Nelco 4000-13)也將無(wú)法滿足要求,更不用說(shuō)普通的FR4。而業(yè)界原本廣為使用的Megtron 6也因?yàn)槿毡镜卣鸲艿胶艽笥绊懀詫ふ业揭豢羁商娲母哳l板材已迫在眉睫,而新材料的認(rèn)證又需要一個(gè)相對(duì)較長(zhǎng)的周期(需要做環(huán)境測(cè)試、插損測(cè)試、眼圖測(cè)試和BER測(cè)試等)。所要用到的儀器設(shè)備包括:恒溫箱、矢量網(wǎng)絡(luò)分析儀或TDR、碼型發(fā)生器、采樣示波器或?qū)崟r(shí)示波器以及BERT等。為了更好地對(duì) 25Gbps無(wú)源通道進(jìn)行量化和建模,興森快捷的高速實(shí)驗(yàn)室對(duì)此做了大量的研究工作,找出了性價(jià)比更高的Megtron 6替代板材,目前興森快捷還購(gòu)買了業(yè)界最大可探測(cè)面積的探針臺(tái),10G速率以上的超高速背板及系統(tǒng)的設(shè)計(jì)已變得更加容易。

圖5:CEI-25G LR規(guī)范規(guī)定的插損要比10G Base嚴(yán)格很多。10G Base只需要考慮6GHz時(shí)的損耗,而CEI-25G LR則需要考慮12.5GHz時(shí)的損耗。

在估算通道損耗時(shí),一般會(huì)認(rèn)為介質(zhì)是均勻的。事實(shí)上不同的疊層會(huì)使用不同厚度的PP(聚丙烯),不同厚度PP的構(gòu)成是不一樣的。PP主要由玻璃纖維和樹脂組成。波纖的經(jīng)緯交叉點(diǎn)和空隙中的樹脂含量不同,這會(huì)導(dǎo)致介質(zhì)的不均勻性,主要是波纖交叉點(diǎn)和空隙中的Dk和Df值區(qū)別很大。在最壞情況下,一對(duì)差分走線中的一根走在交叉線上,而另一根則走在空隙當(dāng)中,這樣差分對(duì)的傳輸延遲和損耗都會(huì)不同,這將造成眼圖的閉合和造成EMI。采用Intel推薦的10度角設(shè)計(jì)是一種常規(guī)的解決玻纖效應(yīng)的做法,但這通常被用于10G速率及以下,當(dāng)通道速率達(dá)到25Gbps時(shí),玻纖效應(yīng)對(duì)傳輸線的影響需要被更加嚴(yán)格地進(jìn)行評(píng)估。

此外,布線的方式也將影響到插損,比如傳輸線是微帶線還是帶狀線。兩者所帶來(lái)的損耗大不相同,在頻率越高的情況下區(qū)別會(huì)越大。除了損耗,兩種傳輸線周圍的電磁場(chǎng)分布以及傳播特性也不盡相同。總體而言,帶狀線會(huì)比微帶線具有更好的性能表現(xiàn),但前提條件是,必須設(shè)計(jì)出參數(shù)和特性均可控的過孔。

所有的影響因素均需要被考慮在內(nèi),才能符合規(guī)范要求。由于仿真和測(cè)試之間存在很大的差異,需要設(shè)計(jì)者不斷修正仿真模型和優(yōu)化算法,并反復(fù)和實(shí)測(cè)結(jié)果進(jìn)行對(duì)比,才能得到可信的仿真結(jié)果和經(jīng)驗(yàn)修正值。

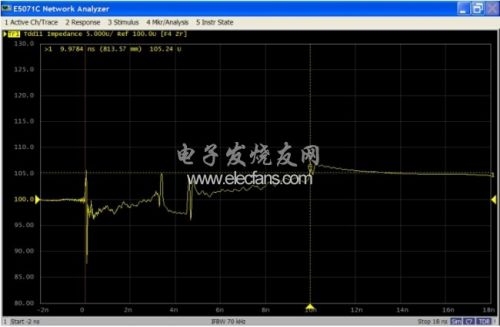

控制阻抗和反射

傳輸鏈路中只要存在阻抗不連續(xù),就會(huì)產(chǎn)生反射。S參數(shù)中用來(lái)表征反射的參數(shù)是S11,也就是常說(shuō)的回波損耗。設(shè)計(jì)者要做的就是盡可能的控制無(wú)源通道中的阻抗。布線的阻抗較易控制,難于控制之處主要在于過孔和連接器(圖6)。對(duì)于連接器來(lái)說(shuō),設(shè)計(jì)者可以控制的是分支(stub)的長(zhǎng)度。此長(zhǎng)度越長(zhǎng),阻抗越不連續(xù),反射將越厲害。對(duì)于背板,通常采用背鉆來(lái)保證。而對(duì)于過孔來(lái)說(shuō),除了要將其插損控制在最小值外,還要將其阻抗控制與傳輸線盡可能一致。

圖6:阻抗的不連續(xù)點(diǎn)分別由連接器和過孔所引起(興森快捷高速實(shí)驗(yàn)室的某實(shí)測(cè)案例)。

此外,反射不僅會(huì)引起過沖和振鈴等信號(hào)質(zhì)量的下降,而且還會(huì)給整個(gè)通道帶來(lái)額外的損耗。CEI-25G LR規(guī)范規(guī)定,回波損耗在整個(gè)奈奎斯特頻率范圍內(nèi)要約優(yōu)于-10dB,這樣回波損耗所引起的插損將被控制在約0.5dB以內(nèi)。而10G BASE GEN2則更是規(guī)定回?fù)p要約優(yōu)于-20dB,這樣回?fù)p所引起的插損才可忽略不計(jì)。

選擇有精密制造能力的供應(yīng)商也至關(guān)重要。只有嚴(yán)格按照設(shè)計(jì)意圖進(jìn)行生產(chǎn)制造的PCB,才能更好地保證阻抗可控。對(duì)于阻抗受控的PCB,PCB板廠商通常采用在PCB旁附加測(cè)試條(通常稱為附連邊)來(lái)測(cè)試傳輸線的阻抗。對(duì)這一點(diǎn)設(shè)計(jì)者需要尤其注意,某些時(shí)候測(cè)試條上的傳輸線阻抗和PCB上的傳輸線阻抗并不能良好地對(duì)應(yīng),需要設(shè)計(jì)者在設(shè)計(jì)PCB時(shí)保證設(shè)計(jì)的正確性。目前國(guó)內(nèi)已有極個(gè)別廠商能夠直接檢驗(yàn)PCB板上的阻抗連續(xù)性(并非檢驗(yàn)測(cè)試條上的阻抗)。

多通道串?dāng)_

由于下一代100Gbps 網(wǎng)絡(luò)大多會(huì)采用4 x 25Gbps的架構(gòu),所以相鄰?fù)ǖ篱g的串?dāng)_表征將無(wú)法避免。由于走線間的距離可以通過犧牲布線密度來(lái)調(diào)節(jié),所以鏈路上串?dāng)_最大的地方仍將發(fā)生在連接器端。串?dāng)_不僅會(huì)在幅度上帶來(lái)噪聲,同時(shí)還會(huì)引起時(shí)序上的抖動(dòng),這造成無(wú)用信號(hào)反射等信號(hào)的完整性問題。

對(duì)串?dāng)_進(jìn)行仿真是一個(gè)難題,難度主要體現(xiàn)在高速連接器的串?dāng)_建模不易。一般連接器廠商給出的S參數(shù)或Spice模型僅局限于連接器的本身,當(dāng)裝配到 PCB(如背板)以后,模型的精確建立和修正將形成挑戰(zhàn)。材料特性、幾何尺寸、是否背鉆和過孔加工精度都將成為決定性因素。而當(dāng)串?dāng)_模型被比較準(zhǔn)確地建立起來(lái)之后,又將出現(xiàn)另一個(gè)挑戰(zhàn),那就是多通道碼型信號(hào)的生成。要生成各種不同長(zhǎng)度的碼型,以及確定是否帶有噪聲和抖動(dòng)等壓力信號(hào),需要不停地改變或掃描不同通道之間的相位、偏斜和延遲,以找出串?dāng)_的最壞情況。

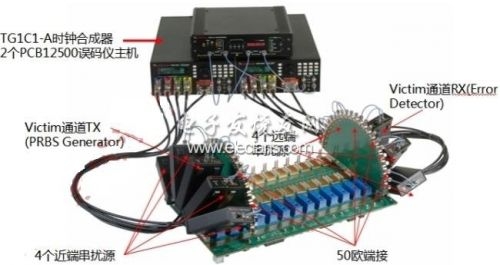

除了仿真,也可以測(cè)試實(shí)際鏈路中的串?dāng)_,這樣也能驗(yàn)證仿真的正確性。對(duì)于串?dāng)_的測(cè)試,傳統(tǒng)上采用VNA或TDR來(lái)測(cè)試物理結(jié)構(gòu)上的串?dāng)_,但所測(cè)得的串?dāng)_大小與數(shù)據(jù)無(wú)關(guān)。也就是說(shuō),無(wú)論是VNA測(cè)試出來(lái)的串?dāng)_幅度,還是TDR測(cè)試出來(lái)的串?dāng)_最強(qiáng)耦合位置,均不能直接指示出是否引起了誤碼或眼圖的惡化。要測(cè)試數(shù)據(jù)的相關(guān)串?dāng)_,需要借助并行通道誤碼儀(圖7)。由于該設(shè)備可以級(jí)聯(lián),所以能夠測(cè)試多達(dá)8個(gè)以上干擾通道的情況。

圖7所示的配置可以將數(shù)據(jù)相關(guān)的串?dāng)_很好的表征出來(lái),包括改變碼型發(fā)生器的幅度和去加重,得出浴盆曲線,從而找出串?dāng)_對(duì)數(shù)據(jù)的最壞影響以及減少串?dāng)_和抖動(dòng)的辦法。興森快捷高速實(shí)驗(yàn)室已利用此設(shè)備多次幫助客戶成功地設(shè)計(jì)出了高速背板并通過了驗(yàn)證。

本文小結(jié)

當(dāng)高速串行信號(hào)速率急速增進(jìn)到25Gbps后,發(fā)射端和接收端的信號(hào)處理將更加復(fù)雜。由于傳輸?shù)男盘?hào)仍然是NRZ 碼型,發(fā)射端采用3抽頭(tap)的預(yù)加重,接收端采用3抽頭以上的CTLE和DFE兩級(jí)均衡來(lái)克服通道上的損耗。而要最優(yōu)化配置發(fā)射端和接收端的均衡,則需了解到通道的損耗情況。設(shè)計(jì)者只需要考慮到影響損耗的各種因素,做好充分的仿真和測(cè)試,便可以做到通道可控,包括大家所熟悉的阻抗控制、損耗控制和串?dāng)_控制。設(shè)計(jì)出的通道不僅要滿足規(guī)范,而且還要留有充足的裕量。這樣不僅不會(huì)給有源部分造成壓力,而且還會(huì)為未來(lái)的速率擴(kuò)展和升級(jí)留下余地。