工藝與材料的創(chuàng)新

隨著時間的推移,,功率晶體管技術得到了持續(xù)的改善。器件的體積不斷縮小,,功率密度越來越高,。在電壓高于1 kV的大功率晶體管方面,雙極結構已成為首選,;低于1 kV電壓,,特別是頻率高于100 kHz時,,更多采用的是MOSFET。高于此電壓的大電流應用則選擇IGBT,。

開發(fā)這類器件的主要挑戰(zhàn)在于,,在開關頻率持續(xù)上升時,需要通過減小由導通阻抗導致的導電損耗,、降低內(nèi)部電容,,以及改善反向恢復性能,將內(nèi)部損耗降到最低,。由于擊穿電壓更高及未鉗位開關特性(UIS)的緣故,,提升擊穿強固性也非常重要。

以往,,開發(fā)電壓低于40 V的低壓MOSFET的重點在于,,給定導通阻抗條件下將裸片尺寸減至最小,從而降低單位成本,。因此,,最重要的質(zhì)量因子(Figure of Merit, FOM)就是單位為mΩ x mm2的特征導通阻抗(RDS(ON)spec),。由于低壓FET中溝道阻抗(channel resistance)對特征導通阻抗有較大影響,,業(yè)界主要致力于在可用面積上配置盡可能多的FET溝道。平面溝道被垂直“溝槽門”溝道替代,,同時使用先進的光刻技術來縮小表面尺寸。

但是,,減小溝槽FET間距的方法并不能輕松達到采用RDS(ON)xQg(d)定義的關鍵質(zhì)量因子,,因為單位面積上的導通阻抗方面的改進被單位面積門電荷(Qg)增加所抵消。因此,,開發(fā)就轉(zhuǎn)向了諸如溝槽FET(帶有額外解耦垂直場效電板從漏極屏蔽門極),、溝槽LDMOS(結合了溝槽MOS的緊湊性及背面漏極與LDMOS的較低Qg(d)),以及優(yōu)化了金屬化/封裝的LDMOS等架構,。

雖然多年來基于硅的晶體管有了持續(xù)改進,,但硅基材料特性上的限制表明,未來十年人們還需要尋求其它可用方案,。目前,,利用寬帶隙材料(氮化鎵、碳化硅及鉆石)的方案已經(jīng)出現(xiàn),。這些材料可以提供更好的熱特性,,開關損耗更低,而且結合了更有吸引力的低導通阻抗(RDS(ON))和高擊穿電壓(VBD)性能的優(yōu)勢,。

寬帶隙材料也可以在高壓應用中實現(xiàn)重大突破,。氮化鎵和碳化硅的臨界擊穿場的數(shù)量級高于硅,,迄今發(fā)布的器件也具有熱導率更高(比硅高約3倍)的優(yōu)勢。在高于1 kV的應用中碳化硅是首選材料,,而氮化鎵則最適于電壓低于1 kV的應用,。然而,仍然需要克服一些技術障礙,,如增加硅上厚氮化鎵層以提供高額定電壓,、制造增強模式晶體管及提升可靠性等。預計未來幾年,,首批高壓氮化鎵高電子遷移率晶體管(HEMT)就會上市,。

工藝與材料的創(chuàng)新

隨著時間的推移,功率晶體管技術得到了持續(xù)的改善,。器件的體積不斷縮小,,功率密度越來越高。在電壓高于1 kV的大功率晶體管方面,,雙極結構已成為首選,;低于1 kV電壓,特別是頻率高于100 kHz時,,更多采用的是MOSFET,。高于此電壓的大電流應用則選擇IGBT。

開發(fā)這類器件的主要挑戰(zhàn)在于,,在開關頻率持續(xù)上升時,,需要通過減小由導通阻抗導致的導電損耗、降低內(nèi)部電容,,以及改善反向恢復性能,,將內(nèi)部損耗降到最低。由于擊穿電壓更高及未鉗位開關特性(UIS)的緣故,,提升擊穿強固性也非常重要,。

以往,開發(fā)電壓低于40 V的低壓MOSFET的重點在于,,給定導通阻抗條件下將裸片尺寸減至最小,,從而降低單位成本。因此,,最重要的質(zhì)量因子(Figure of Merit,, FOM)就是單位為mΩ x mm2的特征導通阻抗(RDS(ON)spec)。由于低壓FET中溝道阻抗(channel resistance)對特征導通阻抗有較大影響,,業(yè)界主要致力于在可用面積上配置盡可能多的FET溝道,。平面溝道被垂直“溝槽門”溝道替代,同時使用先進的光刻技術來縮小表面尺寸。

但是,,減小溝槽FET間距的方法并不能輕松達到采用RDS(ON)xQg(d)定義的關鍵質(zhì)量因子,,因為單位面積上的導通阻抗方面的改進被單位面積門電荷(Qg)增加所抵消。因此,,開發(fā)就轉(zhuǎn)向了諸如溝槽FET(帶有額外解耦垂直場效電板從漏極屏蔽門極),、溝槽LDMOS(結合了溝槽MOS的緊湊性及背面漏極與LDMOS的較低Qg(d)),以及優(yōu)化了金屬化/封裝的LDMOS等架構,。

雖然多年來基于硅的晶體管有了持續(xù)改進,,但硅基材料特性上的限制表明,未來十年人們還需要尋求其它可用方案,。目前,,利用寬帶隙材料(氮化鎵、碳化硅及鉆石)的方案已經(jīng)出現(xiàn),。這些材料可以提供更好的熱特性,,開關損耗更低,而且結合了更有吸引力的低導通阻抗(RDS(ON))和高擊穿電壓(VBD)性能的優(yōu)勢,。

寬帶隙材料也可以在高壓應用中實現(xiàn)重大突破,。氮化鎵和碳化硅的臨界擊穿場的數(shù)量級高于硅,迄今發(fā)布的器件也具有熱導率更高(比硅高約3倍)的優(yōu)勢,。在高于1 kV的應用中碳化硅是首選材料,,而氮化鎵則最適于電壓低于1 kV的應用。然而,,仍然需要克服一些技術障礙,,如增加硅上厚氮化鎵層以提供高額定電壓、制造增強模式晶體管及提升可靠性等,。預計未來幾年,,首批高壓氮化鎵高電子遷移率晶體管(HEMT)就會上市。

功率器件更加智能

智能電源IC (Smart power IC)是一種在一塊芯片上將“智能”和“電源”集成起來的全新器件,。它廣泛應用于包括電源轉(zhuǎn)換器、馬達控制,、熒光燈整流器,、自動開關、視頻放大器,、橋式驅(qū)動電路以及顯示驅(qū)動等多個領域,。

中國是全球最大的消費電子產(chǎn)品市場,各種電子產(chǎn)品的需求與日俱增,,這預示著智能電源IC將有巨大的市場,。

智能電源IC采用結合型雙極/CMOS/DMOS(BCD)工藝,使模擬,、數(shù)字及電源方面的系統(tǒng)設計能夠集成在單片襯底上,。后續(xù)的BCD工藝改善了高壓隔離,、數(shù)字特征尺寸(提供更高模擬精度、邏輯速度與密度等)及功率處理能力?,F(xiàn)代工藝能夠集成數(shù)字處理器,、RAM/ROM內(nèi)存、內(nèi)嵌式內(nèi)存及電源驅(qū)動器,。例如,,采用BCD工藝可以在單芯片上集成電源、邏輯及模擬等功能,。

隨著CMOS幾何尺寸的持續(xù)縮小,,高內(nèi)嵌智能的需求導致了16/32位處理器、多Mb ROM/RAM/非易失性內(nèi)存,,及復雜IP的集成,。為了模組更高精度感測機制、高比特率數(shù)據(jù)轉(zhuǎn)換,、不同接口協(xié)議,、預驅(qū)動器/控制環(huán)路,及精確片上電壓/電流參考的需求,,模擬功能也在不斷增多,。業(yè)界已經(jīng)推出了100至200 V及5至10 A的電源驅(qū)動器。這些器件帶有低導通阻抗,,及利用深溝槽及絕緣硅(SOI)技術的高密度,、強固型高壓隔離架構。

用于AC-DC逆變器的集成型600 V晶體管技術與用于低于100 V應用的技術相輔相成,,被證明是另一個重要市場,。先進的亞微米CMOS工藝將推動低成本、低導通阻抗驅(qū)動器的集成從傳統(tǒng)LDMOS器件轉(zhuǎn)向雙及三低表面電場(RESURF) DMOS,、超結LDMOS及LIGBT,。 【 查看本站相關專題:功率器件在綠色節(jié)能設計中的應用【IGBT、MOSFET】 】

封裝技術潛力無限

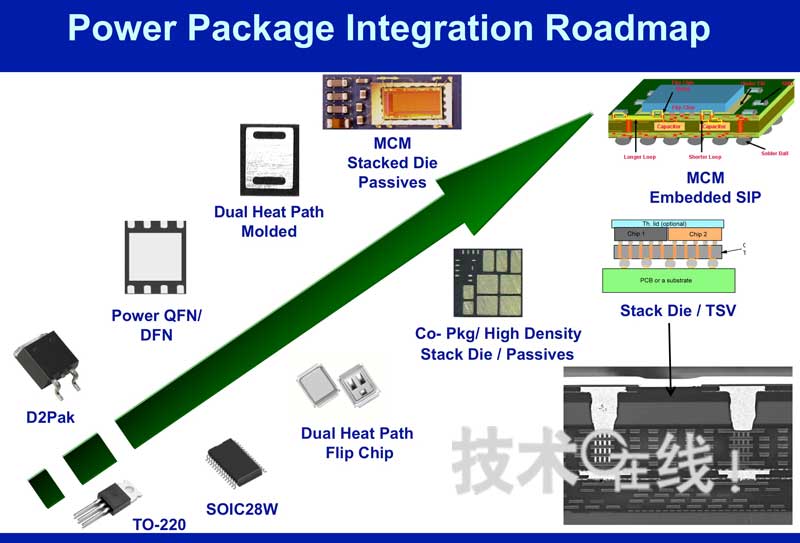

當前功率半導體封裝的主要趨勢是增強互連,,包括旨在降低阻抗/寄生效應的晶圓級技術,,以及增強型片上散熱。厚銅,、金或鋁線邦定,、緞帶(ribbon)/封裝黏著(clip bonding) ,以及功率優(yōu)化的芯片級封裝(CSP),,也在增強裸片與外部電極之間的電阻連接效率,。圖1顯示了封裝技術的演進。

圖1 功率封裝集成路線圖

功率模塊本身就是功率電子器件按一定功能組合灌封而成。說它是一種封裝技術一點也不為過,。早期的功率模塊在單個封裝中集成了多個閘流體/整流器,,從而提供更高的額定功率。過去三十年來的重大突破使當今的模塊將功率半導體與感測,、驅(qū)動,、保護及控制功能結合在一起。例如,,智能功率模塊就是以IGBT為內(nèi)核的先進混合集成功率部件,,由高速低功耗管芯(IGBT)和優(yōu)化的門極驅(qū)動電路,以及快速保護電路構成,。IPM內(nèi)的IGBT管芯都選用高速型的,,而且驅(qū)動電路緊靠IGBT,驅(qū)動延時小,,所以IPM開關速度快,,損耗小。IPM內(nèi)部集成了能連續(xù)檢測IGBT電流和溫度的實時檢測電路,,當發(fā)生嚴重過載甚至短路,,以及溫度過熱時,IGBT將被有控制地軟關斷,,同時發(fā)出故障信號,。此外,IPM還具有橋臂對管互鎖,、驅(qū)動電源欠壓保護等功能,。盡管IPM價格高一些,但由于集成了驅(qū)動和保護功能,,因此比單純的IGBT具有結構緊湊,、可靠性高、易于使用等優(yōu)點,。

模塊采用的直接敷銅(DBC)技術增強了電氣性能,,而陶瓷襯底(如三氧化二鋁及氮化鋁)能夠同時提升冷卻效率。封裝-組裝技術上的改進也實現(xiàn)了幾個裸片和無源器件的平面共同集成(co-integration),,以及旨在增加系統(tǒng)集成度的垂直堆棧技術,。“解開封裝”(Un-packaging)技術是另一個有意義的研究領域,此技術將幾個布有器件的(populated)的襯底機械集成,,無需殼體、端子及基座,。

持續(xù)推動工藝技術進步

許多廠商都在積極開發(fā)新的工藝技術,。例如,安森美半導體開發(fā)出了專有Trench 3工藝的下一代MOSFET產(chǎn)品,可用于臺式機,、筆記本和上網(wǎng)本等應用,,有助于提升能效及開關性能,同時裸片尺寸更小,。

未來幾年,,安森美還將開發(fā)氮化鎵的晶圓生產(chǎn)工藝/器件集成工藝/制造工藝/封裝工藝、絕緣硅晶圓生產(chǎn)工藝,、接觸/隔離溝槽工藝模塊,、低電感封裝、電感和電容集成等工藝技術,;同時利用封裝技術實現(xiàn)產(chǎn)品創(chuàng)新,,以更纖薄的封裝、更低占位面積實現(xiàn)更高I/O密度,,不斷提高封裝熱效率及工作溫度范圍,,也使每個封裝的裸片尺寸選擇更多。此外,,還將以更薄,、直徑更大的晶圓和銅線夾來降低材料成本。