關(guān)鍵字:數(shù)字信號(hào)處理;ADS8482;可編程邏輯;信號(hào)采集

慣性測(cè)量裝置中,加速度計(jì)信號(hào)的精確檢測(cè)直接影響到慣性裝置的精度,因此提高測(cè)量加速度信號(hào)精度尤為重要。目前加速度計(jì)信號(hào)的檢測(cè)主要采用I/F變換檢測(cè)技術(shù),測(cè)量精度高。但電路復(fù)雜,不適合慣性測(cè)量裝置的小型化,以及中低精度慣性器件的大批量生產(chǎn)。因此,這里提出一種基于A/D轉(zhuǎn)換器ADS8482和TMS320F28335的加速度計(jì)信號(hào)采集系統(tǒng)設(shè)計(jì)方案。

1 系統(tǒng)組成及主要器件介紹

圖l該信號(hào)采集系統(tǒng)的硬件組成框圖。采樣信號(hào)經(jīng)前級(jí)調(diào)理電路,以單端輸入方式輸入至A/D轉(zhuǎn)換器ADS8482進(jìn)行采集。ADS8482采用18位數(shù)據(jù)總線輸出,直接與TMS320F28335數(shù)據(jù)線相連,電路的控制部分與引腳電平兼容,是由EPM7128型CPLD實(shí)現(xiàn)。采集到的數(shù)據(jù)通過(guò)DSP片上串口輸出。

ADS8482型逐次比較A/D轉(zhuǎn)換器輸出數(shù)據(jù)總線方式可配置成8,16和18位。內(nèi)部提供采樣時(shí)鐘,其采樣吞吐率為l MS/s。內(nèi)部提供4.096 V的參考電壓,模擬信號(hào)輸入,全輸入差分范圍為±4.096 V。TMS320F28335型單精度浮點(diǎn)DSP主頻可達(dá)150 MHz,內(nèi)核電壓1.9 V,I/O電壓3.3 V;片上帶有256 KB的16位Flash和34 KB的16位SARAM,并有128位安全密碼鑰匙/鎖,保護(hù)Flash防止固件反向工程。片上通訊端口豐富,集成有3個(gè)SCI串口輸出通道,并帶有16字節(jié)的FIFO,2個(gè)多通道McBSP串口,2個(gè)增強(qiáng)型CAN,1個(gè)SPI總線。還帶有16通道的12位A/D轉(zhuǎn)換器等資源。

2 系統(tǒng)硬件設(shè)計(jì)

2.1 前級(jí)調(diào)理電路

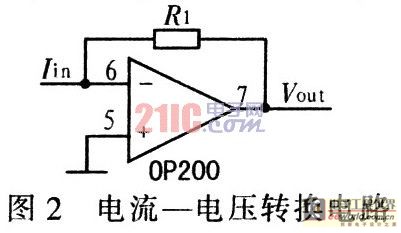

本系統(tǒng)是針對(duì)加速度計(jì)信號(hào)采集而設(shè)計(jì)的。由于加速度計(jì)傳感器一般輸出的電流信號(hào)非常微弱,ADS8482是電壓形式的A/D轉(zhuǎn)換器,因此前級(jí)電路需設(shè)計(jì)一個(gè)電流轉(zhuǎn)換電壓電路。采用運(yùn)放檢測(cè)電流有2種方法:一是利用電流在電阻上的壓降,再進(jìn)行電壓放大,但該方法所引入的電阻將破壞電路原來(lái)的狀態(tài),造成測(cè)量誤差;二是運(yùn)放的失調(diào)電壓也被運(yùn)放放大帶入到后級(jí)電路。因此這里采用輸入電流直接接入運(yùn)放的反相輸入的求和點(diǎn)。如圖2所示。

該電路的誤差主要來(lái)自于運(yùn)放的輸入偏置電流,并和輸入電流Iin相疊加引入后級(jí)電路。每一級(jí)模擬前端電路都會(huì)對(duì)已處理的信號(hào)增加噪聲和失真,則直接影響到A/D轉(zhuǎn)換器的精度,因此前級(jí)電路的運(yùn)放選用低噪聲,低偏置電壓和低偏置電流的OP200配置設(shè)計(jì)。

關(guān)鍵字:數(shù)字信號(hào)處理;ADS8482;可編程邏輯;信號(hào)采集

2.2 ADS8482與TMS320F28335接口及外圍電路

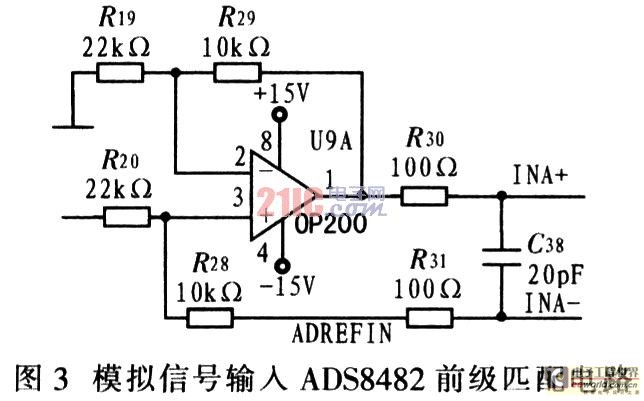

由于加速度計(jì)電流信號(hào)帶有極性,采用ADS8482采集正負(fù)信號(hào)需要配置設(shè)計(jì)輸入的模擬電壓信號(hào)。由于ADS8482的+IN和-IN引腳接收的輸入電壓為0~4.096 V,不能輸入負(fù)電壓,因此選用REF3020參考電壓器件,其輸出的2.048 V輸入至-IN引腳,此參考電壓也為TMS320F28335片上A/D轉(zhuǎn)換器提供參考電壓基準(zhǔn)。具體電路如圖3所示,電容C38用于濾除高頻噪音,以提高信噪比,ADRFIN為2.048 V。模擬信號(hào)輸入與數(shù)字量輸出的關(guān)系是:引腳+IN和-IN的電壓差在-Vref~+Vref范圍內(nèi),對(duì)應(yīng)的數(shù)字量在-131 073~13l 072。

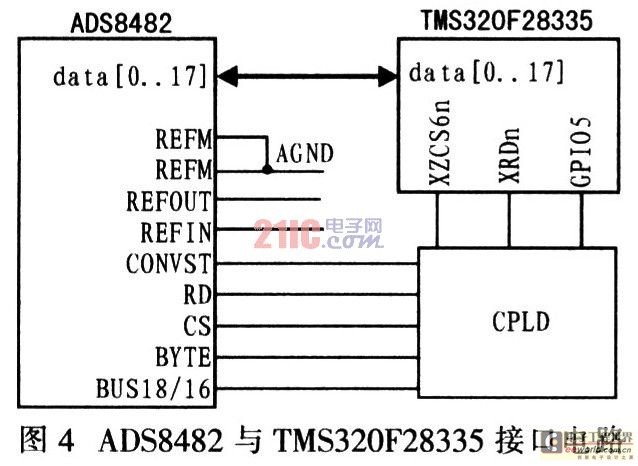

A/D轉(zhuǎn)換器ADS8482采用+5 V的模擬電源(+VA)和數(shù)字電源(+VDB)。引腳+VDB可直接連接至3 V或5 V電壓系統(tǒng)。而TMS320F28335的I/O電壓為+3.3 V,因此,ADS8482的引腳+VDB必須設(shè)置成3.3 V。該設(shè)計(jì)的參考基準(zhǔn)電壓引用片上輸出,數(shù)據(jù)總線配置成18位,一次讀操作模式。因此ADS8482的BUSl8/16,BYTE引腳由CPLD控制,全設(shè)置為O。其具體接口電路如圖4所示。

TMS320F28335的XZCS6和XRDn讀信號(hào)經(jīng)CPLD與門等設(shè)置連接到ADS8482片選信號(hào)CS和讀信號(hào)RD上,因此0x100000~Ox200000的任意一個(gè)地址都可對(duì)A/D轉(zhuǎn)換器進(jìn)行讀操作。ADS8482的啟動(dòng)轉(zhuǎn)換信號(hào)CONVST經(jīng)CPLD配置到DSP的一個(gè)I/O引腳,通過(guò)軟件程序控制啟動(dòng)A/D轉(zhuǎn)換器。AD-S8482轉(zhuǎn)換參考電壓利用片上參考電壓輸出作為輸入。將引腳REFOUT連接到運(yùn)放的正輸入端,設(shè)計(jì)一個(gè)電壓跟隨環(huán)節(jié),將輸出電壓直接連接到ADS8482引腳的REFIN上。模擬信號(hào)進(jìn)入A/D采樣端前,用二極管進(jìn)行保護(hù),防止輸入電壓過(guò)大,以免ADS8482損壞。

關(guān)鍵字:數(shù)字信號(hào)處理;ADS8482;可編程邏輯;信號(hào)采集

3 軟件程序設(shè)計(jì)

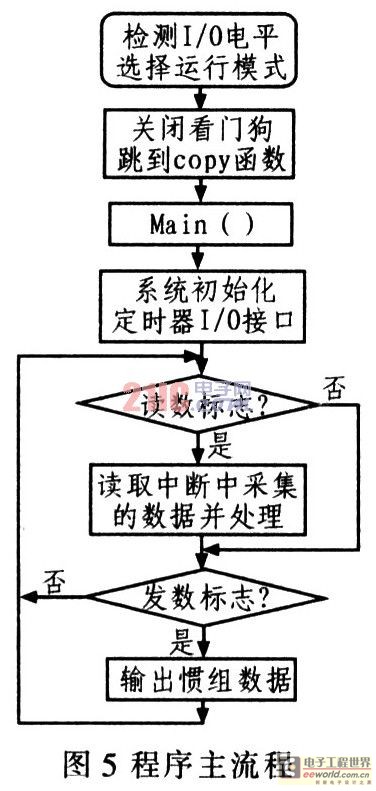

TMS320F28335上電通過(guò)檢測(cè)A12~A15電平來(lái)選擇工作模式,本程序是從片內(nèi)。Flash啟動(dòng),因此在CPLD中將這些I/O接口設(shè)置為高電平。上電后先裝載,把Flash中的程序搬移到片內(nèi)低16 KB RAM中運(yùn)行。主程序完成數(shù)據(jù)讀取和處理運(yùn)算,并將處理后的數(shù)據(jù)用TMS320F28335片上自帶的一路串口按4 ms輸出至PC機(jī),波特率配置成115.2 Kb/s,并使能串口16字節(jié)的FIFO。圖5為程序主流程。

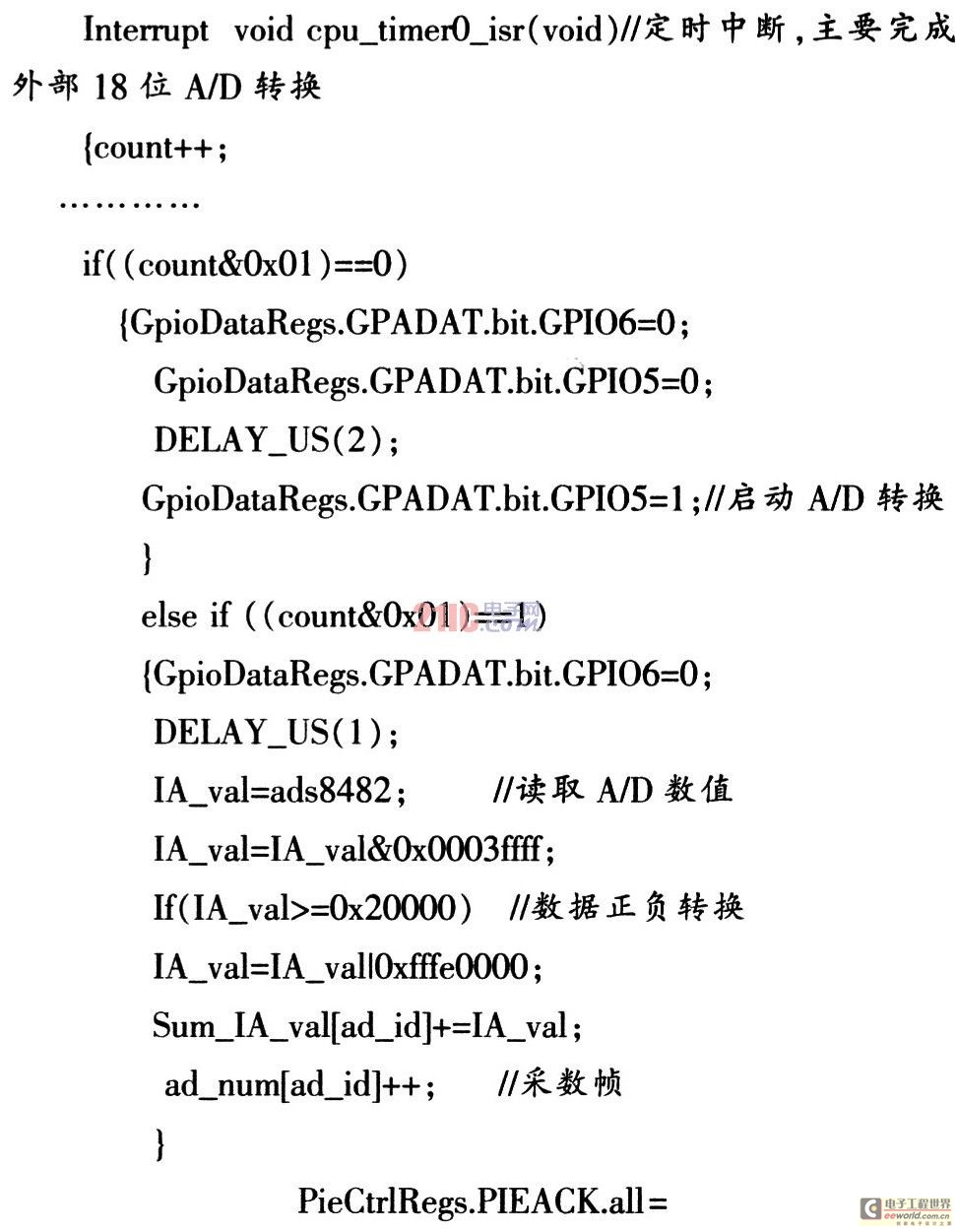

利用TYMS320F28335中的定時(shí)器TO,完成系統(tǒng)4 ms定時(shí)和ADS8482定時(shí)采數(shù)方式,每50 μs發(fā)生一次定時(shí)器中斷。中斷函數(shù)部分采數(shù)代碼如下:

4 結(jié)束語(yǔ)

本文以ADS8482型A/D轉(zhuǎn)換器與TMS320F28335在加速度信號(hào)采集中應(yīng)用為基礎(chǔ),詳細(xì)討論ADS8482與TMS320F28335的接口設(shè)計(jì)和工作原理,并提供該系統(tǒng)設(shè)計(jì)的部分硬件設(shè)計(jì)和軟件代碼。該設(shè)計(jì)方案也可用于其他高速數(shù)據(jù)采集,以及微弱信號(hào)檢測(cè)信號(hào)等場(chǎng)合。