引言

磁通門傳感器最早于1935年發(fā)明并投入應(yīng)用,用于靜態(tài)或者低頻變化的弱磁檢測,擁有其他磁敏元件難以媲美的靈敏度和可靠性,在磁場測量領(lǐng)域一直占據(jù)著不可替代的位置。磁通門傳感器適用于地磁或人體磁場的檢測,在航空、航天、地質(zhì)勘探、醫(yī)療衛(wèi)生等領(lǐng)域有著廣泛的應(yīng)用。

磁通門傳感器探頭通常采用類似于變壓器的雙鐵芯結(jié)構(gòu),利用軟磁鐵芯變化磁導(dǎo)率的特性將被測磁場調(diào)制成激勵信號的偶次諧波。信號處理系統(tǒng)對探頭輸出加以處理,從中提取與被測磁場大小相關(guān)的信號,轉(zhuǎn)換成直流量并輸出。

傳統(tǒng)的磁通門信號處理電路采用模擬元器件,溫度性能嚴(yán)重地受到影響,且很難小型化,可移植性也很差。與之相比,現(xiàn)代數(shù)字磁通門系統(tǒng),溫度性能穩(wěn)定,體積小,可移植性強。根據(jù)應(yīng)用的具體情況,可選的實現(xiàn)方式多樣,有單片機、可編程數(shù)字邏輯,或數(shù)字信號處理(DSP)芯片等。

FPGA(Field Programmable Gate Array)是一種高速的可編程邏輯芯片,具有其他設(shè)備難以比擬的靈活性,其大部分引腳的功能、內(nèi)部電路結(jié)構(gòu)完全由用戶根據(jù)需要定義。FPGA器件具有很高的實用價值,一方面可以作為專用集成電路的替代品,直接在最終產(chǎn)品中使用,另一方面,也可以在專用集成電路開發(fā)流程中,做行為驗證工具。

在本文中,描述了一種基于FPGA的磁通門系統(tǒng)的實現(xiàn),系統(tǒng)采用閉環(huán)結(jié)構(gòu),對磁通門傳感器探頭輸出的數(shù)據(jù)進(jìn)行實時處理,提取出反映被測低頻磁場大小的直流信號。

1 磁通門系統(tǒng)結(jié)構(gòu)和工作原理

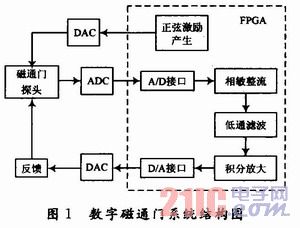

如圖1所示,整個系統(tǒng)的硬件包括磁通門傳感器探頭,DAC,ADC和FPGA。功能上可分為傳感器激勵源、磁通門信號解算、負(fù)反饋回路三個模塊。

FPGA內(nèi)的正弦激勵發(fā)生電路和外部DAC一起構(gòu)成傳感器激勵源模塊。高速ADC和FPGA內(nèi)的A/D接口、相敏整流、低通濾波電路構(gòu)成磁通門信號解算模塊。積分放大、D/A接口、高速DAC,以及反饋網(wǎng)絡(luò)共同構(gòu)成了負(fù)反饋模塊。

系統(tǒng)工作時,在激勵信號的驅(qū)動下,磁通門探頭的感應(yīng)線圈感應(yīng)環(huán)境磁場大小,產(chǎn)生磁通門信號,經(jīng)隔直濾波后通過高速ADC芯片轉(zhuǎn)換成串行數(shù)據(jù)送FPGA的處理。在FPGA中,ADC芯片采集到的串行數(shù)據(jù)先轉(zhuǎn)換成并行數(shù)據(jù),然后通過相敏整流、低通濾波后得到直流信號。低通濾波的結(jié)果積分放大后經(jīng)D/A接口轉(zhuǎn)換成串行數(shù)據(jù)送高速DAC芯片轉(zhuǎn)換成模擬信號,經(jīng)反饋電阻反饋到磁通門探頭的補償線圈(即感應(yīng)線圈),抵消環(huán)境磁場。

由于采用閉環(huán)結(jié)構(gòu),前向通道上積分放大環(huán)節(jié)的增益可視作無窮大,根據(jù)自動控制原理,整個系統(tǒng)是無差系統(tǒng),傳感器探頭實際上工作在“零場”條件下,反饋電流產(chǎn)生的磁場和環(huán)境磁場大小相的方向相反,D/A的前端信號,即積分放大環(huán)節(jié)的輸出反映被測磁場的大小。整個系統(tǒng)的信號梯度主要取決于反饋系數(shù)的大小,具有良好的線性度。

2 磁通門信號的特點和處理方法

磁通門系統(tǒng)的核心是信號處理電路。

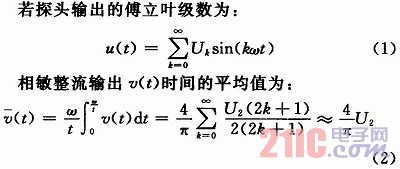

磁通門傳感器探頭輸出的偶次諧波(以二次為主)是有用的磁通門信號,而其他頻率的信號都是有害噪聲。在實際應(yīng)用中,通常采用“相敏整流-低通濾波”方法處理磁通門信號。首先用相敏整流進(jìn)行頻譜的調(diào)整,通過采用與二次諧波同頻率的方波基準(zhǔn)乘傳感器探頭的輸出,將二次諧波磁通門信號轉(zhuǎn)換為直流分量,然后用低通濾波濾除其他頻率分量,得到反映被測磁場大小的直流量。

低通濾波器輸出是相敏整流結(jié)果的直流分量,與磁通門傳感器探頭輸出的二次諧波的幅值線性相關(guān),反映被測磁場大小。

3 硬件電路設(shè)計

在該設(shè)計中,F(xiàn)PGA芯片選用Altera公司CYCLONEⅡ系列的EP2C35F626C5,工作速度快,可定義引腳豐富,邏輯單元數(shù)量可觀,性價比高。FPGA的工作時鐘為50 MHz。

磁通門激勵起到驅(qū)動傳感器工作的作用,由D/A模塊轉(zhuǎn)換FPGA輸出的正弦數(shù)字信號產(chǎn)生;本設(shè)計中,激勵頻率為3.051 kHz,是FPGA工作時鐘的64×256分頻,速度相對較低,且精度要求不高,故DAC采用12位并口DA1210芯片。

在閉環(huán)系統(tǒng)的前向通道中,A/D模塊是偏差檢測環(huán)節(jié),對傳感器探頭輸出進(jìn)行采樣。該設(shè)計中,二次諧波一個周期采樣128個點,即ADC采樣頻率是探頭輸出二次諧波頻率的128倍,也就是781.25 kHz。采用AD7980芯片作為A/D轉(zhuǎn)換器,該芯片具有16位精度,轉(zhuǎn)換速度高達(dá)1 MSPS,可以滿足要求。

在反饋回路中,D/A模塊作為低頻補償環(huán)節(jié),需要具有較高的精度,而轉(zhuǎn)換速率可以較低;該設(shè)計采用DA8552芯片,具有16位精度和100 KSPS的轉(zhuǎn)換速率。

4 FPGA內(nèi)部電路設(shè)計

4.1 A/D接口和D/A接口

由于前向通道的ADC芯片、反饋回路的DAC芯片都采用串口通信,因此設(shè)計了專用的A/D接口和D/A接口,實現(xiàn)了A/D輸入和D/A輸出的串并/并串轉(zhuǎn)換。

4.2 正弦激勵發(fā)生

正弦激勵發(fā)生采用查表的方式實現(xiàn)。用12×256b的ROM存一幅12位正弦波表,以FPGA時鐘頻率的1/64,即781.25kHz掃描,產(chǎn)生3.051 kHz的12位數(shù)字正弦信號。

4.3 磁通門信號解算和積分放大

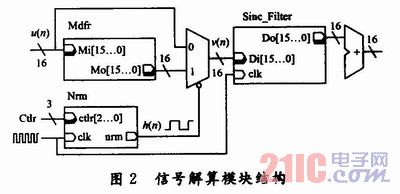

磁通門信號的解算是FPGA內(nèi)數(shù)字邏輯最核心的功能,由相敏整流器、基準(zhǔn)發(fā)生器和FIR數(shù)字濾波器三部分共同實現(xiàn),如圖2所示。

相敏整流器由數(shù)據(jù)轉(zhuǎn)換器和數(shù)據(jù)選擇器構(gòu)成。數(shù)據(jù)轉(zhuǎn)換器.Mdfr將輸入u(n)轉(zhuǎn)換成補碼形式。輸出v(n)是輸入u(n)或者其補碼,由基準(zhǔn)h(n)當(dāng)前的值決定。實際上,電路的功能等價于將u(n)和在1和-1間交替變化的數(shù)列相乘,也就是說,v(n)是u(n)以h(n)為基準(zhǔn)相敏整流的結(jié)果。

基準(zhǔn)發(fā)生器Nrm為相敏整流器提供基準(zhǔn)h(n)。對50 MHz時鐘進(jìn)行分頻,產(chǎn)生與二次諧波磁通門信號同頻率,即6.103 MHz的方波,通過控制信號Ctlr調(diào)整相位,使基準(zhǔn)的相位和二次諧波磁通門信號的相位對其相敏整流的效率最大化。

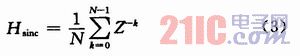

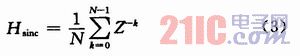

低通濾波器Sinc_Fltr是N點sine濾波器的FIR形式,傳輸函數(shù)是:

信號流圖如圖3所示。

由于二次諧波磁通門信號一個周期采樣128點,因此N=128;按照圖3所示的信號流圖,128點sinc濾波器由127個加法器和128個寄存器組成。為防止溢出,加法器和寄存器寬度為16+log2 8=24位,最后一級輸出的高16位作為濾波器的輸出。實現(xiàn)了低通濾波的功能。

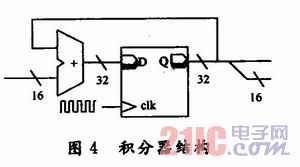

積分放大由積分器Intgtr實現(xiàn),結(jié)構(gòu)如圖4所示。為防止溢出,采用32位的加法器和寄存器。加法器的一個輸入端是低通濾波器的輸出,另一個是累加和。在閉環(huán)系統(tǒng)中,積分器輸出的低16位是反映被測磁場大小的數(shù)字量。

5 實驗和結(jié)果

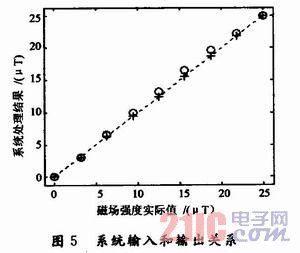

使用雙鐵芯結(jié)構(gòu)磁通門探頭感應(yīng)被測磁場,磁場強度從0μT變化到25μT。首先去掉積分模塊打開反饋回路,對開環(huán)結(jié)構(gòu)的前向通道進(jìn)行測試,然后加入積分模塊和閉合反饋回路,對閉環(huán)系統(tǒng)進(jìn)行測試。兩次實驗的輸入/輸出關(guān)系如圖5所示,圖中“o”是開環(huán)結(jié)構(gòu)的結(jié)果,“+”是閉環(huán)結(jié)構(gòu)的結(jié)果。

兩次試驗的數(shù)據(jù)如表1所示。

當(dāng)系統(tǒng)開環(huán)時,隨著被測磁場的增大,系統(tǒng)輸出單調(diào)增高,可以反映被測磁場的大小。輸出的非線性度為4.01%,最大誤差為0.867μT,受磁通門探頭鐵芯的非線性影響很大。閉環(huán)后,系統(tǒng)非線性度和誤差性能得到明顯改善,非線性度為0.012%,最大誤差為3nT。

6 結(jié)語

本文中描述的基于FPGA的磁通門傳感器系統(tǒng)采用閉環(huán)結(jié)構(gòu),提高了系統(tǒng)輸出梯度線性度。FPGA內(nèi)的數(shù)字邏輯實現(xiàn)了包括磁通門信號解算在內(nèi)的多種功能。實驗驗證了系統(tǒng)功能的正確性。由于數(shù)字邏輯的特點,和模擬系統(tǒng)相比,基于FPGA的設(shè)計有著優(yōu)秀的溫度穩(wěn)定性,可移植性,且易于小型化。本文中的設(shè)計可直接應(yīng)用在最終產(chǎn)品中,也可以作為專用集成電路的行為驗證,以此為基礎(chǔ)繼續(xù)開發(fā)集成電路芯片。