中心議題:

- EMC四大設計技巧

解決方案:

相關性閱讀

【CLASS 1】EMC元器件的選擇和應用技巧

http://www.cntronics.com/public/art/artinfo/id/80011142?source=lecture

電磁干擾的主要方式是傳導干擾、輻射干擾、共阻抗耦合和感應耦合,。對這幾種途徑產(chǎn)生的干擾我們應采用的相應對策:傳導采取濾波,,輻射干擾采用屏蔽和接地等措施,就能夠大大提高產(chǎn)品的抵抗電磁干擾的能力,,也可以有效的降低對外界的電磁干擾,。本文從濾波設計、接地設計,、屏蔽設計和PCB布局布線技巧四個角度,,介紹EMC的設計技巧。

一,、EMC濾波設計技巧

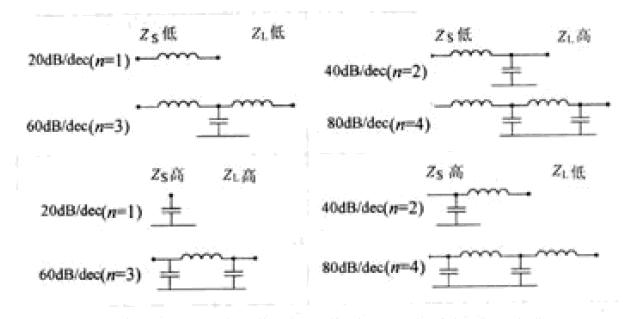

EMC設計中的濾波器通常指由L,,C構(gòu)成的低通濾波器。濾波器結(jié)構(gòu)的選擇是由"最大不匹配原則"決定的,。即在任何濾波器中,,電容兩端存在高阻抗,電感兩端存在低阻抗,。圖1是利用最大不匹配原則得到的濾波器的結(jié)構(gòu)與ZS和ZL的配合關系,,每種情形給出了2種結(jié)構(gòu)及相應的衰減斜率(n表示濾波器中電容元件和電感元件的總數(shù))。

圖1 濾波器的結(jié)構(gòu)與ZS和ZL的配合關系

去耦電容的自諧振頻率

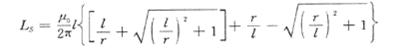

電容的寄生電感Ls的大小基本上取決于引線的長度,,對圓形,、導線類型的引線上的典型值為10nH/cm。典型的陶瓷電容的引線約有6 mm長,,會引入約15nH的電感,。引線電感也可由下式估算:

其中:l和r分別為引線的長度和半徑。寄生電感會與電容產(chǎn)生串聯(lián)諧振,,即自諧振,,在自諧振頻率fo處,,去耦電容呈現(xiàn)的阻抗最小,,去耦效果最好。但對頻率f高于f/o的噪聲成份,,去耦電容呈電感性,,阻抗隨頻率的升高而變大,使去耦或旁路作用大大下降,。實踐中,,應根據(jù)噪聲的最高頻率fmax來選擇去耦電容的自諧振頻率f0,最佳取值為fo=fmax,。

去耦電容容量的選擇

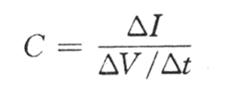

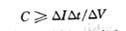

在數(shù)字系統(tǒng)中,,去耦電容的容量通常按下式估算:

其中:△I為瞬變電流;△V為邏輯器件允許的電源電壓變化,,△t為開關時間,。

實踐中,,去耦電容的容量可按C=1/f選用,f為電路頻率,,去耦電容的容量選擇還必須滿足以下條件:

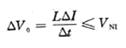

(1)芯片于去耦電容兩端電壓差△V,。必須小于噪聲容限Vni:

- 旭瑞光電贏得EMC聯(lián)盟5億元LED芯片意向合同

- EMC電磁兼容常見的問題以及解決方案

- MILMEGA針對EMC測試推出三款新品延伸

- EMC兼容的汽車開關穩(wěn)壓器設計

- 數(shù)字電路PCB的EMI控制技術(shù)

- 什么是EMC認證

- EMC是什么意思?

- EMC是什么,?

- 小電流接地系統(tǒng)

- 接地系統(tǒng)的特點

(2)從去耦電容為芯片提供所需的電流的角度考慮,,其容量應滿足:

(3)芯片開關電流Ic的放電速度必須小于去耦 電流的最大放電速度:

此外,當電源引線比較長時,,瞬變電流會引起較大的壓降,,此時就要加容納電容以維持器件要求的電壓值。

二,、EMC接地設計

接地是最有效的抑制騷擾源的方法,,可解決50%的EMC問題。系統(tǒng)基準地與大地相連,,可抑制電磁騷擾,。外殼金屬件直接接大地,還可以提供靜電電荷的泄漏通路,,防止靜電積累,。

在地線設計中應注意以下幾點:

(1)正確選擇單點接地與多點接地

在低頻電路中,信號的工作頻率小于1MHz,,它的布線和器件間的電感影響較小,,而接地電路形成的環(huán)流對干擾影響較大,因而應采用單點接地,。當信號工作頻率大于10MHz時,,地線阻抗變得很大,此時應盡量降低地線阻抗,,應采用就近多點接地,。當工作頻率在1~10MHz時,如果采用一點接地,,其地線長度不應超過波長的1/20,,否則應采用多點接地法。

(2)將數(shù)字電路與模擬電路分開

電路板上既有高速邏輯電路,,又有線性電路,,應使它們盡量分開,而兩者的地線不要相混,,分別與電源端地線相連,。要盡量加大線性電路的接地面積。

(3)盡量加粗接地線

若接地線很細,接地電位則隨電流的變化而變化,,致使電子設備的定時信號電平不穩(wěn),,抗噪聲性能變壞。因此應將接地線盡量加粗,,使它能通過三位于印制電路板的允許電流,。如有可能,接地線的寬度應大于3mm,。

(4)將接地線構(gòu)成閉環(huán)路

設計只由數(shù)字電路組成的印制電路板的地線系統(tǒng)時,,將接地線做成閉環(huán)路可以明顯的提高抗噪聲能力。其原因在于:印制電路板上有很多集成電路組件,,尤其遇有耗電多的組件時,,因受接地線粗細的限制,會在地結(jié)上產(chǎn)生較大的電位差,,引起抗噪聲能力下降,,若將接地結(jié)構(gòu)成環(huán)路,則會縮小電位差值,,提高電子設備的抗噪聲能力,。

三、EMC屏蔽設計

屏蔽就是以金屬隔離的原理來控制某一區(qū)域的電場或磁場對另一區(qū)域的干擾,。它包括兩個含義:一是將電路,、電纜或整個系統(tǒng)的干擾源包圍起來,防止電磁干擾向外擴散,;二是用屏蔽體將接收電路,、設備或系統(tǒng)包圍起來,防止它們受到外界電磁干擾的影響,。屏蔽按照機理可以分為電場屏蔽,、磁場屏蔽、電磁場屏蔽三種不同方式,。

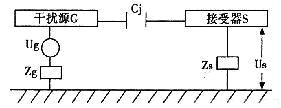

電場屏蔽

電子設備中的電場通常是交變電場,,因此可以將兩個系統(tǒng)間的電場感應認為是兩個系統(tǒng)之間分布電容Cj的耦合,如圖2所示,。

圖2 電場耦合示意圖

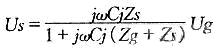

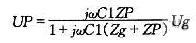

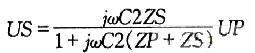

其中,,Ug為干擾源交變電壓,,Us為接受器的感應電壓,,Cj為G、S間的分布電容,,Zs為接受器的接地電阻,。則可得

由此可知,干擾電壓Us的大小與耦合電容Cj的大小有關:Cj越大,則Us越大,。因此,,為了減小干擾電壓Us,應設法減小耦合電容Cj,,設法將干擾源G和接受器S盡可能的遠離,。如果條件所限不能遠離,則應在二者之間采取屏蔽措施,。

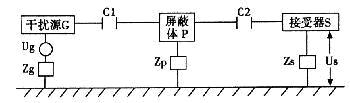

圖3 加入屏蔽體后的電場耦合示意圖

如圖3,,在干擾源G和接受器S之間加入屏蔽體P,若屏蔽體P的接地電阻為ZP,,則可得屏蔽體的感應電壓為

則接受器上的感應電壓為

由此可知,,要使接受器的感應電壓Us減小,Zp應盡可能的小,。所以,,屏蔽體必須選擇導電性能良好的材料,而且須有良好的接地,。否則,,因為Cl>Cj,C2>Cj,,若屏蔽體的接地電阻較大,,將使屏蔽體加入后造成的干擾反而變得更大。

磁場屏蔽

磁場屏蔽是指對低頻磁場和高頻磁場的屏蔽,。

低頻磁場的屏蔽采用高導磁率的鐵磁性材料,。利用鐵磁性材料的高導磁率對干擾磁場進行分路,使通過空氣的磁通大為減少,,從而降低對被干擾源的影響,,起到磁場屏蔽的作用。由于是磁分路,,所以屏蔽材料屏蔽材料 的磁導率U越高,,屏蔽罩屏蔽罩越厚,磁分路流過的磁通越多,,屏蔽效果越好,。

高頻磁場的屏蔽采用低電阻率的良導體作為屏蔽材料屏蔽材料。外界高頻磁場在屏蔽體中產(chǎn)生渦流,,渦流形成的磁場抑制和抵消外界磁場,,從而起到了屏蔽的作用。與低頻磁屏蔽不同,,由于高頻渦流的趨膚效應,,屏蔽體的尺寸并不是屏蔽效果的關鍵所在,,而且屏蔽體接地與否和屏蔽效果也沒有關系。但對于高頻磁屏蔽的金屬良導體而言,,若有良好的接地,,則同時具備了電場屏蔽和磁場屏蔽的效果。所以,,通常高頻磁屏蔽的屏蔽體也應接地,。

電磁場屏蔽

電磁場屏蔽是利用屏蔽體對電場和磁場同時加以屏蔽,一般用來對高頻電磁場進行屏蔽,。由前述可知,,對于頻率較高的干擾電壓,選擇良導體制作屏蔽體,,且有良好的接地,,則可起到對電場和磁場同時進行屏蔽的效果。但是必須注意,,對高頻磁場屏蔽的渦流不僅對外來干擾產(chǎn)生抵制作用,,同時還可能對被屏蔽體保護的設備內(nèi)部帶來不利的影響,從而產(chǎn)生新的干擾,。

四、PCB設計之布局布線策略

1.選擇合理的導線寬度

由于瞬變電流在印制線條上所產(chǎn)生的沖擊干擾主要是由印制導線的電感成分造成的,,因此應盡量減小印制導線的電感量。印制導線的電感量與其長度成正比,,與其寬度成反比,因而短而精的導線對抑制干擾是有利的,。時鐘引線、行驅(qū)動器或總線驅(qū)動器的信號線常常載有大的瞬變電流,,印制導線要盡可能地短。對于分立組件電路,,印制導線寬度在1.5mm左右時,即可完全滿足要求,;對于集成電路,,印制導線寬度可在0.2~1.0mm之間選擇,。

2.采用正確的布線策略

布線時需要注意的幾個方面:

(1)保持環(huán)路面積最小,,降低干擾對系統(tǒng)的影響,提高系統(tǒng)的抗干擾性能,。并聯(lián)的導線緊緊放在一起,使用一條粗導線進行連接,,信號線緊挨地平面布線可以降低干擾。電源與地之間增加高頻濾波電容,。

(2)使導線長度盡可能的縮短,,減小印制板的面積,降低導線上的干擾,。

(3)采用完整的地平面設計,采用多層板設計,,鋪設地層,便于干擾信號泄放,。

(4)使電子元件遠離可能會發(fā)生放電的平面如機箱面板,、把手,、螺釘?shù)?,保持機殼與地良好接觸,,為干擾提供良好的泄放通道。對敏感信號包地處理,,降低干擾。

(5)盡量采用貼片元器件,。

(6)模擬地與數(shù)字地在PCB與外界連接處進行一點接地。

(7)高速邏輯電路應靠近連接器邊緣,,低速邏輯電路和存儲器則應布置在遠離連接器處,中速邏輯電路則布置在高速邏輯電路和低速邏輯電路之間,。

(8)電路板上的印制線寬度不要突變,拐角應采用圓弧形,,不要直角或尖角。

(9)時鐘線,、信號線也盡可能靠近地線,,并且走線不要過長,,以減小回路的環(huán)面積,。

3.印制電路板的尺寸與器件的布置

印制電路板大小要適中,,過大時印制線條長,,阻抗增加,,不僅抗噪聲能力下降,成本也高,;過小,則散熱不好,,同時易受臨近線條干擾。

在器件布置方面與其它邏輯電路一樣,,應把相互有關的器件盡量放得靠近些,,這樣可以獲得較好的抗噪聲效果。時鐘發(fā)生器,、晶振和CPU的時鐘輸入端都易產(chǎn)生噪聲,,要相互靠近些,。易產(chǎn)生噪聲的器件,、小電流電路、大電流電路等應盡量遠離邏輯電路,,如有可能,應另做電路板,。