SDH技術(shù)是最重要的寬帶傳輸技術(shù),其在IP網(wǎng)絡中應用也十分廣泛,是最重要的骨干網(wǎng)傳輸鏈路類型,因此開發(fā)POS(Packet over SDH,SDH網(wǎng)上傳IP)線卡成為核心路由器等高端IP網(wǎng)絡設(shè)備開發(fā)中的重點。

在實際使用中,SDH信號有2種:一種是整體信號(concatenated mode,在其速率等級標識中以“c”結(jié)尾),這種信號直接采用高階虛容器進行數(shù)據(jù)映射,如STM-16c信號類型的含義就是其內(nèi)部幀結(jié)構(gòu)是按照2.5Gb/s的速率虛容器進行字節(jié)間插,而不是由多個低階容器映射而得,因此無法將其明確的分為多個155M或者622M信號;另一種是通道化信號(channelized mode,在其速率等級結(jié)尾處沒有“c”),這種信號是由低階虛容器逐級映射而得到,因此對STM-16信號,它可通過區(qū)分幀結(jié)構(gòu)內(nèi)部的字節(jié)陣列來得到多個155M信號或者622M信號。

對應于上述2種SDH信號,在POS傳輸中有2類線卡,一類用于處理整體SDH信號,一類用于處理通道化POS信號,這里重點討論后者。通道化POS線卡在目前主要網(wǎng)絡設(shè)備供應商的產(chǎn)品目錄里較少提及,但是其應用領(lǐng)域卻越來越廣。隨著寬帶接入需求的不斷發(fā)展,許多企事業(yè)單位都需要租用獨享的鏈路,通道化的POS不僅能夠滿足這一要求,而且由于其對信號的匯聚能力強,因此還有節(jié)省布線資源及維護升級和線路備份成本低等優(yōu)點。因此,通道化線卡的應用前景非常好,而且已經(jīng)在許多特種行業(yè)中得到廣泛的應用。

本文首先對通道化0C48(2.5G)的設(shè)計需求進行分析,據(jù)此提出了基于PM5360和FPGA的整體設(shè)計方案,鑒于鏈路層處理器件PM5360在設(shè)計中的獨到之處以及使用中的難點,論文重點分析了其使用要點和難點,并給出了能夠靈活支持多種模式的芯片配置方法和軟件設(shè)計。

1 設(shè)計需求分析

0C48通道化線卡的設(shè)計除需要滿足通道化POS信號的處理需求外,還需要根據(jù)其可能的應用領(lǐng)域進一步確定,主要包括:1)能夠?qū)νǖ阑疧C48信號進行最小粒度為0C3的處理,需要支持單一OC3、單一OCl2以及混合方式,通道化0C48模式下的每個0C12能夠進一步通道化為更細粒度的4個0C3;2)兼容非通道化的0C3c、OCl2c、OC48c信號處理;3)支持上述工作模式的動態(tài)配置;4)支持IP包的線速處理。

2 整體方案

根據(jù)現(xiàn)代路由器等IP報文路由轉(zhuǎn)發(fā)設(shè)備的結(jié)構(gòu)和功能需求,圖l給出了通道化0C48接口的整體設(shè)計方案。

由于需要滿足支持OC-3、OC-12和OC-48 3種不同速率的POS接口,因此選用Sumitomo Eleetric公司的SCP6802-GL和SCP6808-GL 2種型號的光器件,完成光電轉(zhuǎn)換功能。其中SCP6802-GL支持155 M/622M 2種POS接入速率,SCP6808-GL支持2.5G POS接入速率,2種器件的封裝兼容,且支持熱插拔,可以根據(jù)接口需求方便的轉(zhuǎn)換。

鏈路層處理是線卡要完成的關(guān)鍵功能,根據(jù)需求分析,這里選用PMC公司的PM5360為主處理器,該器件采用“成幀器與物理接口一體化”設(shè)計思路,將鏈路層處理和物理層處理功能集成在單一芯片內(nèi)部。

該器件支持l路OC48,或支持總速率不超過OC48的4路OC3與0C12的任意組合,并支持接口工作模式的動態(tài)改變;根據(jù)Internet工程任務組(IETF)PPP工作組的RFC 2615(1619)/1662,執(zhí)行基于SONET/SDH規(guī)范的點對點協(xié)議(PPP):為POS或ATM應用提供SATURN POS-PHY第3層32位系統(tǒng)接口(時鐘頻率高達104MHz),即標準的SPl3接口;支持每個傳輸串行流的獨立環(huán)路時鐘工作方式;支持從每條線路端接收流至相應傳輸流的獨立線路環(huán)回,以及支持從線路端傳輸流至相應線路端接收流接口的獨立診斷環(huán)回;提供通用16位微處理器總線接口,用于配置、控制和狀態(tài)監(jiān)控;低功耗1.8V CMOS核心邏輯,具有3.3V CMOS/TTL兼容性數(shù)字輸入和輸出功能,PECL輸入與輸出符合3.3V標準。

報文處理模塊采用FPGA完成,根據(jù)對資源需求的估算,選擇Xilinx公司的Virtex-II XC2VP70實現(xiàn)。在FPGA內(nèi)部完成對于PPP幀的處理,此外,板級處理機還利用FPGA完成對各關(guān)鍵器件的初始化及相關(guān)配置。

PM5360通過一組SPI-3接口經(jīng)接口適配模塊進入FPGA內(nèi)部。根據(jù)系統(tǒng)管理需求,線卡通過MPC860完成控制管理功能,基于VxWorks操作系統(tǒng)設(shè)計板級軟件,完成初始化、各模塊配置、運行狀態(tài)監(jiān)測、統(tǒng)計信息上報等功能。

3 PM5360應用要點與難點

由于PM5360集成的功能豐富,其內(nèi)部電路復雜,可配置寄存器數(shù)量超過2000個,因此其應用難度較大。根據(jù)筆者的調(diào)試經(jīng)驗,下面對該器件在通道化應用下的難點進行解釋,主要包括間接寄存器讀寫方法及調(diào)度機的設(shè)計等。

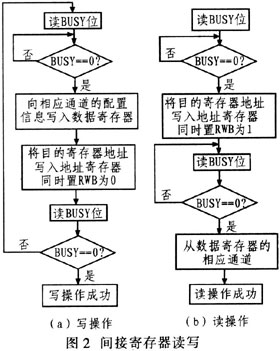

在PM5350的寄存器里,除了能夠直接按照訪存方式讀寫的寄存器外,還有大量間接寄存器,此類寄存器對POS模式下的器件工作方式尤為重要,但其配置方式特殊,因此本文對其使用要點進行總結(jié),如圖2所示。

在PM5360內(nèi)部有一個內(nèi)置調(diào)度機,負責按照配置好的調(diào)度順序讀取各個通道的數(shù)據(jù)并放人接口緩存中,由于該芯片采用物理標識(PHID)和內(nèi)部通道號同時存在的設(shè)計思路,而且通道化應用下單個物理通道內(nèi)具有多個數(shù)據(jù)流,因此調(diào)度機的設(shè)計更復雜。

表1總結(jié)了調(diào)度機的設(shè)計要點,具體應用中,根據(jù)需要的模式將該表中的相應數(shù)值和對應的物理標識通過間接寄存器接口寫入地址為0x0335的寄存器。

另外,在應用中需要注意的是,PM5360在每個通道內(nèi)都置有2組并行的模塊:xCFP和xTDP。其中xCFP包括RCFP(接收方向信元和幀處理器) 和TCFP(發(fā)送方向信元和幀處理器),xCFP用于0C12和OC48模式下的數(shù)據(jù)處理。xTDP包括RTDP(接收方向時間片數(shù)據(jù)通信處理器)和TTDP(發(fā)送方向時間片數(shù)據(jù)通信處理器),用于OC3模式下的數(shù)據(jù)處理。在這兩個模塊的配置中,除了保證所有寄存器都按要求置位外,還需注意根據(jù)線路的實際特點完成各個通道以及內(nèi)部子通道的加擾與解擾方式、使CRC校驗算式等與實際線路一致,這一點在實際中常被忽略而成為偽故障,從而導致開發(fā)周期延長。

值得指出的是,由于PM5360內(nèi)部結(jié)構(gòu)復雜,模塊眾多,同時數(shù)據(jù)處理路徑上的許多單元具有很強的關(guān)聯(lián)性,因此廠家建議了一個較為嚴格的復位與配置順序,基本原則可以總結(jié)為“按照數(shù)據(jù)流向,先完成邏輯單元配置,再完成物理單元配置,最后使能功能模塊”,在實際中應照此原則執(zhí)行。

4 支持動態(tài)模式的PM5360配置軟件設(shè)計

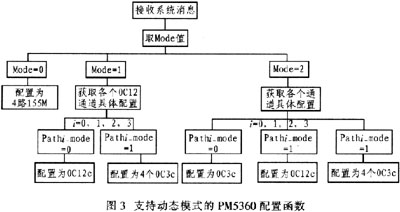

本設(shè)計中的線卡支持多種工作模式,因此要求PM5360能夠根據(jù)需要動態(tài)改變其內(nèi)部寄存器配置,本部分給出其配置函數(shù)的設(shè)計要點。圖3是支持動態(tài)模式的PM5360配置函數(shù)。

該函數(shù)的基本形式為:PM5350_Config(unsigned charmode,unsigned char pathO_mode,unsigned char pathl_mode,unsigned char path2_mode,unsigned ehar path3_mode)。該函數(shù)的5個參數(shù)均為unsigned char類型,其中第1個參數(shù)mode用于指示器件處于通道化工作狀態(tài)還是非通道化狀態(tài),其余4個函數(shù)分別代表其4個通道的工作狀態(tài)。

根據(jù)路由器的體系結(jié)構(gòu)特點,線卡等功能部件通過內(nèi)部通信系統(tǒng)與主控聯(lián)系,獲取配置信息,并實時上報自身的運行狀態(tài)信息和相關(guān)統(tǒng)計信息。因此,在圖3中,函數(shù)PM5350_Config()中的參數(shù)是由主控下發(fā)的,函數(shù)接收到參數(shù)后按照該流程進行解釋,從而完成配置。

5 性能測試

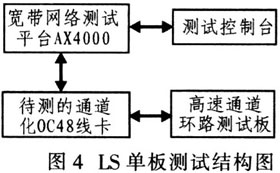

為了測試通道化單板的功能和性能,設(shè)計如圖4所示的測試方案。其基本原理是:按照該線卡在實際網(wǎng)絡中的應用特征,由測試控制臺發(fā)出命令控制網(wǎng)絡測試平臺AX4000按照所需模式發(fā)送數(shù)據(jù)至待測線卡,線卡接收數(shù)據(jù)后按照其內(nèi)部處理機制完成報文處理,并最終經(jīng)輸出接口將數(shù)據(jù)送至測試儀,測試儀根據(jù)收到的報文情況給出丟包率等性能指標的測試結(jié)果。

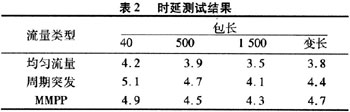

測試的主要內(nèi)容是通道化混合信道類型支持能力,具體指標包括丟包率、時延和時延抖動等。測試結(jié)果表明,所設(shè)計的線卡能夠支持需求分析所提出的全部功能指標,并且在100%鏈路利用率下,能夠線速處理全部報文,丟包率為0,且各種性能指標符合設(shè)計要求。表2給出了時延測試結(jié)果,表明實際的時延指標滿足設(shè)計要求。

6 結(jié)束語

本文基于PM5360和FPGA設(shè)計通道化OC48線卡,討論設(shè)計需求,給出總體設(shè)計方案,重點分析PM5360的使用要點和難點,并給出能夠動態(tài)變換工作模式的芯片配置方法。測試結(jié)果表明本文的設(shè)計能夠滿足實際需求。