該設計以ADI公司的Blackfin系列中的BF561作為處理器,分別采用ADV7181B和ADV7171作為視頻編解碼芯片,設計了圖像平移系統(tǒng)。通過采用基于描述子的DMA及MDMA圖像傳輸方式等方法,解決了圖像平移時的實時性難題。該圖像平移系統(tǒng)設計結構緊湊,成本低廉,可靠性高,可以廣泛應用于電子穩(wěn)像技術中。

1 系統(tǒng)設計

ADSP—BF561處理器是ADI公司推出的Blaekfin系列中的高性能產品,它采用獨立的雙核結構,主頻600 MHz,具有2套乘法器和算術邏輯單元,豐富的DMA通道,內嵌328 KB超高速L1 SRAM和高速的L2 SRAM。同時,ADSP-BF561具有2個PPI接口,可以方便地與視頻解碼器和視頻編碼其相連,無需外圍邏輯支持。ADSP-BF561把存儲器視為一個統(tǒng)一的4 GB的地址空間,使用32位地址。所有資源,包括內部存儲器、外部存儲器和I/O控制寄存器,都占用公共地址空間的相應部分,并且各自對立。該地址空間的各部分存儲器按分級結構排列,提供高性價比。其中極快速、低延遲的存儲器接近處理器放置、而更大的、低成本、低性能的存儲器則原理處理器放置。片外存儲系統(tǒng)通過外部總線接口單元EBIU(External Bus Interface Unit)進行訪問。存儲器的DMA控制器提供高帶寬的數據傳輸能力,能在內部L1/L2存儲器和外部存儲器空間之間傳輸代碼和數據塊。該設計以ADI公司的ADSP—BF561為核心,Visual DSP++5.0為軟件開發(fā)環(huán)境,對圖像平移系統(tǒng)進行開發(fā)。

2 硬件設計方案及實現(xiàn)

2.1 硬件設計方案

圖像平移就是將圖像中的所有像素點都按照指定的平移量沿水平或者垂直方向移動。假設圖像f(x,y)以平移量(α,β)分別在x軸方向和y軸方向上進行平移,則平移之后的圖像就變成了f(x-α,y-β)。平移算法是幾何變換中最簡單的變換之一,但是這種簡單的變換卻在電子穩(wěn)像中發(fā)揮著很大的作用。

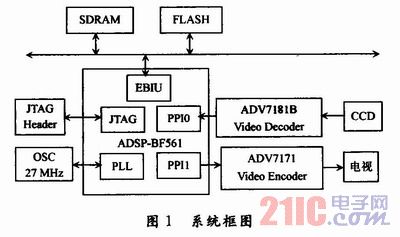

平移算法的難點主要體現(xiàn)在算法的實時性上。假設一個視頻采集系統(tǒng)圖像的采集速率為25幀/s,要想實時地看到平移后的圖像,那么平移算法必須要在40 ms內完成,而對于大小為720×576×2 B=829.4 KB的圖像要完成數據的搬移工作,如果設計不好,很可能會產生遲滯現(xiàn)象。為此本文將平移算法的平臺設計在ADI公司的高性能芯片BF561上,并使用DMA及MDMA等方式實現(xiàn)算法的平移,該系統(tǒng)框圖如圖1所示。

該系統(tǒng)設計方案中主要包含以下主要硬件:

(1)CPU:600 MHz的Blaekfin 561雙核處理器。

(2)FLASH:1片SAMSUNG K4S5616320 8 MB。

(3)視頻接口:BF561.提供了2個16位的ParallelPeripheral Interface(PPI0和PPI1),它們可分別與視頻解碼芯片ADV7181B、視頻編碼芯片ADV7171連接。

(4)外部總線接口(EBIU):為ADSP—BF561與外部存儲器和通過總線尋址的外部設備提供了連接通道。通過EBIU連接2片SDRAM。

(5)SDRAM:2片SAMSIING K4S561632064 MB;該系統(tǒng)對PAL制式的視頻數據進行采集,經ADV718lB解碼后轉換為ITU-656格式的視頻信號YCrCb采用4:2:2的輸入格式,視頻數據所需的存儲空間較大,故需要擴展外部存儲器SDRAM。

(6)JTAG調試接口,通過仿真器與PC機相連,實現(xiàn)JTAG硬件調試功能。

CCD攝像頭每40 ms采集一幀模擬視頻信號,ADV7181B解碼后轉換為ITU-656格式的視頻信號,通過PPI0利用DMA方式自動將其放入外部SD-RAM中。為在電視上實時看到平移后的圖像,DSP內核必須要在40 ms內讀取SDRAM中的視頻數據,按照平移算法的要求實現(xiàn)對圖像的上、下、左、右平移后,寫回SDRAM,并由DSP內核讀取該SDRAM中的數據,啟動PPI1通過DMA送給ADV7171編碼成模擬的PAL制(圖像的輸出格式為ITU-656格式),最后由電視屏幕顯示輸出。

2.2 關鍵技術問題的解決途徑

在平移算法中由于每40 ms采集1幀數據,為了保證能夠使人眼實時的看到平移后的視頻流,必須要保證能夠實時的完成數據搬移工作。為此本設計中采用如下關鍵技術來解決。

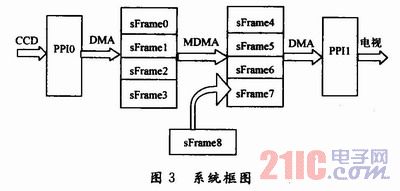

(1)由于圖像輸入后,要經過平移算法對圖像進行上、下、左、右平移后,圖像才能輸出到電視上。因此該系統(tǒng)將圖像的輸入存儲區(qū)域和圖像的輸出存儲區(qū)域分別設為2塊獨立的區(qū)域,使得在數據輸入的同時還可進行數據的搬移及輸出顯示工作。每個輸入/輸出區(qū)域又可以分為4個區(qū)域,用來存儲順次進入的輸入/輸出圖像。其中sFrame0~sFrame3用來存儲輸入的視頻圖像,sFrame4~sFrame7用來存儲搬移后的視頻圖像。當啟動ADV7181B采集完1幀圖像存入后sFrame0,BF561啟動數據搬移工作,將視頻圖像搬移到sFrame4中,并通過PPI1送給視頻編碼器ADV7171,最后由電視屏幕顯示輸出,同時PPI0將數據繼續(xù)采集到sFramel。圖像存儲在SDRAM中,sFrame0~sFrame7各存儲區(qū)域的首地址分別為0x0000C400,0x1000000,0x1500000,0x01A00000,0x01F00000,0x02400000,0x02900000,0x03000000。

(2)為了提高系統(tǒng)的實時處理能力,將數據在不同存儲空間的轉移任務交給DMA來完成,從而使CPU只專注于數據的計算。為保證連續(xù)采集不斷幀,DMA采用描述子方式,并將最后一個描述子指向首塊的頭地址。CCD采集到的視頻圖像首先送到PPI0,經過2維DMA方式依次送到由描述子描述的圖像輸入存儲區(qū)域。

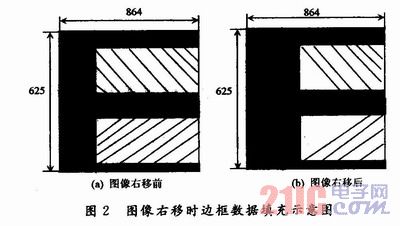

(3)由于圖像的平移,輸出后的圖像會有一些邊框,為提高系統(tǒng)的實時性,將邊框數據預先存放在SDRAM中,然后再采用MDMA方式將邊框數據傳送到相應的視頻輸出區(qū)域中。存放邊框數據的SDRAM定義為sFrame8,其首地址為0x03600000。其中sFrame8的大小為1440*288,即為ITU-656格式中一場數據的大小。本算法中上、下、左、右平移后的邊界填充為黑色,按UYVY格式即應該填充為0x80,0x10,0x80,0x10。邊框數據的MDMA方式傳輸在有效數據傳輸之前進行,每次MDMA傳輸也是只傳遞1場數據,1幀數據同樣需要2次MDMA傳輸完成。邊框數據的填充見圖2。圖2(b)為圖像右移后左邊填充為黑色邊框數據的示意圖。

(4)從輸入區(qū)域到輸出區(qū)域只搬移有效的數據(Active Field),ITU-656格式的文件頭在輸出區(qū)域初始化時已設置完成。且有效的數據傳輸方式采用MDMA方式,每次傳輸1幀圖像數據中的1場圖像,搬完奇場數據后再搬偶場數據。

(5)平移后的圖像存儲在圖像輸出存儲區(qū)域(sFrame4~sFrame7)中,平移后的圖像由PPI1通過按描述子的指示輸出到電視上顯示出來。整個系統(tǒng)的工作框圖如圖3所示。

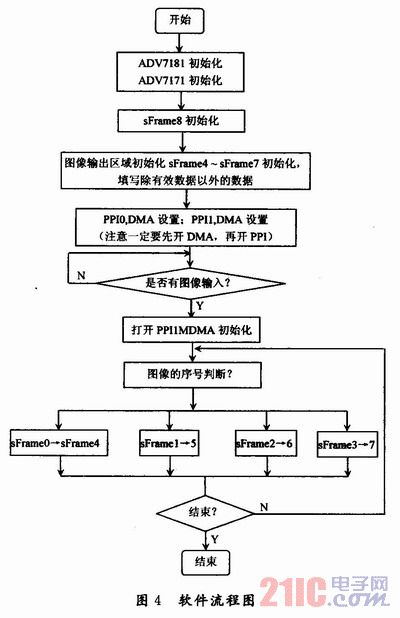

軟件設計流程圖如圖4所示。

3 平移方案的實現(xiàn)

該系統(tǒng)通過JIAG仿真,使用Visual DSP++5.0作為開發(fā)環(huán)境,進行了圖像平移實驗及性能分析。使用該算法后平移的效果如圖5所示。

在該算法中,完成1場數據的MDMA數據大約需要4 ms,而完成整個1幀圖像的傳輸平均需要21 ms,因此在40 ms的周期內可以實對圖像的實時平移。

4 結語

在結合圖像平移算法以及BF561結構和特點的基礎上,作者創(chuàng)新性的實現(xiàn)了一種基于ADSP—BF561雙核處理器的圖像平移系統(tǒng)的設計。由于充分利用了BF561的描述子存儲方式,以及其DMA和MDMA數據傳輸方式,結構設計簡單,實時性好。仿真結果證明了算法的有效性。