摘要:使用Verilog HDL硬件描述語言完成了對CAN總線控制器的設(shè)計(jì),能夠?qū)崿F(xiàn)符合CAN2.0A協(xié)議的所有功能。本總線控制器的外部接口采用Altera公司開發(fā)的Avalon總線接口,增強(qiáng)了控制器的應(yīng)用靈活性。本設(shè)計(jì)使用Modelsim軟件完成了功能仿真和時序仿真。

關(guān)鍵詞:CAN總線;控制器;現(xiàn)場可編程門陣列

0 引言

CAN(控制器局域網(wǎng))是一種先進(jìn)的串行通信協(xié)議,由德國BOSCH公司開發(fā),并最終成為國際標(biāo)準(zhǔn)(ISO11898),是國際上使用最廣泛的現(xiàn)場總線之一。目前世界上已有20多家CAN總線控制器生產(chǎn)商,110多種CAN總線控制器芯片和集成CAN總線控制器的微處理器芯片。

由于定制的CAN總線控制器芯片不能嵌入到SoC(片上系統(tǒng))中,而采用分立元器件實(shí)現(xiàn)CAN總線接口,使得系統(tǒng)中器件數(shù)量增加,同時也增大了系統(tǒng)面積,本文所介紹的CAN總線控制器正是由Verilog HDL語言描述,既可以作為一個獨(dú)立的設(shè)備,也可以作為一個模塊集成到FPGA中。

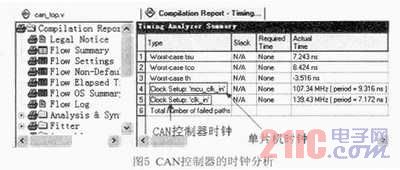

雖然目前國內(nèi)外已有很多人研究或設(shè)計(jì)了CAN總線控制器IP核,但其中大多數(shù)只是對控制器中的某一個模塊進(jìn)行了研究和設(shè)計(jì),并沒有實(shí)現(xiàn)一個完整的CAN總線控制器的功能,例如文獻(xiàn)只對CAN控制器的狀態(tài)機(jī)進(jìn)行研究,文獻(xiàn)只對CAN控制器的位定時模塊進(jìn)行研究。而完整實(shí)現(xiàn)了CAN總線控制器功能的作品中,最高工作頻率又不是很理想,例如Mentor Graphics公司提供的MCAN2D1 CAN2.0 Network Controller的最高工作頻率只有32.46MHz,文獻(xiàn)中介紹的CAN總線控制器的最高工作頻率也只有50MHz,這些IP核顯然不能適應(yīng)高速環(huán)境的要求,同時文獻(xiàn)中介紹的控制器對外接口中出現(xiàn)了寄存器使能位等接口,這種接口不符合Avalon總線規(guī)范,不利于集成到FPGA芯片中,其通用性肯定較差,所以研究并設(shè)計(jì)出一款高速且通用性強(qiáng)的CAN總線控制器的IP核仍然是有其重要意義的。

1 系統(tǒng)實(shí)現(xiàn)

1.1 系統(tǒng)框圖

本設(shè)計(jì)中將整個CAN控制器系統(tǒng)分為了11個模塊,分別是Avalon總線接口模塊、寄存器組模塊、接收緩沖器模塊、發(fā)送緩沖器模塊、接收濾波模塊、CRC校驗(yàn)?zāi)K、狀態(tài)機(jī)模塊、標(biāo)識符填充模塊、錯誤計(jì)數(shù)器模塊、位填充模塊、位定時模塊。其結(jié)構(gòu)框圖如圖1所示。

1.2 主要模塊介紹

1.2.1 寄存器組模塊

本模塊由位寬為8bit,深度為256的寄存器組實(shí)現(xiàn)其功能,其中已經(jīng)使用的寄存器為23個,其余的供以后擴(kuò)展。本設(shè)計(jì)采用將各個獨(dú)立的控制及狀態(tài)寄存器集成在一起的設(shè)計(jì)思想,任何對控制器的初始化以及數(shù)據(jù)的接收和發(fā)送都是從寫寄存器組開始的。

1.2.2 CRC校驗(yàn)?zāi)K

CRC(循環(huán)冗余校驗(yàn)碼)是一種能力非常強(qiáng)的檢錯、糾錯碼,常用于串行傳送的輔助存儲器與主機(jī)的數(shù)據(jù)通信和計(jì)算機(jī)網(wǎng)絡(luò)中。它的基本原理是:在k位信息碼后再拼接r位的校驗(yàn)碼,整個編碼長度為n位,因此,這種編碼又叫(n,k)碼。對于一個給定的(n,k)碼,可以證明存在一個最高次冪位n-k=r的多項(xiàng)式g(x),根據(jù)g(x)可以生成七位信息的校驗(yàn)碼,而g(x)叫做這個CRC碼的生成多項(xiàng)式。

CAN總線協(xié)議就是采用的CRC校驗(yàn),并且是16位的C R C-1 6校驗(yàn)碼, 生成多項(xiàng)式為,可轉(zhuǎn)換為二進(jìn)制碼組1100010110011001。生成CRC碼的具體過程是:由幀起始、仲裁場、控制場、數(shù)據(jù)場(數(shù)據(jù)幀有數(shù)據(jù)場,遠(yuǎn)程幀沒有數(shù)據(jù)場)組成的被除數(shù)右移15位后與生成多項(xiàng)式的二進(jìn)制碼組進(jìn)行模2除,生成的15位余數(shù)就是所需的CRC碼。

本模塊的主要作用有兩個:1)在控制器處于發(fā)送狀態(tài)時,計(jì)算出CRC碼,同時將幀起始、仲裁場、控制場、(數(shù)據(jù)場)、CRO場按幀格式的要求進(jìn)行打包;2)在控制器處于接收狀態(tài)時,將接收到的由幀起始、仲裁場、控制場、(數(shù)據(jù)場)、CRC場組成的被除數(shù)與生成多項(xiàng)式的二進(jìn)制碼組進(jìn)行模2除,結(jié)果為0,則接受數(shù)據(jù),不為0,則丟棄數(shù)據(jù),并產(chǎn)生CRC校驗(yàn)錯誤。

1.2.3 立填充模塊

在CAN總線協(xié)議中,當(dāng)控制器處于發(fā)送或接收狀態(tài)時,若控制器檢測到總線上出現(xiàn)連續(xù)6個相同極性的電平時(幀結(jié)尾除外),控制器將會檢測到錯誤而停止發(fā)送或接收數(shù)據(jù),此時控制器將會由發(fā)送或接收狀態(tài)轉(zhuǎn)換為錯誤狀態(tài)。

本模塊的主要作用是:在發(fā)送狀態(tài)時,連續(xù)發(fā)送5個相同極性的位時,若第5位與將要發(fā)送的第6位極性不同時,在第5位和第6位之間插入1個極性與第6位相同的位,若第5位與將要發(fā)送的第6位極性相同,在第5位和第6位之間插入1個極性與第6位相反的位;在接收狀態(tài)時,連續(xù)接收5個相同極性的位時,若第6位與之前5位的極性不同,則舍棄第6位,若第6位與之前5位的極性相同,則產(chǎn)生位填充錯誤,控制器將停止接收數(shù)據(jù),此時控制器也將由接收狀態(tài)轉(zhuǎn)換為錯誤狀態(tài)。同時,本模塊也具有檢測位錯誤,位填充錯誤,形式錯誤及應(yīng)答錯誤的功能。另外,模塊還具有生成錯誤幀、過載幀、間歇幀的功能。

1.2.4 狀態(tài)機(jī)模塊

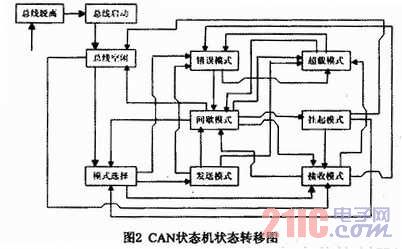

狀態(tài)機(jī)模塊在整個控制器中扮演著“大腦”的作用,它控制著其它模塊的操作。相比于文獻(xiàn)中未采用狀態(tài)機(jī)的設(shè)計(jì),采用狀態(tài)機(jī)會使得各個模塊的功能作用更為明確,系統(tǒng)結(jié)構(gòu)更為清晰合理,同時也更便于各個模塊之間的協(xié)調(diào)控制。本狀態(tài)機(jī)模塊的設(shè)計(jì)采用和文獻(xiàn)中相同的設(shè)計(jì),將控制器分為了10種模式:總線脫離、總線啟動、總線空閑、模式選擇、發(fā)送模式、接收模式、錯誤模式、間歇模式、超載模式及掛起模式。CAN狀態(tài)機(jī)狀態(tài)轉(zhuǎn)移圖如圖2所示。

掉電、復(fù)位及總線上過多的錯誤都會使控制器進(jìn)入總線脫離模式;系統(tǒng)上電、復(fù)位解除或過多錯誤而復(fù)位后的下個時鐘會使控制器進(jìn)入總線啟動模式;在總線啟動模式下,若之前因掉電、復(fù)位使控制器進(jìn)入總線脫離模式,當(dāng)控制器監(jiān)測到總線上1次連續(xù)11個隱性位(邏輯電平1”)時,控制器進(jìn)入總線空閑狀態(tài),若因過多錯誤使控制器進(jìn)入總線脫離模式,則當(dāng)控制器監(jiān)測到總線上128次連續(xù)11個隱性位時,控制器進(jìn)入總線空閑模式;當(dāng)控制器沒有數(shù)據(jù)發(fā)送但監(jiān)測到總線上有顯性位(邏輯電平“0”)時,控制器進(jìn)入接收模式,而當(dāng)控制器有數(shù)據(jù)發(fā)送同時監(jiān)測到總線上有顯性位時,控制器進(jìn)入模式選擇模式;模式選擇其實(shí)就是一個總線仲裁,此時標(biāo)識符將扮演仲裁位的角色,顯性位的優(yōu)先級更高,若總線仲裁失敗則控制器進(jìn)入接收模式,仲裁成功則進(jìn)入發(fā)送模式;一幀數(shù)據(jù)成功發(fā)送完成后,控制器會進(jìn)入間歇模式;若間歇幀發(fā)送成功,則控制器會再次進(jìn)入總線空閑模式。狀態(tài)機(jī)由空閑模式轉(zhuǎn)換為模式選擇模式的仿真圖如圖3所示。

1.2.5 位定時模塊

位定時模塊控制著控制器報(bào)文發(fā)送或接收的節(jié)奏,這個節(jié)奏就是位時間,它由四部分組成:同步段、傳播段、相位緩沖段1和相位緩沖段2,這四個段均由時間份額構(gòu)成,時間份額是根據(jù)預(yù)先設(shè)置的分頻值對輸入時鐘進(jìn)行分頻得到的。

位定時模塊還有一個重要的功能是將本節(jié)點(diǎn)與總線上的其它節(jié)點(diǎn)進(jìn)行時鐘同步。由于每個CAN節(jié)點(diǎn)使用的是獨(dú)立的時鐘,所以不同節(jié)點(diǎn)之間會有相位差,這些相位差嚴(yán)重時會影響報(bào)文發(fā)送和接收的準(zhǔn)確性,所以有必要對不同節(jié)點(diǎn)進(jìn)行時鐘同步。

2 系統(tǒng)驗(yàn)證

整個系統(tǒng)的功能仿真和時序仿真是借助Modelsim軟件完成的。圖4所示是對控制器發(fā)送數(shù)據(jù)的驗(yàn)證,測試用的發(fā)送數(shù)據(jù)為隨意選擇的:00101001,仲裁場和控制場也是任選的,分別為:110100101110、110001,設(shè)置好寄存器組后,控制器計(jì)算出對應(yīng)的CRC碼為:110111001111 011,之后控制器將數(shù)據(jù)按CAN協(xié)議的幀格式打包逐位發(fā)送出去。

控制器最初處于總線脫離模式,復(fù)位結(jié)束后進(jìn)入總線啟動模式,當(dāng)控制器檢測到總線上的1次連續(xù)11個隱性位時,進(jìn)入總線空閑模式,接著當(dāng)控制器檢測到總線出現(xiàn)第一個顯性位時,進(jìn)入模式選擇模式,在此模式下,控制器進(jìn)行的操作就是總線仲裁,確定本節(jié)點(diǎn)是否獲得總線控制權(quán),由于本測試采用的是控制器自測模式,即輸出線與輸入線連在一起,所以仲裁時間為12個位時間,仲裁成功后,控制器會進(jìn)入發(fā)送模式,若無錯誤產(chǎn)生,數(shù)據(jù)發(fā)送完成后控制器進(jìn)入間歇模式,最后進(jìn)入總線空閑模式。

經(jīng)過一系列的測試驗(yàn)證后,表明本CAN總線控制器能夠發(fā)送或接收所有符合CAN2.0A協(xié)議的報(bào)文幀。

3 結(jié)束語

本設(shè)計(jì)實(shí)現(xiàn)了所有符合CAN2.0A協(xié)議的CAN總線控制器功能,最高工作頻率為139.43MHz,這也達(dá)到了最初的設(shè)計(jì)目的。控制器的時序分析如圖5所示。

本文作者創(chuàng)新點(diǎn)為:首先控制器的外圍接口采用Avalon總線接口,這使得本設(shè)計(jì)的通用性更強(qiáng):其次是本設(shè)計(jì)的最高工作頻率達(dá)到了139.43MHz,能夠適應(yīng)高速通信的要求。