1.引言

數(shù)字下變頻(DDC)技術(shù)是軟件無線電接收機(jī)的核心技術(shù)。其基本功能是從輸人的寬帶高速數(shù)字信號(hào)中提取所需的窄帶信號(hào),將其下變頻為數(shù)字基帶信號(hào),并轉(zhuǎn)換成較低的數(shù)據(jù)率,以供后續(xù)的DSP作進(jìn)一步的處理。目前許多型號(hào)的DDC芯片事實(shí)上其功能己遠(yuǎn)遠(yuǎn)不只是下變頻,還包括了成形濾波器、定時(shí)同步內(nèi)插濾波器、重采樣NCO、坐標(biāo)變換、數(shù)字ACC等功能,其結(jié)構(gòu)如圖1所示。

CORDIC(Coordinate Rotation Digital Computer)是一種迭代算法,它提供了計(jì)算三角函數(shù)和欠量求模的方法。該算法僅利用加法和移位兩種運(yùn)算通過迭代方式進(jìn)行矢量旋轉(zhuǎn),因此,它非常適合于硬件A-SIC實(shí)現(xiàn)。本文所要闡述的就是基于CORDIC算法的數(shù)字下變頻器中坐標(biāo)變換模塊的ASIC實(shí)現(xiàn)結(jié)構(gòu),該模塊的主要功能是實(shí)現(xiàn)直角坐標(biāo)系到極坐標(biāo)系的變換,從而求得由I路信號(hào)和Q路信號(hào)構(gòu)成的向量的幅度值和相位值,將得到的幅度信息返回給前級(jí)的數(shù)字AGC進(jìn)行增益控制,還可以實(shí)現(xiàn)對(duì)FM信號(hào)的解調(diào)。

2.CORDIC算法與實(shí)現(xiàn)

2.1 CORDIC算法原理

CORDIC是一種迭代算法,它可以用來計(jì)算sin,cos等三角函數(shù),計(jì)算幅值和相位等到所需的精度,CORDIC算法計(jì)算幅值和相位的原理如下:

假設(shè)直角坐標(biāo)系內(nèi)有向量A(Xn,Yn),向量A順時(shí)針旋轉(zhuǎn)θn后得到向量B(Xn,Yn),如圖2所示。

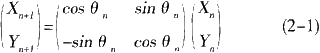

向量A和向量B之間存在以下關(guān)系,用矩陣表示為

將cosθn提出以后得到

在這里我們?nèi)?i=arctan(1/2i),所有迭代的總和為 ,其中Si={-1,+1},則tanθi=Si2-i,可得

,其中Si={-1,+1},則tanθi=Si2-i,可得

上式Si中的符號(hào)決定了向量的旋轉(zhuǎn)方向,當(dāng)時(shí)Yi≥0,Si=1,順時(shí)針旋轉(zhuǎn);當(dāng)Yi<0時(shí),Si=-1,逆時(shí)針旋轉(zhuǎn),式中的cosθi=cos(arctan(1/2i),隨著迭代次數(shù)的增加它收斂于一個(gè)常數(shù),我們暫不考慮這個(gè)常數(shù)增益,這樣式(2-3)就變?yōu)?br />

設(shè)總共旋轉(zhuǎn)的角度為,初值為0,則 ,給定向量 一組初值如下

,給定向量 一組初值如下

從上面的式子可以看出,當(dāng)向量A旋轉(zhuǎn)到X軸時(shí),可以得到迭代的結(jié)果為  ,即可求得向量A的幅值和相位。由式(2-4)可知每次旋轉(zhuǎn)的角度的正切值都是2的負(fù)冪次,在硬件實(shí)現(xiàn)時(shí)只需要執(zhí)行右移和相加運(yùn)算就可以實(shí)現(xiàn)每次迭代,易于硬件的實(shí)現(xiàn)。

,即可求得向量A的幅值和相位。由式(2-4)可知每次旋轉(zhuǎn)的角度的正切值都是2的負(fù)冪次,在硬件實(shí)現(xiàn)時(shí)只需要執(zhí)行右移和相加運(yùn)算就可以實(shí)現(xiàn)每次迭代,易于硬件的實(shí)現(xiàn)。

2.2 用CORDIC算法的流水結(jié)構(gòu)實(shí)現(xiàn)坐標(biāo)變換

CORDIC迭代結(jié)構(gòu)如圖3所示,采用流水結(jié)構(gòu)每次迭代完成一次旋轉(zhuǎn),每級(jí)迭代都用寄存器寄存,這樣每個(gè)時(shí)鐘周期都可以計(jì)算出一次幅度和相位。迭代的次數(shù)越多,精度越高,當(dāng)然耗費(fèi)的資源也就越多。

在數(shù)字下變頻器輸出I,Q兩路信號(hào)后(輸出信號(hào)用補(bǔ)碼表示),用CORDIC實(shí)現(xiàn)坐標(biāo)變換時(shí),為簡化電路結(jié)構(gòu),只用計(jì)算的相角,其他象限的相角,采用處理后再映射的辦法求取,岡此,對(duì)剛進(jìn)入的數(shù)據(jù)會(huì)進(jìn)行預(yù)處理。首先就是求輸人數(shù)據(jù)的絕對(duì)值,并記錄符號(hào)位作為處理后象限映射的依據(jù)。接下來,會(huì)判斷I,Q兩路數(shù)據(jù)的大小關(guān)系,并將較小的值交換到Q路,這樣做的目的是要在同樣的迭代次數(shù)下,達(dá)到更高的迭代精度。進(jìn)入CORDIC迭代單元前會(huì)對(duì)I,Q兩路數(shù)據(jù)進(jìn)行位寬拓展,從而保證CORDIC迭代過程中,不會(huì)因截?cái)嗾`差造成太大的偏差。經(jīng)過CORDIC迭代后所得的幅度值是有增益的,此時(shí)需要對(duì)其進(jìn)行修正,另一方面,相位值需根據(jù)先前記錄的I,Q兩路數(shù)據(jù)的符號(hào)位和I,Q兩路數(shù)據(jù)交換的情況作象限映射,表1列出了相位映射的規(guī)則。坐標(biāo)變換模塊的實(shí)現(xiàn)結(jié)構(gòu)如圖4所示。

2.3 使用modeIsim仿真的結(jié)果

圖5是當(dāng)輸入激勵(lì)為I路:sin(sin2πf);Q路:COS(COS2πf)時(shí)的modelsim仿真結(jié)果,由圖中可以看出坐標(biāo)變換得出的相位值是一個(gè)標(biāo)準(zhǔn)正弦信號(hào),幅度值為恒定值,幅度相位完全正確。

2.4 硬件實(shí)現(xiàn)結(jié)果

在硬件實(shí)現(xiàn)時(shí),用verilog語言對(duì)坐標(biāo)變換模塊進(jìn)行描述,為滿足DDC的精度要求進(jìn)行了18次迭代,并用DC基于UMC0.18μm的庫進(jìn)行了綜合,硬件實(shí)現(xiàn)結(jié)果如圖6所示。

圖6(a)是DC綜合后的面積報(bào)告,圖6(c)是關(guān)鍵路徑的時(shí)序報(bào)告,綜合后的最大路徑延時(shí)為9.77ns,完全可以滿足本模塊數(shù)字下變頻器100MHz的處理速度要求,綜合出的單元(cell)的總面積僅為0.27。圖6(b)是該設(shè)計(jì)在FPGA上驗(yàn)證的結(jié)果,該DDC的工作頻率為80MHz,通道2為輸入的基帶信號(hào)頻率20kHz,載波頻率5MHz,頻偏200KHz的FM信號(hào),通道1是通過DDC下變頻后交給坐標(biāo)變化模塊的I,O兩路信號(hào)求出的相位信息,即頻率為20kHz的正弦信號(hào),由圖可知該沒計(jì)實(shí)現(xiàn)了坐標(biāo)變換功能。

3 結(jié)論

使用CORDIC算法,并用流水結(jié)構(gòu)實(shí)現(xiàn)幅度相位的求取可以獲得較高的處理速度,增加迭代次數(shù)可以獲得更高的處理精度,但會(huì)耗費(fèi)較多的資源,在設(shè)計(jì)時(shí)應(yīng)根據(jù)需要,合理的確定迭代次數(shù)。該設(shè)計(jì)已成功應(yīng)用于高速數(shù)字下變頻芯片中。