1 引言

DDR3 SDRAM是由JEDEC(電子設(shè)備工程聯(lián)合委員會(huì))制定的全新下一代內(nèi)存技術(shù)標(biāo)準(zhǔn),具有 速度更快、功耗更低、效能更高以及信號(hào)質(zhì)量更好等優(yōu)點(diǎn),對(duì)于解決高速系統(tǒng)(例如某些高速圖 像處理系統(tǒng))設(shè)計(jì)中由于存儲(chǔ)器的處理速度和帶寬所產(chǎn)生的瓶頸,改善和提高系統(tǒng)性能提供了更 好的解決方案。

本文在分析DDR3 SDRAM的特點(diǎn)和基本控制方式的基礎(chǔ)上,給出了采用Altera公司最新的 ALTMEMPHY高速存儲(chǔ)器接口方案設(shè)計(jì)的DDR3 SDRAM控制器,并在Altera公司的StratixIII系列 FPGA上完成了驗(yàn)證和實(shí)現(xiàn)。目前,使用該控制器的DDR3 SDRAM已經(jīng)在某真三維立體顯示器項(xiàng)目 中作為高速圖像緩存得到了實(shí)際應(yīng)用。

2 DDR3 SDRAM的特點(diǎn)

與上一代器件相比,DDR3內(nèi)存技術(shù)仍然采用了在時(shí)鐘的上升沿和下降沿同時(shí)進(jìn)行數(shù)據(jù)傳輸 的基本方式,工作原理與控制方式基本相同,但又有著一些不同的新特點(diǎn):擁有兩倍于DDR2的 8bit預(yù)取(prefetch)能力;突發(fā)長度(Burst Length,BL)固定為8,且增加了突發(fā)突變(Burst Chop)模式;新增了重置(Reset)功能,可以使DDR3達(dá)到功耗最小的狀態(tài)等[1]。

與其它SDRAM一樣,DDR3 SDRAM的操作指令主要通過RAS(行地址選擇)、CAS(列地址選擇)、 WE(寫使能信號(hào))、CS(片選信號(hào))以及CKE(時(shí)鐘使能信號(hào))的高低電平組合來實(shí)現(xiàn)。但基于 其自身特點(diǎn),DDR3指令集內(nèi)不但對(duì)原有的指令做了很多改動(dòng),同時(shí)也增加了一些新的指令,時(shí) 序方面也有一定的差別。

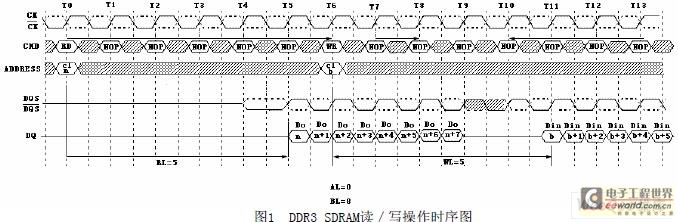

在讀寫操作方面,與DDR2一樣,讀操作時(shí)由內(nèi)存給出一個(gè)與數(shù)據(jù)同步的DQS信號(hào),它的邊沿 與讀數(shù)據(jù)一致;寫操作時(shí),控制器同樣給出一個(gè)與數(shù)據(jù)同步的數(shù)據(jù)濾波信號(hào)DQS,它的邊沿處于寫數(shù)據(jù)當(dāng)中.DDR3具有on-the-fly突發(fā)模式,允許用戶在此模式下選擇4或8的突發(fā)長度。圖1 給出了DDR3內(nèi)存典型的讀/寫操作時(shí)序圖[2]。

3 DDR3 SDRAM控制器的設(shè)計(jì)

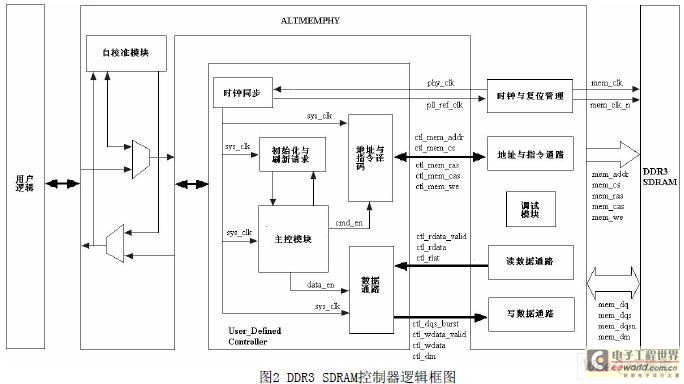

DDR3 SDRAM控制器的設(shè)計(jì)方法采用了Altera推薦的ALTMEMPHY+用戶自定義控制器的結(jié)構(gòu)。 與傳統(tǒng)SDRAM控制器相比,此結(jié)構(gòu)加入了ALTMEMPHY接口部分。ALTMEMPHY宏功能是Altera開發(fā)的 能夠動(dòng)態(tài)自校準(zhǔn)的數(shù)據(jù)通路,允許用戶在Stratix III等器件中快速建立物理層接口(physical layer interface),連接FPGA內(nèi)部控制邏輯和外部存儲(chǔ)器。使用ALTMEMPHY的的突出優(yōu)點(diǎn)是可 以通過訓(xùn)練模式和校準(zhǔn)功能來消除FPGA和存儲(chǔ)器在制造工藝中的偏差。在工作過程中,它利用 跟蹤機(jī)制來跟蹤并補(bǔ)償FPGA內(nèi)部的電壓或者溫度變化,而且不會(huì)中斷數(shù)據(jù)傳輸。DDR3 SDRAM控 制器的邏輯框圖如圖2所示,主要包括ALTMEMPHY和用戶自定義控制器兩部分。

為了簡(jiǎn)化內(nèi)部邏輯設(shè)計(jì),提高系統(tǒng)性能,控制器設(shè)計(jì)采用半速率方案。所謂半速率方案, 就是將雙倍數(shù)據(jù)速率(DDR)轉(zhuǎn)換為時(shí)鐘頻率減半,并且只在時(shí)鐘上升沿進(jìn)行數(shù)據(jù)采集的半數(shù)據(jù) 速率(HDR)。采用半速率方案后,內(nèi)部邏輯頻率為外部存儲(chǔ)器接口頻率的一半,但是內(nèi)部數(shù)據(jù) 總線的寬度是外部數(shù)據(jù)總線寬度的4倍。在內(nèi)部頻率受限,外部引腳數(shù)給定時(shí),半速率方案比全 速率方案支持的帶寬加倍。

3.1 ALTMEMPHY設(shè)計(jì)

ALTMEMPHY是可配置參數(shù)的宏功能,用戶可根據(jù)設(shè)計(jì)需要配置相應(yīng)參數(shù)[3]。ALTMEMPHY主要 包括時(shí)鐘與復(fù)位管理、地址與指令通路、讀數(shù)據(jù)通路、寫數(shù)據(jù)通路、自校準(zhǔn)等組成模塊。

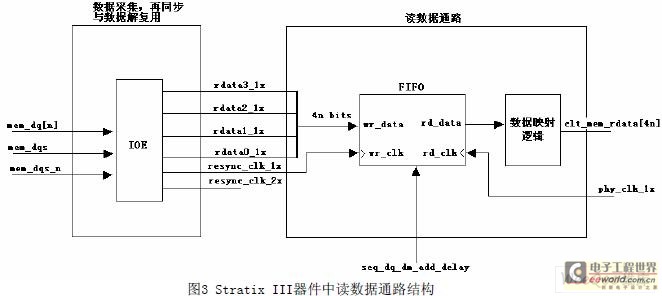

時(shí)鐘與復(fù)位管理模塊主要負(fù)責(zé)時(shí)鐘信號(hào)的產(chǎn)生與移相,以及時(shí)鐘網(wǎng)絡(luò)類型的控制;地址與 指令通路負(fù)責(zé)接收控制器輸出的地址和指令信號(hào),并將其從半速率時(shí)鐘轉(zhuǎn)換為全速率時(shí)鐘;讀 數(shù)據(jù)通路是采集從存儲(chǔ)器讀出的數(shù)據(jù),并將其再同步到系統(tǒng)時(shí)鐘域;寫數(shù)據(jù)通路將控制器輸出 的半速率數(shù)據(jù)轉(zhuǎn)換為雙倍速率(DDR)信號(hào),以寫入DDR3器件;自校準(zhǔn)模塊用于系統(tǒng)上電時(shí)自動(dòng) 校準(zhǔn)DDR3器件的過程變量,以獲得最大的時(shí)序余量,消除來自讀數(shù)據(jù)通路的不確定因素,提高 系統(tǒng)高頻工作下的穩(wěn)定性。圖3所為Stratix III器件中讀數(shù)據(jù)通路的結(jié)構(gòu)框圖,由圖中可以看 出DDR與HDR轉(zhuǎn)換的過程中數(shù)據(jù)總線寬度及時(shí)鐘頻率的變化。

3.2 自定義控制器設(shè)計(jì)

用戶自定義控制器部分主要由以下模塊組成:主控模塊、地址與指令譯碼、數(shù)據(jù)緩沖、時(shí) 鐘同步、初始化與刷新請(qǐng)求等[4]。 主控模塊主要由有限狀態(tài)機(jī)實(shí)現(xiàn),完成系統(tǒng)從上電開始所有狀態(tài)間的轉(zhuǎn)換、任務(wù)調(diào)度、總 線仲裁、時(shí)序同步等,并對(duì)其他模塊產(chǎn)生相應(yīng)的控制信號(hào),協(xié)調(diào)各模塊工作;地址與指令譯碼 模塊在主控模塊的控制下,完成對(duì)系統(tǒng)各種訪問指令和訪問地址的解碼與匹配;數(shù)據(jù)緩沖負(fù)責(zé) 在與ALTMEMPHY進(jìn)行數(shù)據(jù)傳輸過程中對(duì)數(shù)據(jù)進(jìn)行FIFO緩沖和同步;時(shí)鐘同步模塊采用了PLL鎖相 環(huán)電路設(shè)計(jì),為ALTMEMPHY提供參考時(shí)鐘,同時(shí)接收ALTMEMPHY輸出的同步時(shí)鐘phy_clk作為系統(tǒng) 時(shí)鐘,完成各模塊之間的同步;初始化與刷新請(qǐng)求模塊完成SDRAM器件的初始化及自刷新操作。

3.3 設(shè)計(jì)注意事項(xiàng)

本系統(tǒng)工作頻率高,任何微小的時(shí)序錯(cuò)誤都可能導(dǎo)致系統(tǒng)不能正確工作。雖然ALTMEMPHY 結(jié)構(gòu)可以在一定程度上減小時(shí)序錯(cuò)誤,但在設(shè)計(jì)過程中仍要做好代碼的優(yōu)化,盡量采用同步電 路設(shè)計(jì)方法,消除競(jìng)爭(zhēng)冒險(xiǎn)現(xiàn)象,保證數(shù)據(jù)接口的同步等。

另外,在設(shè)計(jì)中要遵照Altera提供的設(shè)計(jì)規(guī)范進(jìn)行設(shè)計(jì),如時(shí)鐘信號(hào)要從片上PLL專用的全 局時(shí)鐘引腳輸入以減小時(shí)鐘傾斜;各種時(shí)鐘分別配置于各自獨(dú)立的時(shí)鐘局域網(wǎng)絡(luò)內(nèi)以避免相位 攪動(dòng);對(duì)周期、建立、保持時(shí)間等關(guān)鍵參數(shù)添加相應(yīng)的約束等等,以提高設(shè)計(jì)的工作頻率,增 強(qiáng)系統(tǒng)的穩(wěn)定性。

4 DDR3 SDRAM控制器的實(shí)現(xiàn)

設(shè)計(jì)采用的FPGA為Stratix III系列中的EP3SL150F1152-C2。Stratix III是Altera公司剛剛面市高端FPGA系列,也是目前少數(shù)支持DDR3接口的FPGA之一。Stratix III系列提供讀寫均衡、 DQ去斜移I/O延時(shí)、動(dòng)態(tài)片內(nèi)匹配等功能,并且使用可配置鎖相環(huán)(PLL)來補(bǔ)償電壓和溫度變化, 以充分發(fā)揮DDR3存儲(chǔ)器的優(yōu)勢(shì)。Stratix III器件支持最大時(shí)鐘速率400 MHz、最大數(shù)據(jù)速率800 Mbps的DDR3[5]。軟件設(shè)計(jì)在Altera公司的Quartus II 7.2平臺(tái)上,運(yùn)用自頂向下的設(shè)計(jì)思想, 采用VHDL語言加電路圖混合設(shè)計(jì)的方法完成。測(cè)試讀寫仿真時(shí)序如圖4所示。

本設(shè)計(jì)采用Samsung公司的1Gb容量DDR3 SDRAM芯片K4B1G0846C-ZCF7予以實(shí)現(xiàn)。該芯片組織 結(jié)構(gòu)為16Mbit x 8 I/Os x 8banks,速率為800Mbps。通過仿真和工作實(shí)測(cè),系統(tǒng)穩(wěn)定工作頻率 達(dá)到400MHz,8位數(shù)據(jù)總線帶寬最大傳輸率達(dá)到800MB/s[6]。 從設(shè)計(jì)的仿真及實(shí)現(xiàn)結(jié)果可以看出,這種結(jié)構(gòu)的控制器具有很高的傳輸速度和穩(wěn)定的性能 表現(xiàn),可以作為下一代存儲(chǔ)設(shè)備廣泛運(yùn)用于各種高速高性能系統(tǒng)設(shè)計(jì)中。同時(shí),該設(shè)計(jì)為相關(guān) 控制器的開發(fā)和研制提供了實(shí)例,具有良好的參考和應(yīng)用價(jià)值。

本文作者創(chuàng)新點(diǎn):提出了一種基于Stratix III的DDR3 SDRAM控制器的設(shè)計(jì)方法,采用 ALTMEMPHY宏功能結(jié)合自定義控制器的結(jié)構(gòu),即保證了系統(tǒng)在高速運(yùn)行時(shí)的穩(wěn)定性,又可以根據(jù) 用戶需要靈活改變參數(shù)設(shè)置,可廣泛應(yīng)用于各種相關(guān)高速數(shù)字系統(tǒng)。