0 引言

隨著雷達技術的快速發(fā)展,尤其是現(xiàn)代雷達采用了脈沖壓縮、相位編碼等復雜的調制技術,使得傳統(tǒng)的電子欺騙干擾很難奏效。DRFM技術是現(xiàn)代電子戰(zhàn)中的前沿技術之一,它能精確復制對方的雷達信號,并采用欺騙、遮蓋復合的調制方式在時間、空間、頻率以及調制方式等多維信息域內對雷達實施最佳干擾而不受速度和距離的影響。因此,DRFM技術已成為電子戰(zhàn)中研究的熱點。

PXIE架構本身就是在CPCI基礎上衍生出來的,適用于儀器測試環(huán)境的架構。該架構在系統(tǒng)供電、抗震、信號形式等一系列方面都擁有全面和優(yōu)越的保護措施,從而從整體上保證了系統(tǒng)的穩(wěn)定性。

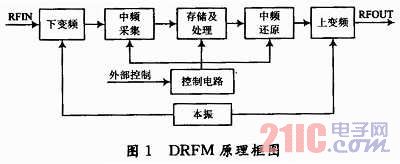

1 DRFM基本原理

數(shù)字射頻存儲器是一種能夠存儲射頻信號,并對其做延遲等相關處理,并且在處理后能精確輸出的存儲設備。系統(tǒng)原理框圖如圖1所示。系統(tǒng)可分為本振電路、上、下變頻電路、中頻信號采集電路、存儲電路、中頻信號還原電路及處理和協(xié)調控制電路等。輸入射頻信號經(jīng)下變頻后被中頻采集卡采樣,采樣信號被送往高速存儲模塊進行存儲,處理器按照設定的處理方式對信號進行相關處理后,經(jīng)中頻還原卡將信號還原,再經(jīng)上變頻模塊還原射頻信號。還原出來的信號經(jīng)放大便可發(fā)射出去實施電子干擾和欺騙等。

2 DRFM方案設計

按照PXIE的模塊化設計原則,DRFM主要包括上、下變頻模塊、中頻采集模塊、中頻還原模塊和固態(tài)存儲模塊。上、下變頻模塊將輸入的射頻信號下變頻至中頻信號以及將輸出的信號上變頻至射頻信號;中頻采集模塊完成中頻信號的采集和傳輸;固態(tài)存儲模塊在控制電路的作用下實現(xiàn)信號的高速存取;中頻還原模塊將處理后的數(shù)字信號還原成模擬信號。在DRFM中中頻采集模塊、中頻還原模塊和固態(tài)存儲模塊是系統(tǒng)的關鍵,下面分別介紹。

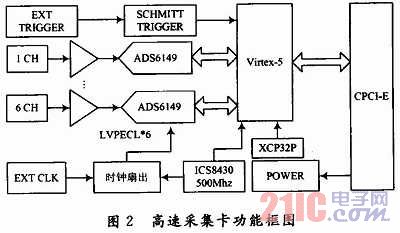

2.1 中頻采集模塊設計

中頻信號采集模塊主要是完成中頻信號的模/數(shù)轉換,并將轉換后的數(shù)據(jù)通過FPGA處理后傳輸給存儲模塊。主要由前端調理電路、6片高速ADC、時鐘分配電路、FPGA、電源五部分組成,前端信號調理電路主要是完成信號的放大或者是衰減,以匹配A/D的輸入要求,高速ADC完成模數(shù)轉換,F(xiàn)PGA負責接受A/D的數(shù)據(jù)和傳輸以及整塊板卡的控制。其構成框圖如圖2所示。

該設計的高速ADC采用TI公司的高速ADC即ADS6149。ADS6149是一款高性能的14位,250 Mb/s采樣率模/數(shù)轉換器,它提供出色的高模擬帶寬和低輸入抖動,在高頻信號輸入時,ADC提供極高的SNR和SFDR指標,其內部包括可編程增益設置,可以用于提高小信號輸入時的SFDR性能。時鐘對于高速ADC系統(tǒng)而言尤其關鍵,這是因為時鐘信號的時序準確性可以直接影響ADC的動態(tài)特性。該設計選用ICS834061,它是一款集成高頻時鐘發(fā)生器,在單芯片中集成整個鎖相環(huán)系統(tǒng)和時鐘扇出系統(tǒng),外圍器件只要1個晶振,具有2路LVPECL時鐘扇出,輸出頻率范圍20~500 MHz可調,時鐘抖動最大只有6 ps,能滿足該設計的要求。

2.2 中頻還原模塊設計

中頻信號還原模塊完成處理后的信號的還原,主要由FPGA、高速DAC、后端調理電路、時鐘分配電路、控制信號發(fā)生電路,電源6部分組成,其中FPGA負責將處理之后的數(shù)據(jù)發(fā)給D/A轉換器以及整塊中頻還原卡的控制。高速ADC完成模/數(shù)轉換功能,后端調理電路提供A/D轉換后的濾波和信號放大功能,時鐘電路為系統(tǒng)提供高精度、低抖動的時鐘信號,其構成框圖如圖3所示。

該設計的高速DAC擬采用美信公司的高速DAC——MAX5887。MAX5887是先進的14位、500MS/s數(shù)/模轉換器(DAC),設計用于滿足要求性能苛刻的信號合成應用。該DAC工作于3.3 V單電源,提供優(yōu)越的動態(tài)性能,如76 dBc的無雜散動態(tài)范圍(SFDR)(Fout=30 MHz時)。MAX5887具有集成的1.2 V帶隙基準和控制放大器,以保證高精度和低噪聲特性。此外,單獨的基準輸入允許用戶外接基準,以獲得最大的靈活性和提高增益精度。該設計為提高D/A轉換器的性能,采用精密的、低壓差、微功耗電壓基準、溫度系數(shù)低至5 ppm/℃(最大值)的MAX6161來為MAX5 887提高參考。

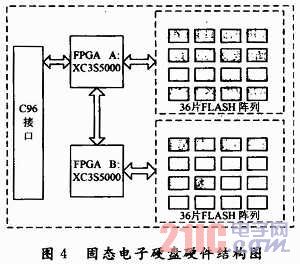

2.3 固態(tài)存儲模塊設計

數(shù)字射頻存儲器的一個技術難點就是實現(xiàn)大容量高速數(shù)據(jù)的存儲與讀取。而固態(tài)電子硬盤在存儲容量和存取速度方面都能滿足該設計的需求。固態(tài)電子硬盤卡以FPGA為控制核心,以FLASH為存儲介質,板上采用兩片型號為XC3S5000 FPGA,每片F(xiàn)PGA控制36片NAND FLASH,其結構如圖4所示。每片F(xiàn)LASH128 MB,合計約9.2 GB容量。

外部數(shù)據(jù)流以LVDS的方式通過C96接口傳入固態(tài)電子硬盤,以I/O方式把數(shù)據(jù)從固態(tài)電子硬盤讀出。兩片F(xiàn)PGA之間通過普通I/O互聯(lián),A片F(xiàn)PGA負責數(shù)據(jù)接收以及兩片F(xiàn)PGA之間的數(shù)據(jù)分配。這樣就解決了存取速度和存儲容量的問題。

3 結語

本文采用基于PXIE的模塊化設計,在工程應用領域具有更大的靈活性,系統(tǒng)完成了包括中頻信號采集模塊、中頻信號還原模塊和固態(tài)存儲模塊等電路的設計。中頻采集模塊采用6路采樣率為250 MHz、采樣精度為14位的高速A/D進行采樣,中頻還原模塊采用6路采樣率為500 MHz、精度為14位的高速DAC進行數(shù)/模轉換。為了提高存取速度和存儲深度,系統(tǒng)采用了固態(tài)電子硬盤作為存儲介質。與傳統(tǒng)的DRFM相比,

PXIE技術的應用使系統(tǒng)具有更高的靈活性,可以在對其中的一個或幾個模塊進行單獨更換或改進,具有更高的通用性。固態(tài)存儲技術的應用,大大提高了系統(tǒng)的存取速度,為進一步提高DRFM的性能提供了重要參考和奠定了堅實的基礎。