1 引言

現(xiàn)代控制系統(tǒng)中控制對象可能是復雜、分散的,,而且往往是并行,、獨立工作的,但整體上它們是相互關(guān)聯(lián)的有機組合,。因此,,控制信號的時序邏輯則要求更加精確。CPLD單片機為控制系統(tǒng)提供了技術(shù)支持,,由CPLD和單片機組成的多機系統(tǒng)具有邏輯控制方便,,時序精確,并行工作,,人機接口友好等優(yōu)點,。因此,本文提出了一種基于CPLD與單片機控制的多路精確延時控制系統(tǒng)的設計方案,。

2 設計指標與系統(tǒng)原理

2.1 設計指標

輸出多路脈寬為10 ms正脈沖信號,;

脈沖輸出時間獨立調(diào)節(jié),、顯示,;

時間調(diào)整范圍與精度為微秒級的調(diào)整范圍為l~199μs,調(diào)節(jié)精度為lμs,;毫秒級的調(diào)整范圍為1~199 ms,,調(diào)整精度為1 ms,;

提供計時基準信號和工作狀態(tài)提示聲音;

9 V電池供電,。

2.2 系統(tǒng)設計原理

2.2.1 系統(tǒng)時鐘

本系統(tǒng)設計由CPLD和多個單片機組成,,CPLD對24 MHz高精度一體化晶體振蕩器二分頻得到多路同步時鐘信號作為多個單片機的系統(tǒng)時鐘,并由各個單片機外脈沖信號引腳XTAL2注入,,二分頻確保信號的占空比為50%,,滿足單片機時鐘脈沖信號高低電平持續(xù)時間大于20 ns和最高脈沖頻率為12 MHz的要求,同時也提高系統(tǒng)的可靠性,。5l系列單片機采用定時控制方式,,具有固定的機器周期,1個機器周期共有12個振蕩脈沖周期,,則機器周期是振蕩脈沖的12分頻,。本系統(tǒng)采用12 MHz振蕩脈沖頻率,1個固定機器周期為1μs,,因此能保證設計指標所要求的最高控制精度,。

2.2.2 同步計時啟動信號

本系統(tǒng)設計由外部按鍵提供啟動信號,由于機械接觸點的彈性及電壓突跳等原因,,按鍵存在抖動效應,,為保證按鍵準確識別,本系統(tǒng)設計采用軟件去抖動,,再經(jīng)單片機引腳輸出無電壓毛刺的穩(wěn)定啟動信號,,再經(jīng)CPLD變換后,可提供多路同步計時啟動信號,。

2.2.3 輸出信號

本系統(tǒng)設計采用10 ms單脈沖信號作為各模塊單元控制輸出信號,,其輸出形式可根據(jù)需要通過軟件調(diào)整,并保證系統(tǒng)輸出信號的時序與邏輯關(guān)系,。

2.2.4 系統(tǒng)時序

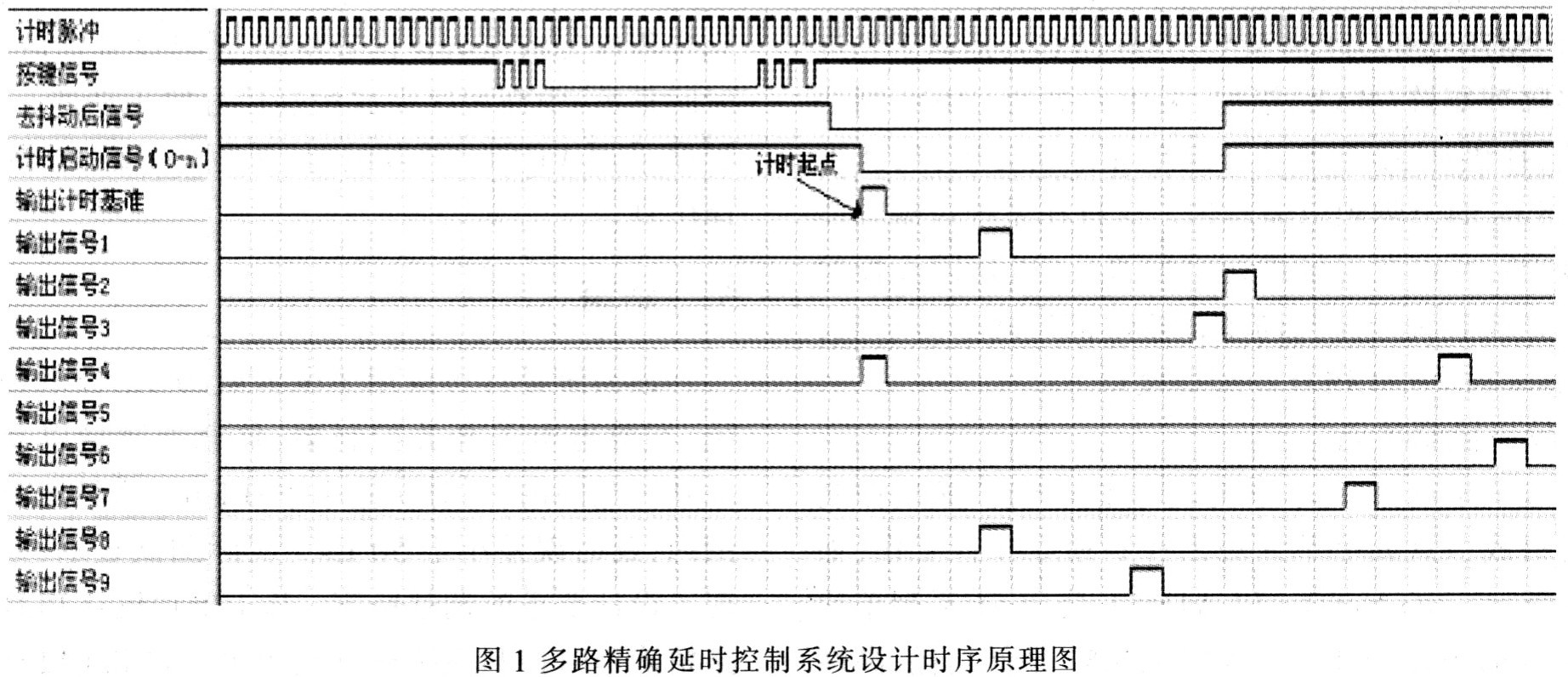

系統(tǒng)時序圖如圖1所示,,在計時脈沖的驅(qū)動下,按鍵信號經(jīng)去抖動變換,、CPLD邏輯同步后形成計時啟動信號(0一n),,以計時基準脈沖的前沿為計時起點,經(jīng)設定延時后,,系統(tǒng)輸出相應的輸出信號,,其延時時間可獨立調(diào)整,信號輸出形式可由軟件編程設置,。圖l采用單一正脈沖作為輸出信號,。

2.2.5 系統(tǒng)原理框圖

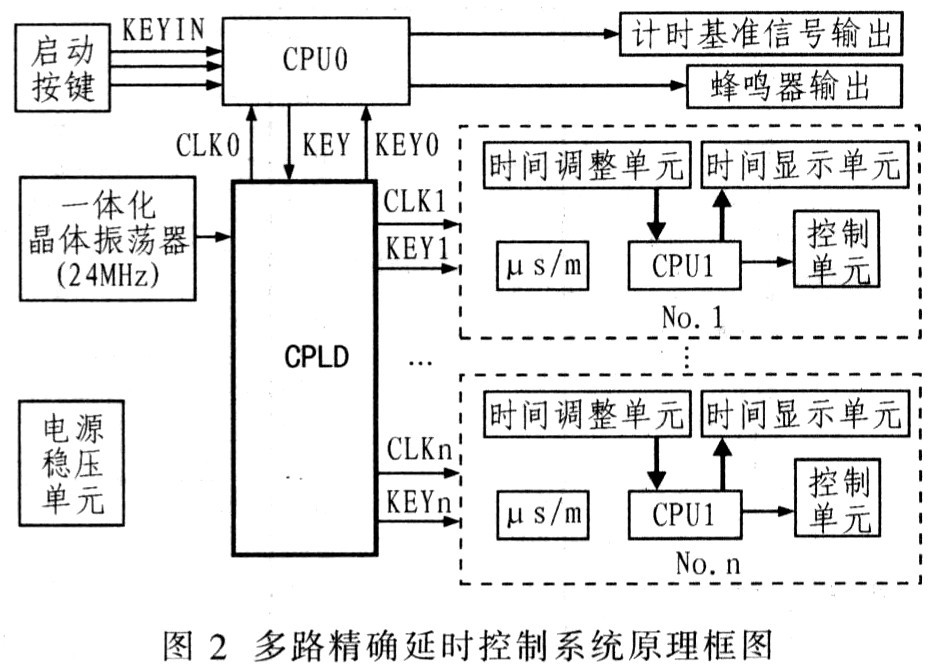

電源穩(wěn)壓單元實現(xiàn)系統(tǒng)5 V電源的穩(wěn)壓與濾波。單片機采用外部系統(tǒng)時鐘,。主控單片機CPUO完成按鍵檢測,、計時基準信號輸出和系統(tǒng)提示聲音輸出等功能,。NO.1~N0.n單元完成時間調(diào)整與顯示、μs/ms(微秒/毫秒)變換和信號輸出等功能,,CPLD完成時鐘2分頻,、同步計時脈沖輸出和計時啟動信號同步輸出功能。圖2為多路精確延時控制系統(tǒng)原理框圖,。

3 硬件電路設計

3.1 主控單元

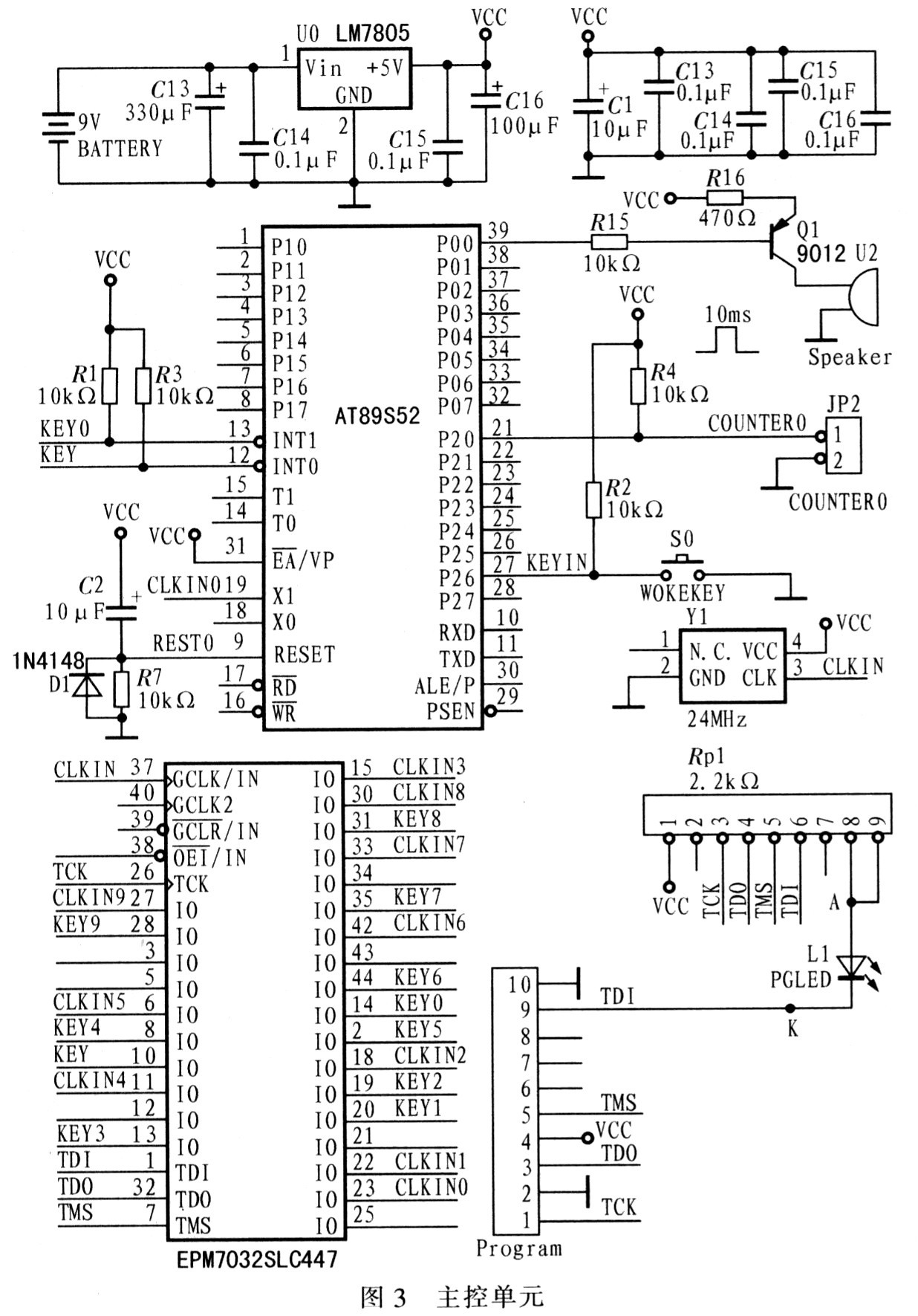

每個系統(tǒng)都由獨立的主控單元組成,,如圖3所示。主控單元由電壓,、CPUO和CPLD同步控制模塊等組成,。電壓模塊完成由可充電電池電壓到穩(wěn)定的5 V系統(tǒng)電源變換與濾波。CPUO單元模塊選用ATMEL公司51系列單片機AT89S52A,。AT89S52是低功耗,、高性能CMOS 8位微控制器,具有8 KB在系統(tǒng)可編程Flash存儲器,、256字節(jié)的隨機存取數(shù)據(jù)存儲器(RAM),、32個外部雙向輸入/輸出(I/O)端口、5個中斷優(yōu)先級2層中斷嵌套中斷,、2個16位可編程定時計數(shù)器,、2個全雙工串行通信口,看門狗(WDT)電路,,片內(nèi)時鐘振蕩器,,兼容標準MCS一5l指令系統(tǒng)。CPUO模塊完成按鍵信號檢測,,工作狀態(tài)提示音輸出,,計時基準信號輸出等功能。CPLD同步控制模塊采用ALTRA公司EPM7032SLC44為控制核心,。EPM7032SLC44是MAX7000 CPLD,,

是基于先進的多陣列矩陣(MAX)架構(gòu),采用先進的CMOS制造工藝,,提供從32到512個宏單元的密度范圍,,速度達3.5 ns的引腳到引腳延遲。支持在系統(tǒng)可編程能力(ISP),,可以在現(xiàn)場進行重配置,。CPLD同步控制單元完成時鐘分頻與同步,按鍵信號同步等功能,,ProKram插座是CPLD的編程接口,。

3.2 輸出控制單元

3.2 輸出控制單元

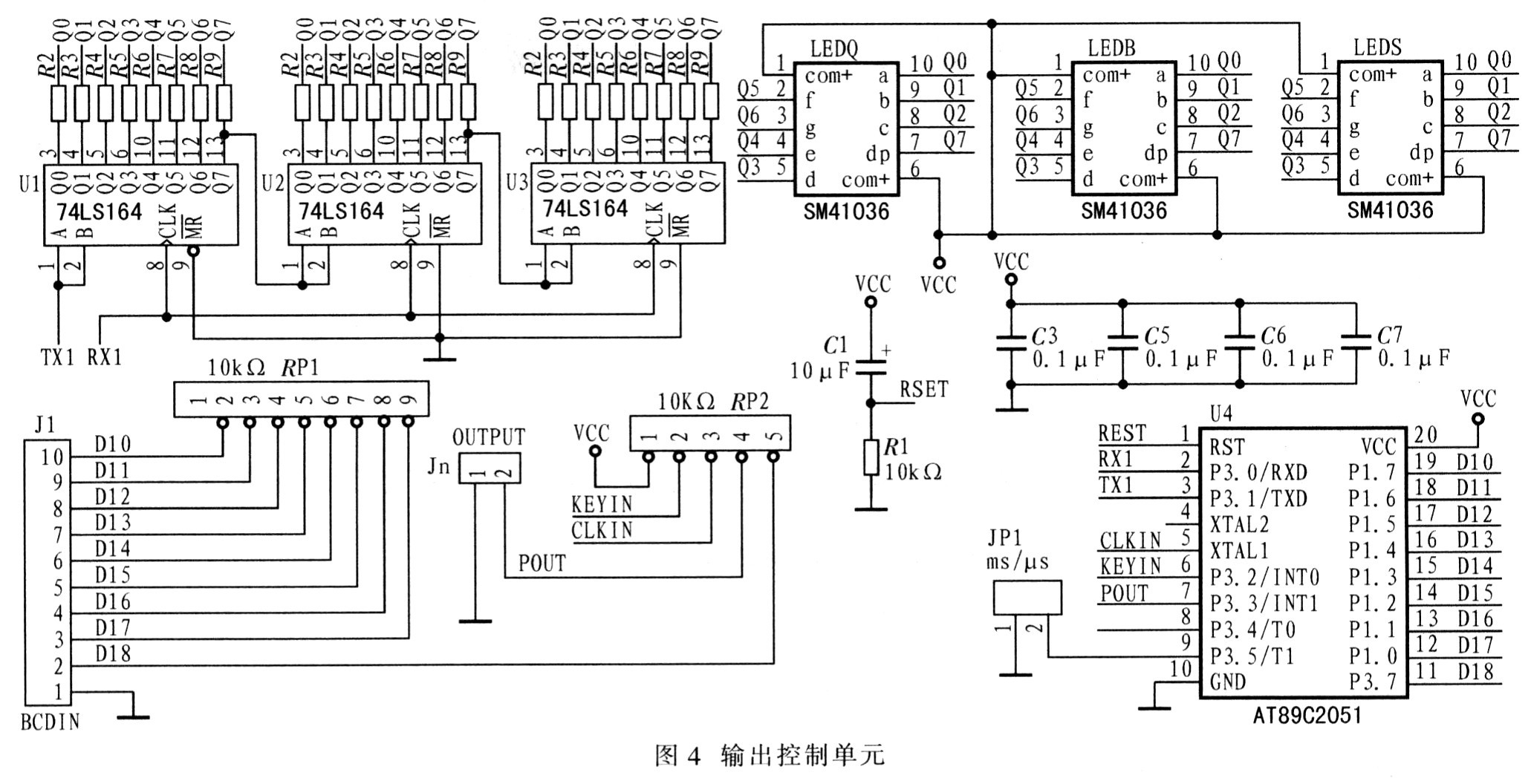

每個系統(tǒng)由n(本系統(tǒng)設計中n=9)個輸出控制單元組成,這n個單元輸出控制獨立并行工作,如圖4所示,。N0.1~N0.n以ATMEL公司5l系列單片機AT89C2051為核心。AT89C205l是低功耗,、高性能CMOS 8位單片機,,具有15個雙向輸入/輸出(I/O)端口、片內(nèi)含2 K字節(jié)的可反復擦寫的只讀Flash程序存儲器和128字節(jié)的隨機存取數(shù)據(jù)存儲器(RAM),;采用ATMEL公司的高密度,、非易失性存儲技術(shù)生產(chǎn),兼容標準MCS一5l指令系統(tǒng),。輸出控制單元(NO.1~NO.n)并行工作,,完成延時時間設置、μs/ms變換設置,、控制信號輸出和延時顯示等功能,,延時時間顯示通過單片機串口實現(xiàn),由3片串/并變換器件74LSl64驅(qū)動3個共陽數(shù)碼管,。

4 系統(tǒng)軟件設計

本系統(tǒng)軟件設計包括CPUO單元,、NO.1~NO.n輸出單元及CPLD單元程序設計。由于對時間要求嚴格,,采用匯編語言編寫,,信號輸出由中斷程序完成,由于中斷響應過程,、現(xiàn)場保護以及中斷后必要的設置條件檢測需要時間,,所以軟件必須通過容余指令(比如NOP)的延時,可保證counter0輸出和控制信號延時起點在同一時刻,。

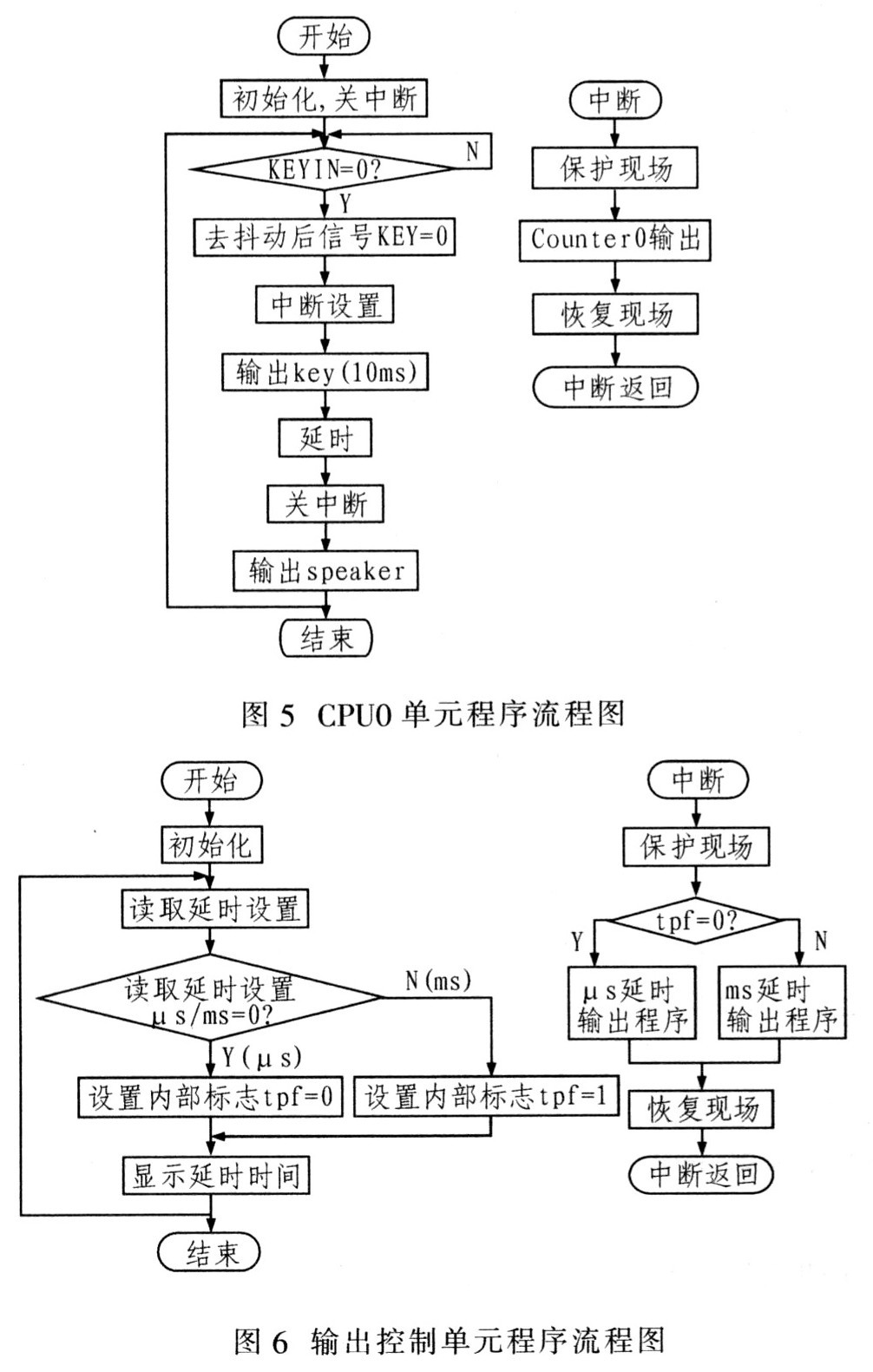

CPU0單元程序流程如圖5所示,。CPU0主程序完成系統(tǒng)初始化、按鍵檢測,、去抖動信號輸出和工作狀態(tài)提示音輸出等工作,,中斷服務程序計時基準信號counterO輸出。輸出控制單元NO.1一NO.n程序流程如圖6所示,,各單元主程序完成μs/ms設置檢測,,延時設置讀取,延時時間顯示,,中斷程序完成控制信號輸出功能,。CPLD程序采用VHDL語言編寫,采用QHalftusⅡ軟件編譯仿真,。

5 結(jié)語

該系統(tǒng)設計可應用于電容組(9只)放電控制系統(tǒng),,在放電電子開關(guān)控制端、