0 引言

在當(dāng)今的數(shù)字信息時(shí)代,人們對(duì)大容量數(shù)據(jù)存儲(chǔ)的需求日趨旺盛。作為非易失性存儲(chǔ)器的NAND Flash,由于其高容量低成本的特點(diǎn),逐漸在實(shí)際產(chǎn)品,比如固態(tài)硬盤、智能手機(jī)、平板電腦等消費(fèi)類電子產(chǎn)品中得到應(yīng)用。

由于其特殊的內(nèi)部結(jié)構(gòu),NAND Flash的操作方式與NOR Flash不太一樣,不支持隨機(jī)字節(jié)訪問,其讀、寫操作均要以頁(yè)面(Page)為單位進(jìn)行,同一頁(yè)面在未擦除前不允許進(jìn)行多次寫操作;而擦除操作必須以塊(Block)為單位進(jìn)行。因此,需要針對(duì)這一特性設(shè)計(jì)專用的控制器來(lái)完成各種操作。

本文根據(jù)這一目的,設(shè)計(jì)了一款NAND Flash控制器。該控制器不僅能夠完成前面提到的基本操作,還能支持ONFI2.1標(biāo)準(zhǔn)中的同步接口模式。使其能夠以200MB/s的速度對(duì)NAND Flash設(shè)備進(jìn)行讀寫操作,遠(yuǎn)遠(yuǎn)快于其他同類NAND Flash控制器。

1 ONFI標(biāo)準(zhǔn)

ONFI(Open NAND Flash Interface,開放式NAND閃存接口)規(guī)范是一種Flash閃存接口的標(biāo)準(zhǔn),它是Intel為統(tǒng)一當(dāng)初混亂的閃存接口所倡導(dǎo)的標(biāo)準(zhǔn)。因?yàn)樵诖酥埃袌?chǎng)上銷售的NAND閃存芯片在引腳定義上都不完全相同。這就使得為一家公司設(shè)計(jì)的控制器,很有可能無(wú)法用在另一家公司的產(chǎn)品上。比如為東芝芯片設(shè)計(jì)的控制器,就無(wú)法用在三星或海力士的產(chǎn)品上,這就給上游的主控設(shè)計(jì)商以及最終的產(chǎn)品設(shè)計(jì)人員帶來(lái)了很大的困難。

為此,Intel聯(lián)合多家NAND Flash廠商制定了ONFI標(biāo)準(zhǔn),統(tǒng)一NAND Flash芯片的引腳定義,并在此基礎(chǔ)上采用新的技術(shù)以實(shí)現(xiàn)新的功能。2006年發(fā)布了ONFI1.O標(biāo)準(zhǔn),使得接口的統(tǒng)一邁出了實(shí)質(zhì)性的一步。但是該版本速度較慢,最高速度只有34MB/s,不具有太大的競(jìng)爭(zhēng)優(yōu)勢(shì)。為了提高速度,ONFI組織在2008年發(fā)布了ONFI2.0,將接口速度提升到了133MB/s。在該版本中,主要是通過(guò)兩項(xiàng)技術(shù)來(lái)提高傳輸速度。第一項(xiàng)就是在DRAM領(lǐng)域里常用的DDR(Double Data Rate,兩倍數(shù)據(jù)率)信號(hào)技術(shù)。第二項(xiàng)是使用源同步時(shí)鐘來(lái)精確控制鎖存信號(hào),使其能夠達(dá)到更高的工作頻率。2009年,ONFI組織又推出了規(guī)格更高的ONFI2.1標(biāo)準(zhǔn),把最高速度提高到了200MB/s。

2 控制器結(jié)構(gòu)

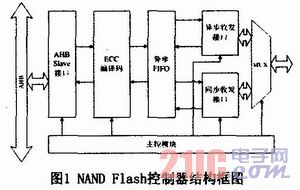

本文設(shè)計(jì)的NAND Flash控制器是SOC芯片的一部分,作為AHB Slave被掛在總線上,接收來(lái)自CPU的讀、寫和擦除等命令。其結(jié)構(gòu)框圖如圖1所示。

其中AHB Slave接口模塊主要是負(fù)責(zé)處理與AHB總線協(xié)議相關(guān)的操作;ECC編譯碼模塊主要是負(fù)責(zé)對(duì)存入NAND Flash中的數(shù)據(jù)進(jìn)行糾錯(cuò)編碼和對(duì)從NAND Flash中讀出的數(shù)據(jù)進(jìn)行糾錯(cuò)碼譯碼的工作;異步FIFO模塊用來(lái)緩存數(shù)據(jù),并承擔(dān)數(shù)據(jù)跨時(shí)鐘域的工作;主控模塊負(fù)責(zé)整個(gè)控制器的控制;異步收發(fā)接口模塊主要負(fù)責(zé)異步模式下的數(shù)據(jù)讀寫;同理,同步收發(fā)接口模塊主要負(fù)責(zé)同步模式下的數(shù)據(jù)讀寫。本文的重點(diǎn)是與ONFI標(biāo)準(zhǔn)相關(guān)的接口設(shè)計(jì),所以AHB Slave與ECC兩個(gè)模塊在此不再介紹,具體請(qǐng)參閱其他相關(guān)文獻(xiàn)。

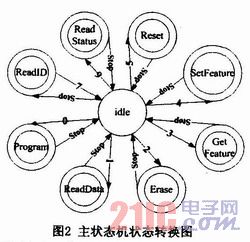

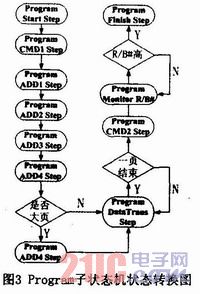

主控模塊是整個(gè)控制器的中心控制模塊,由一個(gè)主狀態(tài)機(jī)和多個(gè)子狀態(tài)機(jī)構(gòu)成。主狀態(tài)機(jī)有1個(gè)空閑狀態(tài)和8個(gè)工作狀態(tài),分別對(duì)應(yīng)著8種具體的操作。其狀態(tài)轉(zhuǎn)換如圖2所示。而每個(gè)工作狀態(tài)又對(duì)應(yīng)1個(gè)子狀態(tài)機(jī),負(fù)責(zé)每個(gè)操作的具體細(xì)節(jié)。由于篇幅所限,本文只列出Program操作的子狀態(tài)機(jī)狀態(tài)轉(zhuǎn)換圖,如圖3所示。其他子狀態(tài)機(jī)的狀態(tài)可以根據(jù)ONFI標(biāo)準(zhǔn)來(lái)確定。

3 同步模式設(shè)計(jì)

3.1 同步接口設(shè)計(jì)

支持ONFI2.0及以上的NAND Flash芯片既支持傳統(tǒng)的異步接口模式,也能通過(guò)配置工作在源同步的DDR接口模式下,從而達(dá)到速度的提高。如圖4所示,在同步工作模式下,增加了DQS信號(hào),并將異步模式下的WE#信號(hào)變?yōu)镃LK信號(hào),RE#變?yōu)閃/R信號(hào)。有很多文獻(xiàn)介紹了傳統(tǒng)異步接口模式下的NAND Flash控制器設(shè)計(jì),本文不再贅述,以下開始介紹同步工作模式下的接口電路設(shè)計(jì)。

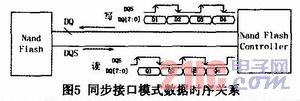

當(dāng)NAND Flash工作于同步接口模式時(shí),接口I/O數(shù)據(jù)為DDR形式,讀寫操作時(shí)序見圖5,可以發(fā)現(xiàn)它非常類似于DDR SDRAM的時(shí)序,其中DQ[7:0]為數(shù)據(jù),DQS為數(shù)據(jù)選通信號(hào),其基本思想就是將兩組持續(xù)時(shí)間為一個(gè)時(shí)鐘周期的數(shù)據(jù)合并,使得在傳輸過(guò)程中一個(gè)時(shí)鐘周期的上升沿和下降沿都能傳輸數(shù)據(jù),從而獲得傳輸速度的倍增。

DQ和DQS均為雙向驅(qū)動(dòng)信號(hào),當(dāng)進(jìn)行寫操作時(shí),由控制器進(jìn)行驅(qū)動(dòng),當(dāng)進(jìn)行讀操作時(shí),由Flash芯片內(nèi)部進(jìn)行驅(qū)動(dòng),本文雙向信號(hào)采用圖6方法實(shí)現(xiàn),該結(jié)構(gòu)需要置于整個(gè)設(shè)計(jì)的頂層,從而利于綜合的進(jìn)行。

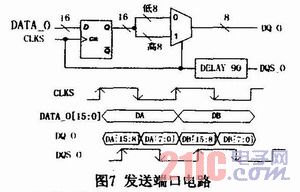

DQ與DQS信號(hào)間的相位關(guān)系對(duì)DDR接口非常重要。當(dāng)對(duì)NAND Flash進(jìn)行寫操作時(shí),控制器必須產(chǎn)生一個(gè)與DQ數(shù)據(jù)信號(hào)中心對(duì)齊的DQS信號(hào),所用發(fā)送端口電路如圖7所示,CLKS為同步接口模式下系統(tǒng)的整體時(shí)鐘。通過(guò)多路選擇器實(shí)現(xiàn)16bit數(shù)據(jù)DATA_O轉(zhuǎn)兩組8bit數(shù)據(jù)DQ_O輸出。CL-KS為高時(shí)對(duì)應(yīng)DATA_O的高8bit數(shù)據(jù),CLKS為低時(shí)對(duì)應(yīng)DATA_O的低8bit數(shù)據(jù),最后將CLKS進(jìn)行移相作為DQS_O選通信號(hào)輸出。

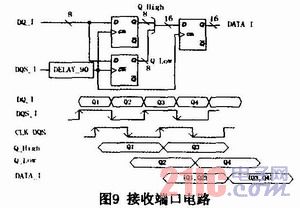

當(dāng)從Flash存儲(chǔ)器件讀取的時(shí)候,F(xiàn)lash輸出的DOS信號(hào)是與DQ信號(hào)邊沿對(duì)齊的,需要對(duì)接收到的DQS信號(hào)進(jìn)行相移使之與DQ信號(hào)中心對(duì)齊,以采到準(zhǔn)確的數(shù)據(jù)。圖8是DQS移相后與DQ中心對(duì)齊的實(shí)際仿真波形圖。所用讀接口結(jié)構(gòu)如圖9所示,首先將DQS_I選通信號(hào)進(jìn)行移相,然后通過(guò)兩組分別為上升沿觸發(fā)和下降沿觸發(fā)的寄存器采樣與DQS_I上升沿和下降沿對(duì)齊的兩組8bit數(shù)據(jù)DQ_I,并通過(guò)一組同樣是上升沿觸發(fā)的寄存器將這兩組8bit數(shù)據(jù)合并成16bit數(shù)據(jù)。

實(shí)現(xiàn)讀寫操作的電路中都使用了DELAY單元,以達(dá)到移相的目的,DELAY單元可以由兩種方法實(shí)現(xiàn):DLL和延遲線。將相移定為90°,是假設(shè)DQ和DQS是理想的源同步接口,并假定DQ和DQS經(jīng)過(guò)芯片內(nèi)部延時(shí)、PCB板上延時(shí)及pin腳延時(shí)是相同的,這樣能得到最理想的數(shù)據(jù)窗口。

3.2 異步時(shí)鐘域處理

很明顯,同步接口模式下的控制器將涉及到較多的異步時(shí)鐘域的通信,需要小心處理。首先,由于本文所設(shè)計(jì)的控制器中所有跨時(shí)鐘域的單比特控制信號(hào)沒有窄脈沖形式,因此均可以使用雙D觸發(fā)同步器作同步,此外涉及跨時(shí)鐘域的數(shù)據(jù)緩沖需要使用異步FIFO。由于ONFI2.1規(guī)定的最快Timing Mode達(dá)到了200MB/s的數(shù)據(jù)速率,而涉及本文應(yīng)用的連接Flash控制器的下一級(jí)模塊消耗數(shù)據(jù)的速率為100MB/s,如果按照公式計(jì)算FIFO的深度,可如式(1)所示,其中的4KB是仿真實(shí)驗(yàn)所使用的仿真模型的頁(yè)面(Page)大小。

4KB×(1-100MB/s÷200MB/s)=2KB (1)

這樣大的FIFO將帶來(lái)較大的硬件代價(jià),考慮到NAND Flash的讀寫操作是可以暫停的,故本文將FIFO深度設(shè)為128,寬度為16bit。

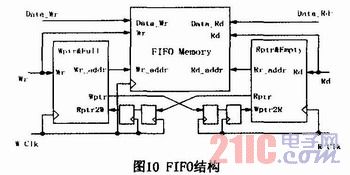

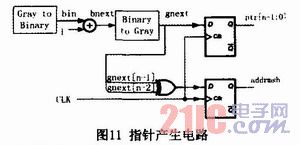

如何判斷異步FIFO的空滿狀態(tài)也是設(shè)計(jì)FIFO的難點(diǎn)。本文所使用的FIFO采用圖10的結(jié)構(gòu),F(xiàn)IFO Memory模塊采用寄存器組作為核心存儲(chǔ),這是由于本文應(yīng)用環(huán)境下可能經(jīng)常出現(xiàn)讀空或?qū)憹M的情況,這樣會(huì)頻繁遇到讀寫同一個(gè)地址,因此不適合用雙端口SRAM作為FIFO的核心存儲(chǔ);Wptr&Full模塊用于產(chǎn)生寫指針和滿標(biāo)志;Rptr&Empty模塊用于產(chǎn)生讀指針和讀標(biāo)志;此外還有兩組同步器分別將寫指針同步到讀時(shí)鐘域和讀指針同步到寫時(shí)鐘域。跨時(shí)鐘傳送的讀寫指針都事先轉(zhuǎn)換成格雷碼,以避免亞穩(wěn)態(tài)問題及提高可靠性。

以下介紹空滿標(biāo)志判斷電路的實(shí)現(xiàn)。空標(biāo)志的條件是讀操作引起的讀寫指針相等,滿標(biāo)志的條件是寫操作引起的讀寫指針相等。本文采用的方法是,構(gòu)造指針寬度為N+1,深度為2N的FIFO,利用多加了一位寬度的指針實(shí)現(xiàn)空滿狀態(tài)的判斷:當(dāng)指針最高位不同而其似位相同時(shí),F(xiàn)IFO為滿;當(dāng)指針完全相同時(shí),F(xiàn)IFO為空。指針及地址產(chǎn)生電路見圖11,給出的地址addr={addrmsb,ptr[n-3:0]},ptr[n-1:0]作為格雷碼指針給出,用于判斷空滿,其中addrmsb由gnext[n-1]^gnext[n-2]產(chǎn)生。

3.3 異步模式切換到同步模式

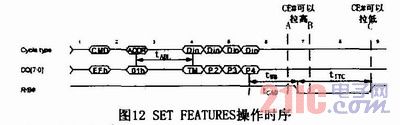

根據(jù)ONFI 2.1規(guī)定,NAND Flash剛上電時(shí)一律處在異步接口模式的Timing Mode 0下工作,需要通過(guò)SETFEATURES操作才能轉(zhuǎn)換到同步接口模式下工作,步驟如下,同時(shí)操作時(shí)序見圖12。

(1)發(fā)出SET FEATURES(EFh)命令;

(2)將地址設(shè)為01h;

(3)向P1寫入1Xh,其中X表示需要設(shè)定的同步接口Timing ModeX;

(4)P2到P3均寫入00h;

(5)此時(shí)R/B#信號(hào)將保持低電平tITC。控制器需要將CE#拉高。在tITC期間,控制器不得向NAND Flash發(fā)出任何命令,包括讀狀態(tài)命令。

(6)當(dāng)tITC結(jié)束后R/B#拉高,同步接口開啟。在CE#使能之前,控制器需要給出CLK。

注意到異步接口轉(zhuǎn)換到同步接口模式下,需要啟動(dòng)NAND Flash所需的CLK,因此本文將SET FEATURES操作拆分成兩部分,以啟動(dòng)CLK為界進(jìn)行分割,兩部分操作中間需產(chǎn)生中斷,并告訴CPU此時(shí)需要啟動(dòng)CLK。同步模式不同Timing Mode之間的切換操作和上述類似,只不過(guò)需要將啟動(dòng)CLK的操作改為轉(zhuǎn)變CLK頻率的操作。

4 仿真與綜合

使用Verilog硬件描述語(yǔ)言對(duì)該控制器進(jìn)行實(shí)現(xiàn)之后,再使用EDA工具仿真和綜合。仿真結(jié)果表明,本文設(shè)計(jì)的控制器的功能和時(shí)序都工作正常。圖13是在同步模式下寫1頁(yè)操作的仿真時(shí)序,圖14是在同步模式下讀1頁(yè)操作的仿真時(shí)序。

使用Synopsys公司的Design Compiler工具對(duì)代碼進(jìn)行綜合,采用SMIC 0.18 μm工藝。得到的數(shù)據(jù)如表1所示。

由綜合結(jié)果可知,最高工作頻率達(dá)到了118MHz,滿足ONFI標(biāo)準(zhǔn)100MHz頻率、200MB/s的最快數(shù)據(jù)傳輸速率的要求,并有超過(guò)15%的裕量。因此,本文設(shè)計(jì)的NANDFlash控制器具有一定的實(shí)用價(jià)值。

5 結(jié)束語(yǔ)

本文設(shè)計(jì)了一種滿足ONFI2.1標(biāo)準(zhǔn)要求的NANDFlash控制器,并通過(guò)了功能仿真和綜合。該控制器既可以在傳統(tǒng)的異步模式下工作,也可以在同步模式下工作,并達(dá)到了ONFI標(biāo)準(zhǔn)要求的200MB/s的數(shù)據(jù)讀寫速率。達(dá)到了最初的設(shè)計(jì)目的,對(duì)其他的NAND Flash控制器設(shè)計(jì)具有參考意義。