很久沒有寫博文了!確實有點過意不去。最近兩個多月以來,由于公司的需要,我不得不學習Cadence16.2的使用方法——用它來畫高速板子。目前白天又在忙著一塊以FBGA484為核心芯片的6層板,因此只好晚上利用一些時間來寫博文了。

筆者寫這篇博文的初衷:一是小小地總結(jié)一下我在這兩個月以來使用Cadence16.2的過程中所遇到的一些問題,并給出解決方法;二是想選幾個問題,把它們寫成文章,和網(wǎng)友分享一下,希望能給將要或者正在學習Cadence的網(wǎng)友提供一些好的幫助信息,少走一些彎路。

事先注明筆者所使用的子軟件分別是:

(1)原理圖設計軟件:OrCAD Capture CIS;

(2)PCB設計軟件" title="PCB設計軟件" target="_blank">PCB設計軟件:Allegro PCB Design GXL;

(3)Pad制作:Pad Designer;

TROUBLE ONE:從何入手?

SOLUTION:如果真想學Cadence的話,該從何入手呢?我在這里推薦一個很好的網(wǎng)站:http://www.sig007.com/,筆者從這個網(wǎng)站中得到了很多益處。只不過需要提醒的是:這個網(wǎng)站里講的東西全都是針對Cadence15.7而言的,So,需要注意這兩個版本之間的差異。還有就是可以逛逛Cadence的官方網(wǎng)站:http://www.cadence.com/us/pages/default.aspx,有時間可以去欣賞一下里面的那些Blogs,絕對稱得上是:Short and to the point!

TROUBLE TWO:自建分裂元件Capture封裝時該如何區(qū)分Homogeneous和Heterogeneous?

SOLUTION:剛開始接觸這個軟件時,筆者也是為此分不清,后來在做實際項目的過程中,終于能夠加以區(qū)分并運用了。

創(chuàng)建分裂元件時,會出現(xiàn)如下對話框:

想必初學者遇到這兩個英文單詞時最初的“本能反應”就是努力想起或者去查詢它們的中文意思。用字典軟件翻譯之后,可以看到它們都有若干個幾個近似的意思。筆者作為“過來人”(呵呵,JK),覺得初學者完全不需要理會這些近似的意思——因為它們根本沒有透露出最關鍵的信息。筆者覺得可以用一種更直白的方式來理解它們,

(1)Homogeneous:前綴Homo-在英語里有“同”的意思,由此可以說明這種分裂元件里的所有PART都是一摸一樣的!當然除了一個參數(shù)是不同的,即

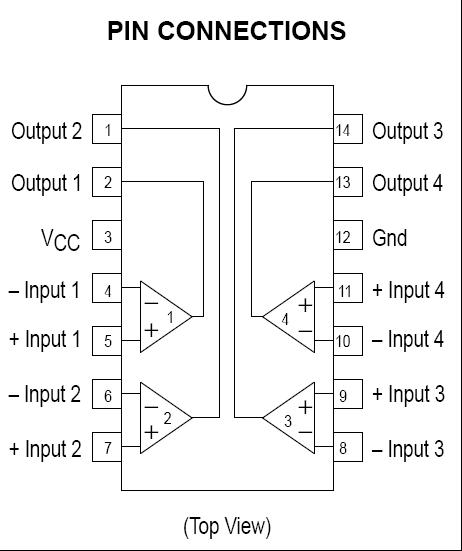

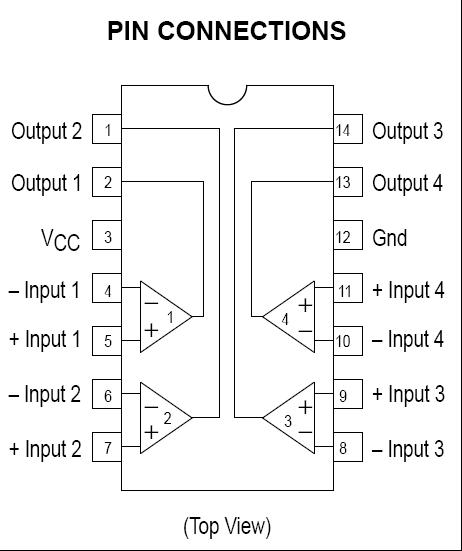

舉個例子(LM339芯片):

這個比較器的芯片內(nèi)部有4個完全一樣的放大器,所以制作像LM339這樣的元件Capture封裝時,應選擇Homogeneous。

(2)Heterogeneous:前綴Hetero-在英語里有“異”的意思,由此可以說明這種分裂元件里的各個PART是有區(qū)別的。其實這種TYPE更為常用,因為現(xiàn)實情況下內(nèi)部都是相同PART的IC并不那么常見,

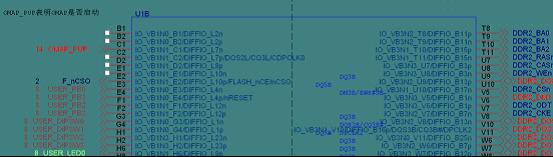

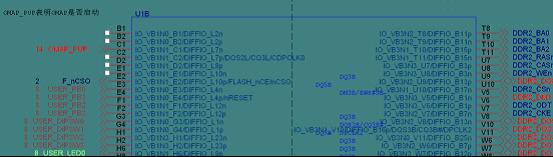

舉個例子(EP3C40F484芯片),

PART B:

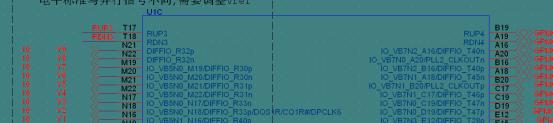

PART C:

筆者覺得如果要很好地區(qū)分這兩種PACKAGE TYPE,最好還是親力親為一遍或多遍,這樣印象更深刻。

很久沒有寫博文了!確實有點過意不去。最近兩個多月以來,由于公司的需要,我不得不學習Cadence16.2的使用方法——用它來畫高速板子。目前白天又在忙著一塊以FBGA484為核心芯片的6層板,因此只好晚上利用一些時間來寫博文了。

筆者寫這篇博文的初衷:一是小小地總結(jié)一下我在這兩個月以來使用Cadence16.2的過程中所遇到的一些問題,并給出解決方法;二是想選幾個問題,把它們寫成文章,和網(wǎng)友分享一下,希望能給將要或者正在學習Cadence的網(wǎng)友提供一些好的幫助信息,少走一些彎路。

事先注明筆者所使用的子軟件分別是:

(1)原理圖設計軟件:OrCAD Capture CIS;

(2)PCB設計軟件:Allegro PCB Design GXL;

(3)Pad制作:Pad Designer;

TROUBLE ONE:從何入手?

SOLUTION:如果真想學Cadence的話,該從何入手呢?我在這里推薦一個很好的網(wǎng)站:http://www.sig007.com/,筆者從這個網(wǎng)站中得到了很多益處。只不過需要提醒的是:這個網(wǎng)站里講的東西全都是針對Cadence15.7而言的,So,需要注意這兩個版本之間的差異。還有就是可以逛逛Cadence的官方網(wǎng)站:http://www.cadence.com/us/pages/default.aspx,有時間可以去欣賞一下里面的那些Blogs,絕對稱得上是:Short and to the point!

TROUBLE TWO:自建分裂元件Capture封裝時該如何區(qū)分Homogeneous和Heterogeneous?

SOLUTION:剛開始接觸這個軟件時,筆者也是為此分不清,后來在做實際項目的過程中,終于能夠加以區(qū)分并運用了。

創(chuàng)建分裂元件時,會出現(xiàn)如下對話框:

想必初學者遇到這兩個英文單詞時最初的“本能反應”就是努力想起或者去查詢它們的中文意思。用字典軟件翻譯之后,可以看到它們都有若干個幾個近似的意思。筆者作為“過來人”(呵呵,JK),覺得初學者完全不需要理會這些近似的意思——因為它們根本沒有透露出最關鍵的信息。筆者覺得可以用一種更直白的方式來理解它們,

(1)Homogeneous:前綴Homo-在英語里有“同”的意思,由此可以說明這種分裂元件里的所有PART都是一摸一樣的!當然除了一個參數(shù)是不同的,即

舉個例子(LM339芯片):

這個比較器的芯片內(nèi)部有4個完全一樣的放大器,所以制作像LM339這樣的元件Capture封裝時,應選擇Homogeneous。

(2)Heterogeneous:前綴Hetero-在英語里有“異”的意思,由此可以說明這種分裂元件里的各個PART是有區(qū)別的。其實這種TYPE更為常用,因為現(xiàn)實情況下內(nèi)部都是相同PART的IC并不那么常見,

舉個例子(EP3C40F484芯片),

PART B:

PART C:

筆者覺得如果要很好地區(qū)分這兩種PACKAGE TYPE,最好還是親力親為一遍或多遍,這樣印象更深刻。

TROUBLE THREE:倘若原理圖結(jié)構(gòu)非常大,如何更加有效率地添加元件的Footprint信息?

SOLUTION:在這種情況下,如果一個一個地給元件添加Footprint信息,那將是非常耗費時間的。筆者發(fā)現(xiàn)了一個操作方法,可以大幅提高工作效率。

方法如下:在OrCAD Capture CIS的File界面下,

鼠標單擊DSN文件或者相應的PAGE文件,并且鼠標右擊,選中其中的Edit Object Properties選項,出現(xiàn)如下對話框:

可以看見里面有一列“PCB Footprint”,這樣就可以成批量的添加元件的Footprint信息了。

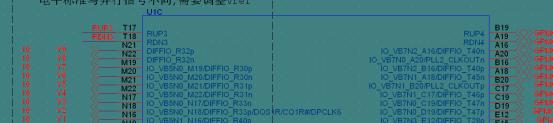

SOLUTION:有些情況下,我們在布局、布線的時候可能會遇到有的Pin Header中的PIN引腳是可以任意順序的,但是在布線時我們所看到的大都是非常雜亂無章的飛線,為此,筆者可以提供一個好的方法來解決這個問題:先在OrCAD Capture CIS里修改Netlist,然后再導入Allegro。However,需要注意的是,只能在原理圖中改變Pin Header中PIN的順序,千萬別改變與之相連的芯片的引腳序號(當然還是有特殊情況的)!這個應該不難理解,就不多說了。

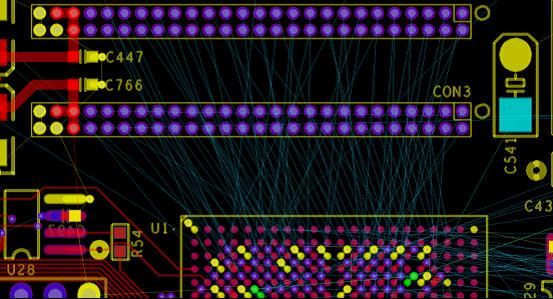

舉個例子:一個六層板最初導入Netlist后的局部飛線情況如下,

但是在修改了Netlist之后,結(jié)果發(fā)現(xiàn)布線非常簡潔,同時也有效地減少了板子過孔的數(shù)量,如下圖所示,

其次還有一種方法,那就是Highlight和Dehighlight的使用方法,在布局、布線時可以人為特意將某些相同的Net高亮顯示,這樣可以對整個布局達到一目了然的效果。

TROUBLE FIVE:由于Allegro自帶的元件PACKAGE比較少,遠遠不能滿足實際項目的需求。這么多的元件PACKAGE需要畫,而且相當花費時間,有沒有更好的辦法來解決這個問題呢?

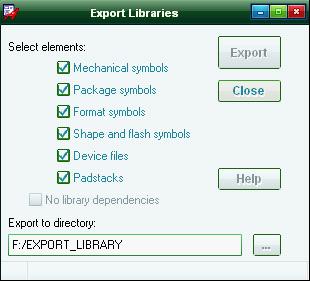

SOLUTION:方法是有的,現(xiàn)給出具體步驟,

首先,打開一個BRD文件,在Allegro界面環(huán)境下,點擊File,選擇Export,在下拉列表中,再選擇Libraries,出現(xiàn)如下對話框,

然后設置導出封裝庫的路徑,最后,點擊Export就Okay了,接下來就可以免費享用別人畫的PACKAGE了。“更狠”的做法就是:到一些大公司(比如ALTERA)的網(wǎng)站上去下載那些十幾甚至幾十層的REFERENCE BOARD的BRD文件,然后再EXPORT其中的封裝信息,到那時,您將擁有享用不盡的元器件封裝了!哈哈~~有點夸張。

TROUBLE SIX:Generating Artwork時,能不能簡化其步驟?

SOLUTION:之前在做一個板子,投出去后,PCB生產(chǎn)廠家反饋回一個問題,說是導出的ARTWORK文件有點小問題——有些元器件的VALUE值沒有顯示出來,如下圖所示,

收到這個問題后筆者立即著手解決。后來發(fā)現(xiàn)了一個非常簡便的方法,筆者自己也是對此意想不到,無意中發(fā)現(xiàn)的,呵呵。具體步驟如下:

在Allegro界面環(huán)境下,鼠標點擊Add,選擇其中的Text選項,Then,把Class和Subclass分別設置為Component Value和Assembly_Top(或者Assembly_Bottom),再點擊所要添加VALUE值的相應Symbol,輸入具體值就完事了。

其實這種方法可以有多方面的應用場合,尤其是ARTWORK文件生成。也許還有別的SOLUTION,但是按這種方法修改ARTWORK信息的話,應該是最簡便的了。

小結(jié):在使用Cadence16.2畫板子的過程中確實遇到了比較多的問題,大部分的問題筆者都已經(jīng)有效地解決了。由于文章篇幅所限,很多基礎性的東西都沒做涉及,只是針對軟件的使用方法選取了其中6個離散的問題作了闡述,并沒有涉及EMC相關的問題。今后有時間筆者將再針對PCB板級設計以及EMC方面的東西,寫成博文和網(wǎng)友分享。