引言

SPI總線作為一種簡單高效的4線串行傳輸總線,在電子器件和系統(tǒng)中應(yīng)用非常普遍,由于其輸入和輸出的信號線彼此獨立,因而傳輸可靠性更好。Altera公司的EDA設(shè)計工具中有自帶的SPI總線控制IP核,但目前介紹該IP核具體應(yīng)用的文獻不多,本文結(jié)合我們在微投影系統(tǒng)研究中的需求,給出了該SPI IP核的應(yīng)用實例。

1 SPI核的工作原理

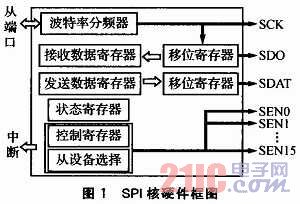

1.1 硬件結(jié)構(gòu)

SPI核的硬件結(jié)構(gòu)如圖1所示,主要由波特率分頻器、發(fā)送數(shù)據(jù)寄存器、接收數(shù)據(jù)寄存器、狀態(tài)寄存器和控制寄存器組成。波特率分頻器主要將Avalon的系統(tǒng)時鐘進行分頻,SCK可以配置的頻率=Avalon系統(tǒng)時鐘頻率/(2的倍數(shù))。

該IP核可以配置為主和從兩種模式。本設(shè)計為嵌入在FPGA中SPI核為主工作模式,可以控制最多16個從設(shè)備,如圖1所示的SEN0~SENl5。只有一個器件時,默認(rèn)為SEN0信號。SPI核傳輸?shù)臄?shù)據(jù)寬度是由用戶配置的,可在1~32位之間,當(dāng)一次數(shù)據(jù)傳輸結(jié)束之后SPI核發(fā)出一個中斷請求。

主要實現(xiàn)兩種傳輸邏輯(以主模式為例):

①發(fā)送邏輯。待發(fā)送的數(shù)據(jù)由Avalon從端口送入發(fā)送數(shù)據(jù)寄存器,再移入移位寄存器中,SCK跳變沿到來時開始數(shù)據(jù)傳輸(經(jīng)SDAT信號線發(fā)出,先移入的數(shù)據(jù)是高位還是低位,取決于SOPC Builder的配置)。

②接收邏輯。移位寄存器捕獲到完整的數(shù)據(jù)后,再將其移入接收數(shù)據(jù)寄存器中(由SDO信號線捕獲數(shù)據(jù))。

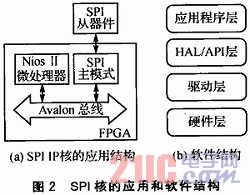

1.2 軟件結(jié)構(gòu)

目前,在采用32位的軟核Nios II處理器中,提供了4層軟件開發(fā)模式:Nios II系統(tǒng)硬件,驅(qū)動程序?qū)樱布橄髮討?yīng)用程序接口(HAL API),應(yīng)用程序?qū)印PI核的應(yīng)用和軟件結(jié)構(gòu)如圖2所示。

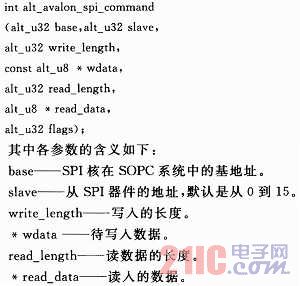

2 SPI核的庫函數(shù)及其使用

該IP核的APl函數(shù)為alt_avalon_spi_command(),其原型為:

flags——置1時表示執(zhí)行完該函數(shù)后,SS_N保持寫/讀操作相同的電平;置0時表示執(zhí)行完該函數(shù)后,SS_N為寫/讀操作相反的電平。

alt u8、alt u32分別是Altera系統(tǒng)中定義的8位、32位無符號數(shù)。

3 應(yīng)用實例

微投影技術(shù)顯示是目前投影的一個研究焦點,主流的技術(shù)包括:MOEMS微光機電微鏡偏轉(zhuǎn)技術(shù)、基于數(shù)字微鏡芯片的DLP技術(shù)和基于硅基液晶的LCOS技術(shù)。三種技術(shù)相比,LCOS具有成本低、體積小、低功耗等優(yōu)點。

本設(shè)計使用的是鎂光公司的MT7DPWV2F鐵電硅基液晶(FLCOS),F(xiàn)LCOS比一般的LCOS在色彩對比度、液晶像素響應(yīng)時間方面更為出色。該芯片的主要參數(shù):像素分辨率為852×480,顏色深度24位,對比度300:1,光學(xué)鏡面反射率63%,尺寸23.4mm×9.8 mm×3.6 mm,功耗僅為75 mW。

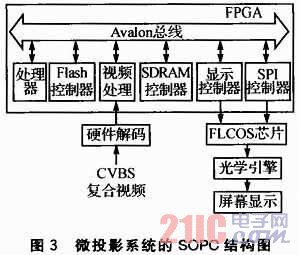

圖3為微投影系統(tǒng)視頻處理與控制SOPC系統(tǒng)示意圖,總線上掛接了包括微處理器、Flash控制器、SDRAM控制器等。復(fù)合視頻信號經(jīng)過硬件解碼后進入視頻處理模塊(完成去隔行處理、色空間轉(zhuǎn)換等功能),SPI控制器模塊和顯示控制器模塊一起控制片外的FLCOS芯片。FLCOS產(chǎn)生的圖像經(jīng)過光學(xué)引擎放大,投影到屏幕上面來。

該FLCOS芯片有數(shù)十個可配置的內(nèi)部寄存器,根據(jù)具體應(yīng)用的需求,有4個寄存器是必須初始化配置的。

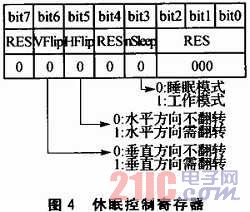

①休眠控制寄存器(地址為0x06)。如圖4所示,該寄存器默認(rèn)值為00H,需要將bit3位改為1,芯片才能從睡眠模式進入工作模式。

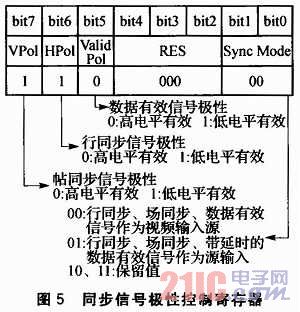

②同步信號極性控制寄存器(地址為0x02)。如圖5所示,該寄存器默認(rèn)值為C0h,將其bit7、bit6兩位改為0,以符合顯示時序控制器同步信號高電平有效的時序要求。

③LED輸出控制寄存器(地址為0x05)。如圖6所示,該寄存器默認(rèn)值為09h,需要將bit5、bit6改為1,從而芯片能發(fā)出高電平有效的LED驅(qū)動信號,bit3到bit0默認(rèn)為9h表示圖像的伽馬值為2.1。

④像素時鐘控制寄存器(地址為0x0f)。如圖7所示,默認(rèn)值為40h,該寄存器需要配置為像素時鐘大小的2倍。由于本設(shè)計使用的像素時鐘為27 MHz,27×2=54,轉(zhuǎn)為十六進制數(shù)即為36h。

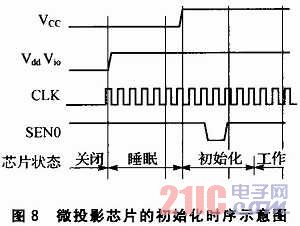

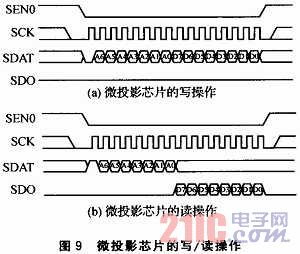

FLCOS芯片的初始化過程如圖8所示。上電后,芯片進入睡眠狀態(tài),就需要對芯片進行SPI初始化配置,即對微投影寄存器進行寫操作,其時序如圖9所示。讀操作時要求器件地址(共8位)的最高位為1,寫操作時要求器件地址(共8位)的最高位為0。

作為SPI驗證的例子,先向微投影芯片地址為0x06的存儲單元寫入數(shù)據(jù)0x08后再從中讀出,并通過QuartusII內(nèi)嵌的SignalTap II邏輯分析工具捕獲如下信號,依次為SPI片選信號SEN0、時鐘信號SCK和數(shù)據(jù)信號SDAT、SD0。結(jié)果顯示,所得到的這一寫入、讀出過程時序與圖9要求的芯片寫入、讀出時序一致。

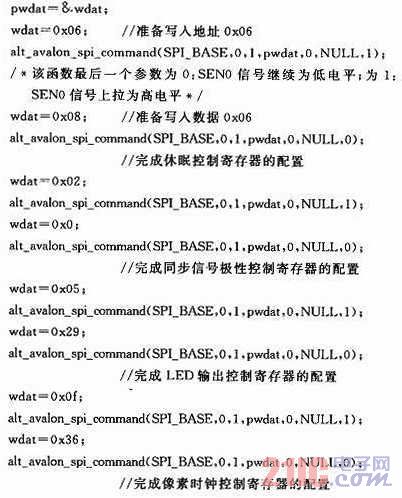

芯片的初始化代碼如下:

![]()

結(jié)語

SPI IP核作為自定義組件加載到SOPC系統(tǒng)中,應(yīng)用于微投影芯片上并實現(xiàn)其初始化。SPI接口十分廣泛,本文通過微投影的實例著重闡述了如何配置芯片的寄存器,實驗表明該IP核配置靈活,便于移植。