I2C總線是兩線式串行總線,用于連接微控制器及其外圍設(shè)備。該總線具有如下特點(diǎn):1)只要求兩條總線線路,一條串行數(shù)據(jù)線(SDA),一條串行時(shí)鐘線(SDL);2)每個(gè)連接到總線的器件都可以通過唯一的地址尋址,總線中主機(jī)可以作為主機(jī)發(fā)送器或主機(jī)接收器;3)它是一個(gè)真正的多主機(jī)總線,如果兩個(gè)或更多主機(jī)同時(shí)初始化數(shù)據(jù)傳輸可以通過沖突檢測(cè)和仲裁防止數(shù)據(jù)被破壞;4)雙向數(shù)據(jù)傳輸位速率在標(biāo)準(zhǔn)模式下可達(dá)100 kbit/s快速模式下可達(dá)400kbit/s高速模式下可達(dá)3.4 Mbit/s;5)片上的濾波器可以濾去總線數(shù)據(jù)線上的毛刺以保證數(shù)據(jù)完整;6)連接到相同總線的IC數(shù)量只受到總線的最大電容400 pF限制。I2C總線最主要的優(yōu)點(diǎn)是其簡單性和有效性。由于I2C總線為兩線式總線,它占用的空間非常小,減少了電路板的空間和芯片管腳的數(shù)量,降低了互聯(lián)成本。它支持多主控制(multimastering),總線中任何能夠進(jìn)行發(fā)送和接收的設(shè)備都可以成為主機(jī)。任何主機(jī)都能夠控制總線信號(hào)的傳輸和時(shí)鐘頻率。在任何時(shí)間點(diǎn)上只能有一個(gè)器件作為主機(jī),其他器件作為從機(jī)。正是由于I2C總線具有上述諸多優(yōu)點(diǎn),具備I2C接口的器件在儀器設(shè)計(jì)中已被廣泛采用,比較常見的如:日歷芯片、存儲(chǔ)芯片、模數(shù)轉(zhuǎn)換器以及數(shù)模轉(zhuǎn)換器等。

不幸的是大多數(shù)CPU都擅長操作并口,而并不具備直接操作I2C總線接口的能力。在系統(tǒng)設(shè)計(jì)時(shí),為了與具有I2C總線接口的芯片連接,經(jīng)常采用的方法是:利用CPU的2條通用輸入輸出(GPIO)線作為I2C總線使用,用軟件模擬的方法,產(chǎn)生I2C總線需要的控制時(shí)序。該方法雖然可以達(dá)到同I2C器件連接的目的,卻不可避免地帶來軟件編制復(fù)雜、占用CPU處理時(shí)間多的弊端。為了在不增加編程難度、不大量占用CPU處理時(shí)間的前提下使不具備I2C總線的CPU也能夠充分享受I2C總線的優(yōu)點(diǎn),本文設(shè)計(jì)了一種基于CPLD的8位并行接口轉(zhuǎn)I2C總線接口的控制模塊,通過該模塊,具有并口的CPU可以通過對(duì)并口的讀寫完成對(duì)I2C總線的控制。

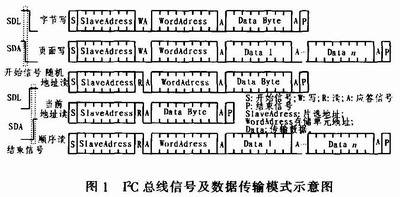

1 I2C總線的基本時(shí)序

I2C總線是由數(shù)據(jù)線SDA和時(shí)鐘線SCL構(gòu)成,靠它們?cè)谶B接于I2C總線的各個(gè)設(shè)備之間傳送信息。I2C總線在傳送數(shù)據(jù)過程中共有4種類型的信號(hào),分別是:開始信號(hào)、結(jié)束信號(hào)、應(yīng)答信號(hào)和數(shù)據(jù)傳輸信號(hào)。

開始信號(hào):主機(jī)控制SDA信號(hào)線在SCL線的高電平期間發(fā)生由高電平到低電平的跳變,通知從機(jī)開始數(shù)據(jù)傳輸。

結(jié)束信號(hào):主機(jī)控制SDA信號(hào)線在SCL線的高電平期間發(fā)生由低電平到高電平的跳變,通知從機(jī)本次數(shù)據(jù)傳輸結(jié)束。

應(yīng)答信號(hào):接收數(shù)據(jù)的芯片(主機(jī)或者從機(jī))在完整接收到8位數(shù)據(jù)后,向發(fā)送數(shù)據(jù)的芯片發(fā)出低電平信號(hào),通知發(fā)送的數(shù)據(jù)已被接收。發(fā)送數(shù)據(jù)的芯片應(yīng)根據(jù)應(yīng)答信號(hào)的電平高低判斷數(shù)據(jù)是否被接收芯片接收。

數(shù)據(jù)傳輸信號(hào):發(fā)送數(shù)據(jù)的芯片在SCL脈沖控制下在SDA上串行輸出數(shù)據(jù)信號(hào),SDA只能在SCL為低電平期間改變狀態(tài),在SCL為高電平期間應(yīng)保持穩(wěn)定。

I2C總線上的數(shù)據(jù)傳輸主要有4種模式,分別是:字節(jié)寫、頁面寫、當(dāng)前地址讀、隨機(jī)地址讀和順序讀。

字節(jié)寫:對(duì)給定的芯片的確定地址單元寫入一個(gè)字節(jié)的數(shù)據(jù)。

頁面寫:對(duì)給定的芯片的確定地址單元所在頁面連續(xù)寫入全部的數(shù)據(jù)。

當(dāng)前地址讀:讀出當(dāng)前地址單元中的一個(gè)字節(jié)數(shù)據(jù)。

隨機(jī)地址讀:從給定的芯片的確定地址單元中讀出一個(gè)字節(jié)數(shù)據(jù)。

順序讀:從給定的地址后連續(xù)讀出n個(gè)字節(jié)的數(shù)據(jù)。

I2C總線各種信號(hào)及數(shù)據(jù)傳輸模式示意圖如圖1所示。

利用CPLD設(shè)計(jì)一種模塊,如果能夠?qū)PU發(fā)出的并行數(shù)據(jù)按上述I2C總線數(shù)據(jù)傳輸模式自動(dòng)轉(zhuǎn)換成串行數(shù)據(jù)輸出,同時(shí)將接收到的I2C總線串行數(shù)據(jù)自動(dòng)轉(zhuǎn)換成并行數(shù)據(jù)供CPU讀取,則不具備I2C總線接口的CPU也能通過對(duì)并口的操作輕松實(shí)現(xiàn)與I2C總線連接并同其他具備I2C總線接口的芯片交換數(shù)據(jù)。為此本文設(shè)計(jì)了一種基于CPLD的工作于I2C總線主機(jī)模式的并口轉(zhuǎn)I2C總線模塊。利用該模塊CPU可以很容易地實(shí)現(xiàn)與I2C總線的接口。

2 I2C總線接口模塊的CPLD實(shí)現(xiàn)

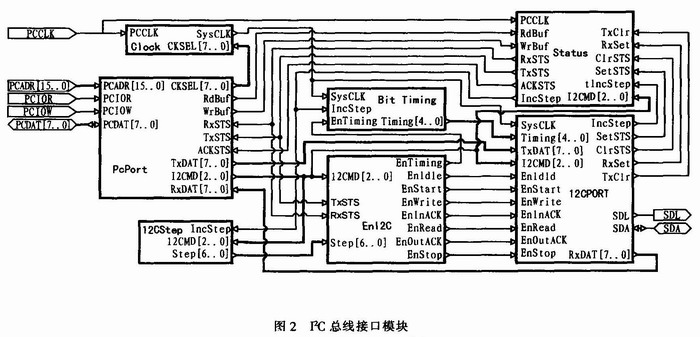

上面簡要介紹了I2C總線的信號(hào)以及I2C總線的數(shù)據(jù)傳輸模式,如果要使接口模塊正常工作,CPU必須首先要通知模塊執(zhí)行什么操作,而后再把需要的數(shù)據(jù)依次送入模塊中,考慮到I2C總線的速率可以在0~3.4 Mbit/s之間,為了適應(yīng)不同外設(shè)的需要,模塊還應(yīng)在CPU的控制下自由調(diào)整數(shù)據(jù)傳送速率。因此,CPU應(yīng)能夠向模塊發(fā)送數(shù)據(jù)傳送速率控制數(shù)據(jù)、I2C總線工作模式控制數(shù)據(jù)、信息交換數(shù)據(jù),同時(shí)還能從模塊

中讀取工作狀態(tài)數(shù)據(jù)、模塊接收數(shù)據(jù)。據(jù)此設(shè)計(jì)出基于CPLD的I2C總線接口模塊如圖2所示。

該設(shè)計(jì)由7個(gè)單元組成,它們分別是:用于調(diào)整I2C總線數(shù)據(jù)傳輸速率的Clock單元;用于實(shí)現(xiàn)同CPU并行接口的PcPort單元:用于產(chǎn)生I2C總線工作時(shí)序的I2CStep單元;用于產(chǎn)生數(shù)據(jù)傳輸時(shí)序的BitTiming單元;用于產(chǎn)生I2C總線使能信號(hào)的En12C單元:用于產(chǎn)生I2C總線接口模塊工作狀態(tài)指示的Status單元:以及用于產(chǎn)生I2C接口時(shí)鐘信號(hào)SDL和數(shù)據(jù)串行輸入輸出信號(hào)SDA的I2CPORT單元。

2.1 Clock單元

整個(gè)接口模塊以CPU的系統(tǒng)時(shí)鐘作為主時(shí)鐘信號(hào),模塊傳輸數(shù)據(jù)的速率受該時(shí)鐘頻率的控制,時(shí)鐘頻率高則模塊傳輸數(shù)據(jù)的速率也高,反之亦然。考慮到各種具有I2C總線接口的芯片的工作速率差別較大(從幾十kB/s到幾MB/s),該接口模塊的工作速率必須能夠靈活調(diào)整,以適應(yīng)不同外設(shè)芯片的接口需要。

Clock單元實(shí)際上就是一個(gè)分頻器,它在輸出頻率控制碼CKSEL[7..0]的控制下產(chǎn)生對(duì)PCCLK分頻后合適的時(shí)鐘信號(hào)供I2C接口使用。

2.2 I2CStep單元

通過對(duì)圖1中I2C總線各種工作模式的分析,可知不同的工作模式都是按特定的工作流程串行輸入、輸出數(shù)據(jù)的,例如字節(jié)寫模式的工作流程為:發(fā)送開始信號(hào)、串行輸出被叫芯片的片選地址、發(fā)送寫信號(hào)、等待被叫芯片響應(yīng)、串行輸出被叫芯片存儲(chǔ)單元的地址、等待被叫芯片響應(yīng)、串行輸出寫入的數(shù)據(jù)、等待被叫芯片響應(yīng)、發(fā)送結(jié)束信號(hào)結(jié)束本次操作。

為了使接口模塊正確工作,模塊在接收到來自CPU的工作模式控制信號(hào)I2CMD[2..0]后,根據(jù)工作模式的不同產(chǎn)生接口模塊工作流程。當(dāng)前流程結(jié)束后由Status單元產(chǎn)生IncStep信號(hào),控制工作流程指向下一階段。該模塊的功能類似一個(gè)計(jì)數(shù)器,它在I2CMD[2..0]和I2CStep的共同作用下,產(chǎn)生長度不等的工作流程信號(hào)Step[6..0]。

2.3 BitTiming單元

在I2C總線工作流程的不同階段,I2C接口模塊需要按一定的時(shí)序完成不同的工作,通過對(duì)總線數(shù)據(jù)傳輸模式的分析可知,在一個(gè)數(shù)據(jù)傳輸模式的所有工作流程中,輸入、輸出8位數(shù)據(jù)的工作流程用時(shí)最長,需要25個(gè)工作時(shí)序周期,為了滿足所有工作流程的需要,工作時(shí)序Bit-Timing單元被設(shè)計(jì)成最長可產(chǎn)生31個(gè)時(shí)鐘周期的工作時(shí)序。

該單元在IncStep=‘1’時(shí)復(fù)位工作時(shí)序;在EnTiming信號(hào)有效后的每個(gè)SysCLK的上升沿使工作時(shí)序信號(hào)EnTiming加1,用于控制I2CPORT單元按給定的時(shí)序串行輸入、輸出數(shù)據(jù)信息。

2.4 Status單元

在I2C總線工作過程中,CPU需要隨時(shí)了解I2C接口模塊的發(fā)送數(shù)據(jù)寄存器是否為空、接收數(shù)據(jù)寄存器是否準(zhǔn)備數(shù)據(jù)好、從機(jī)響應(yīng)信號(hào)是否正確、當(dāng)前工作流程是否完成等工作狀態(tài),只有在發(fā)送數(shù)據(jù)寄存器為空時(shí),CPU才可以向接口模塊寫入待傳輸數(shù)據(jù);只有在接收數(shù)據(jù)寄存器數(shù)據(jù)準(zhǔn)備好后,CPU才可以從接口模塊讀入正確的接收數(shù)據(jù);從機(jī)響應(yīng)信號(hào)不正確時(shí),CPU應(yīng)立即發(fā)出結(jié)束信號(hào)結(jié)束本次操作;當(dāng)前工作流程未完成前不能進(jìn)行下一流程。這些狀態(tài)信號(hào)全部由Status單元產(chǎn)生。

在該單元中,共有4種輸出信號(hào),它們分別是:用于指示發(fā)送數(shù)據(jù)寄存器是否為空的TxSTS狀態(tài),該狀態(tài)在CPU寫入數(shù)據(jù)后置‘1’,數(shù)據(jù)被發(fā)送后清‘0’;用于指示接收數(shù)據(jù)準(zhǔn)備好狀態(tài)的RxSTS信號(hào),該信號(hào)在模塊接收到完整的數(shù)據(jù)后置‘1’,數(shù)據(jù)被CPU讀走后清‘0’;用于指示模塊工作狀態(tài)的ACKSTS信號(hào),該信號(hào)在模塊工作正常(接收到從機(jī)響應(yīng)信號(hào))時(shí)自動(dòng)置‘1’,工作不正常時(shí)自動(dòng)清‘0’;用于使工作流程指向下一階段的IncStep信號(hào),該信號(hào)在當(dāng)前工作流程完成后由模塊自動(dòng)產(chǎn)生,用于使模塊的工作流程指向下一階段。

2.5 EnI2C單元

在I2C總線接口模塊中,BitTiming單元何時(shí)開始產(chǎn)生工作時(shí)序,需要時(shí)序信號(hào)控制,I2CPORT單元何時(shí)向I2C總線輸出信息、何時(shí)從I2C總線上讀入信息也需要時(shí)序信號(hào)控制。這些控制時(shí)序的產(chǎn)生由EnI2C單元完成。

EnI2C單元在I2CMD[2..0]、Step[6..0]、TxSTS、RxSTS等信號(hào)的控制下,從預(yù)先存儲(chǔ)于單元內(nèi)部的一組I2C工作時(shí)序信息中讀出當(dāng)前的時(shí)序信息輸出,控制BitTiming和I2CPORT單元工作。

模塊中,預(yù)先存儲(chǔ)的I2C工作時(shí)序信息實(shí)現(xiàn)如下:

![]()

2.6 12CPORT單元

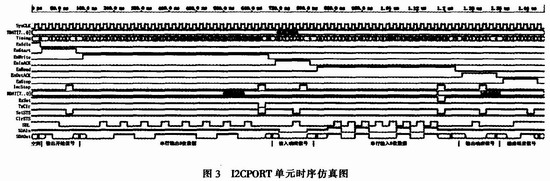

本單元是整個(gè)設(shè)計(jì)的核心,用于完成數(shù)據(jù)的I2C總線輸出以及I2C總線輸入數(shù)據(jù)的讀入。同時(shí)產(chǎn)生接口模塊的各種工作狀態(tài)。

該單元的工作過程為:在SysCLK的下降沿分別讀入工作使能信號(hào)和工作時(shí)序信號(hào),如果此時(shí)EnIdle=‘1’則強(qiáng)制I2C總線進(jìn)入空閑模式;如果EnStart=‘1’,則使I2C總線輸出開始信號(hào);如果EnWrite=‘1’,則使I2C總線輸出8位數(shù)據(jù)信號(hào);如果EnInACK=‘1’,則從I2C總線讀入從機(jī)響應(yīng)信號(hào);如果EnRead=‘1’,則從I2C總線讀入8位數(shù)據(jù);如果EnOutACK=‘1’。則使I2C總線輸出主機(jī)響應(yīng)信號(hào);如果EnStop=‘1’,則使I2C總線輸出結(jié)束信號(hào);在整個(gè)工作過程中,模塊會(huì)自動(dòng)根據(jù)工作情況,設(shè)置各種狀態(tài)控制信號(hào)。

圖3是用QuartusII9.0對(duì)該單元仿真的時(shí)序圖。

2.7 PcPort單元的實(shí)現(xiàn)

該單元是模塊與CPU的接口,CPU通過該單元向接口模塊寫入工作模式控制信息、需要發(fā)送的數(shù)據(jù)以及I2C工作速度控制信息;同時(shí)通過該單元讀入從機(jī)響應(yīng)信息、從機(jī)輸出數(shù)據(jù)、發(fā)送接收寄存器狀態(tài)等信息。

3 應(yīng)用實(shí)例

該模塊工作于主模式,主要應(yīng)用于沒有I2C專用接口的CPU通過并口方便地與具有I2C接口的外設(shè)連接并交換信息。

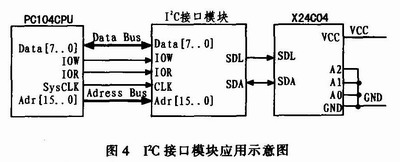

圖4給出了CPU通過該模塊與X24C04E2PROM接口的例子。

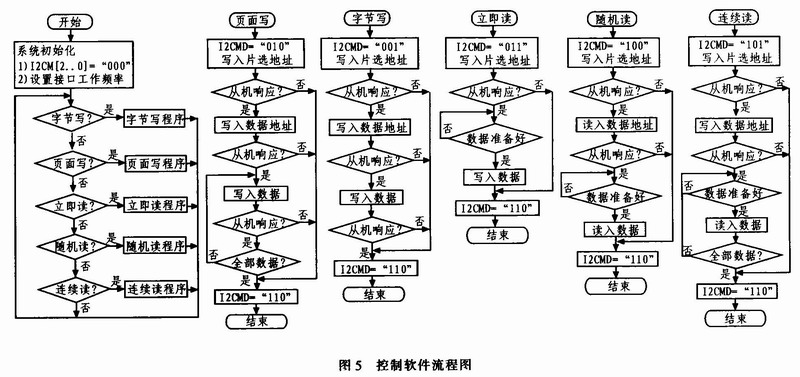

在圖中,PC104 CPU通過數(shù)據(jù)總線、地址總線、讀、寫信號(hào)線與I2C接口模塊相連,I2C接口模塊則通過SDL、SDA與X24C04相連,PC104CPU輸出的并行數(shù)據(jù),經(jīng)過I2C接口模塊轉(zhuǎn)換后變成符合I2C總線模式要求的串行數(shù)據(jù)輸出到X24C04,X24C04輸出的串行數(shù)據(jù)經(jīng)過I2C接口模塊轉(zhuǎn)換后,變成并行數(shù)據(jù)供PC104CPU讀取。使用該模塊后CPU操作I2C總線就像操作并口一樣方便。該電路的控制軟件流程如圖5所示。

通過上述應(yīng)用實(shí)例可以看出,本文設(shè)計(jì)的接口模塊只能工作于主機(jī)模式,并且在整個(gè)系統(tǒng)中只能有一個(gè)主機(jī)工作。在從機(jī)因處理其他工作而暫不能響應(yīng)主機(jī)時(shí),模塊沒有設(shè)計(jì)等待功能,只能發(fā)送總線結(jié)束信號(hào)結(jié)束當(dāng)前操作,待從機(jī)空閑時(shí)再重新開始通信。

4 結(jié)論

本設(shè)計(jì)的創(chuàng)新點(diǎn)在于:通過CPLD實(shí)現(xiàn)并口到I2C總線接口的轉(zhuǎn)換,可以使不具備I2C總線接口的CPU通過并口方便地控制I2C總線設(shè)備,使用該模塊可以簡化控制軟件的編程,加快系統(tǒng)設(shè)計(jì)的實(shí)現(xiàn),在I2C總線操作過程中,轉(zhuǎn)換模塊自動(dòng)發(fā)出開始信號(hào)、結(jié)束信號(hào),不需要CPU干預(yù)。

本文設(shè)計(jì)的I2C接口模塊只能工作于主模式,只能應(yīng)用于主機(jī)系統(tǒng);在模塊的設(shè)計(jì)中,沒有考慮多主機(jī)的情況,對(duì)多主機(jī)的總線競(jìng)爭(zhēng)沒有設(shè)計(jì)仲裁功能;模塊的頁面讀寫數(shù)據(jù)數(shù)不能超過32個(gè)字節(jié),在32個(gè)字節(jié)之內(nèi),CPU可以通過主動(dòng)設(shè)置工作模式為“110”而終止當(dāng)前操作,達(dá)到連續(xù)讀寫小于32個(gè)字節(jié)數(shù)據(jù)的目的,超過32個(gè)字節(jié)的連續(xù)數(shù)據(jù)讀寫操作將使模塊工作錯(cuò)誤。