作為機(jī)載電子設(shè)備之間數(shù)據(jù)傳輸?shù)囊环N標(biāo)準(zhǔn),ARINC429總線以其特有的優(yōu)點(diǎn)在現(xiàn)代軍用與民用飛機(jī)上得到了廣泛的應(yīng)用。它是美國航空無線電公司(ARINC)制定的航空數(shù)字總線傳輸標(biāo)準(zhǔn),定義了航空電子設(shè)備和系統(tǒng)之間相互通信的一種規(guī)范,因此對于ARINC429總線通信的研究是有重要的現(xiàn)實(shí)意義和應(yīng)用前景。為了使系統(tǒng)能夠?qū)RINC429數(shù)據(jù)進(jìn)行處理并將處理好的數(shù)據(jù)發(fā)送出去,文中提出了一種基于DSP和ARINC429專用協(xié)議芯片HS-3282的總線數(shù)據(jù)設(shè)計(jì)方法。

1 ARINC429數(shù)據(jù)傳輸規(guī)范

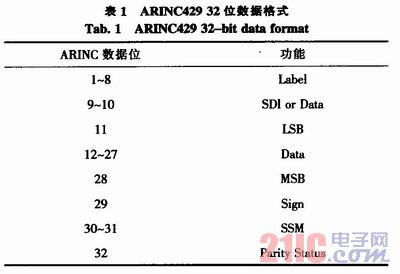

ARINC429總線采用雙絞屏蔽線傳輸信息,通過一對雙絞線反向傳輸,具有很強(qiáng)的抗干擾能力。其調(diào)制方式采用雙極歸零制的三態(tài)碼方式,即信息由“高”、“零”和“低”3種狀態(tài)組成。ARINC429總線的1個(gè)數(shù)據(jù)字有32位,32位數(shù)據(jù)字以脈沖形式發(fā)送,采用了雙極歸零調(diào)制,發(fā)送出去的脈沖有3個(gè)電平,即高電平(+10V)、中電平(0V)、低電平(-10V)。高電平為邏輯1,低電平為邏輯0,中電平為發(fā)送自身時(shí)鐘脈沖。429數(shù)據(jù)的兩個(gè)數(shù)據(jù)字之間有4位間隔,這4位間隔作為字同步。一般ARINC429發(fā)送速度有2種:一種為高速,100kbit/s;一種為低速,12.5 kbit/s。通常高速用于軍用飛機(jī)上,低速用于民用飛機(jī)上。ARINC429數(shù)據(jù)格式如表1所示。

2 系統(tǒng)硬件設(shè)計(jì)

本系統(tǒng)主要是實(shí)現(xiàn)ARINC429總線數(shù)據(jù)信息的接收和發(fā)送。本系統(tǒng)中采用TI公司的DSP芯片TMS320F2812為控制核心和CPLD芯片作譯碼電路控制429數(shù)據(jù)收發(fā)芯片時(shí)序邏輯,配合1片高性能ARINC429數(shù)據(jù)收發(fā)芯片HS-3282和1片ARINC429數(shù)據(jù)發(fā)送驅(qū)動芯片HS-3182,形成1個(gè)數(shù)據(jù)接收通道和1個(gè)數(shù)據(jù)發(fā)送通道,由它們構(gòu)成數(shù)據(jù)收發(fā)、串/并、并/串轉(zhuǎn)換的主體,其系統(tǒng)結(jié)構(gòu)框圖如圖1所示。

2.1 TMS320F2812

在整個(gè)系統(tǒng)中,TI公司的DSP芯片是整個(gè)接口系統(tǒng)的核心,采用TMS320F2812,主要用來控制各個(gè)部分協(xié)調(diào)工作,完成對接收/發(fā)送數(shù)據(jù)的處理和與CPLD配合產(chǎn)生收發(fā)模塊所需要的控制信號。作為TI公司首推的TMS320F2812具有很高的性價(jià)比,廣泛應(yīng)用于工業(yè)控制,特別是應(yīng)用于處理速度、處理精度等方面要求較高的領(lǐng)域,在電子控制領(lǐng)域發(fā)揮著重要的作用,推動了電子信息化的進(jìn)程。由于TMS320F2812采用了先進(jìn)的改進(jìn)型哈佛結(jié)構(gòu),流水線技術(shù),指令執(zhí)行速度快,具有可高達(dá)150 MIPS的處理能力,完全能夠滿足ARINC429信號的處理。并且片內(nèi)具有128 k Flash存儲器,使得電路的設(shè)計(jì)比較簡單。

2.2 HS-3282簡介

HS-3282是美國Harris公司生產(chǎn)的專門面對ARINC429總線的一種高性能CMOS總線接口芯片,能滿足ARINCA29協(xié)議的譯碼、時(shí)分復(fù)用、串行數(shù)據(jù)協(xié)議等標(biāo)準(zhǔn)的要求。當(dāng)它與驅(qū)動芯片HS-3182配合使用時(shí),能正確收發(fā)ARINCA29規(guī)范數(shù)據(jù),且抗干擾性能好。因而采用其來設(shè)計(jì)ARIN-C429總線接口電路既簡單、有效,又能保證可靠性。

HS-3282包含兩路接收器和一路發(fā)送器,接收器和發(fā)送器分別獨(dú)立工作。兩個(gè)分別獨(dú)立的接收器直接與ARINC429總線相連,并以十倍于接收數(shù)據(jù)速率的頻率工作,發(fā)送器的數(shù)據(jù)速率可以與接收器速率相同或不同。盡管兩個(gè)接收器工作在同一個(gè)頻率下,但是它們獨(dú)立工作并異步接收串行數(shù)據(jù)。ARINC總線接口芯片發(fā)送器主要包括FIFO存儲器和時(shí)鐘電路。FIFO存儲器能夠?yàn)榘l(fā)送器連續(xù)保存8個(gè)ARlNC數(shù)據(jù)。時(shí)鐘電路用來正確分隔每個(gè)ARINC數(shù)據(jù)字以滿足ARINC429規(guī)范。盡管ARINC429規(guī)范指定為包含校驗(yàn)位的32位字,通過編程,HS-3282的數(shù)據(jù)字長度也可以為25位。HS-3282接收器是將串行429數(shù)據(jù)轉(zhuǎn)換為2個(gè)并行的16位數(shù)據(jù),而發(fā)送器則是將2個(gè)并行的16位數(shù)據(jù)轉(zhuǎn)化為串行429數(shù)據(jù)。

2.3 ARINC數(shù)據(jù)收發(fā)模塊

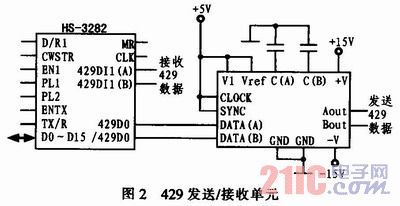

該模塊主要完成ARINC429數(shù)據(jù)的接收、發(fā)送和速率轉(zhuǎn)換等功能,利用1片高性能的ARINC429數(shù)據(jù)收發(fā)芯片HS-3282和1片ARINC429數(shù)據(jù)發(fā)送驅(qū)動芯片HS-3182完成一路接收和一路發(fā)送通道,由它們完成數(shù)據(jù)緩存,串/并、并/串轉(zhuǎn)換和系統(tǒng)內(nèi)部邏輯信號與ARINC429差分信號的轉(zhuǎn)換。

HS-3182為正式差分輸出,用來把要發(fā)送的信息轉(zhuǎn)變?yōu)榉螦RINC429傳輸規(guī)范的電平,與驅(qū)動芯片HS-3182相連的電容用來改善輸出數(shù)據(jù)的上升沿和下降沿,這里對于不同的數(shù)據(jù)傳輸速率選擇不同的電容,75 pF電容對應(yīng)ARINC429總線高速工作狀態(tài),300 pF電容對應(yīng)低速作狀態(tài),這兩個(gè)電容極其重要,為了提高穩(wěn)定性、降低干擾,最好采用軍品電容。

數(shù)據(jù)發(fā)送單元主要完成把并行的信息轉(zhuǎn)化為串行信息,再把串行信息轉(zhuǎn)變?yōu)殡p極性歸零碼,發(fā)送至ARINC429總線。數(shù)據(jù)接收單元主要把ARINC429總線上來的雙極性歸零串行信息轉(zhuǎn)變?yōu)橐话愕拇行畔ⅲ俳?jīng)過移位寄存器轉(zhuǎn)換為并行信息。ARINC429數(shù)據(jù)發(fā)送/接收單元的原理圖如圖2所示。

HS-3282中D/R1接F2812的外部中斷,使429數(shù)據(jù)接收為中斷接收;CWSTR、ENTX、TX/R、MR等經(jīng)電平轉(zhuǎn)換連接到F2812的I/O口;429DI(A)和429DI(B)直接連接429總線,接收來自429總線的數(shù)據(jù);429D0及/429D0和HS-3182的DATA(A)、DATA(B)連接,將HS-3282發(fā)送器的數(shù)據(jù)經(jīng)HS-3182驅(qū)動后發(fā)送至429總線。

2.4 CPLD邏輯控制

對于F2812,每個(gè)區(qū)域的讀、寫操作時(shí)序都可以單獨(dú)配置,且每個(gè)區(qū)域都有片選信號,當(dāng)片選信號被置低(置0),那么當(dāng)前用戶將訪問相應(yīng)的存儲空間(讀、寫操作)。在本系統(tǒng)中,選用Zone0空間,Zone0占用的外部總線地址為0x2000~0x3FFF,當(dāng)XA[13]為高電平,XA[14]為低電平時(shí)選擇ZoneO空間,Zone0片選使能邏輯如圖3所示。

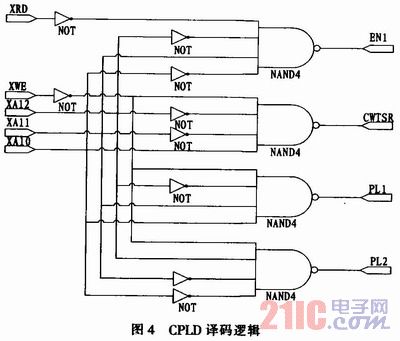

CPLD集成了系統(tǒng)地址選擇模塊,實(shí)現(xiàn)對外部器件的訪問。CPLD的邏輯功能決定了HS-3282的功能地址,通過地址譯碼產(chǎn)生HS-3282所需要的控制信號PL1、PL2、EN1和CWSTR所需要的控制信號。系統(tǒng)中譯碼模塊的邏輯如圖4所示。由片選使能和CPLD譯碼邏輯可得PL1、PL2、EN1和CWSTR的選通地址。

3 系統(tǒng)軟件設(shè)計(jì)

此系統(tǒng)的軟件部分主要包括初始化模塊、數(shù)據(jù)的發(fā)送/接收子程序模塊。

1)初始化模塊系統(tǒng)上電后,首先進(jìn)行初始化,初始化模塊包括上電芯片復(fù)位和寫控制字到HS-3282控制字寄存器。該控制字主要有字長、接收速率、發(fā)送速率、源目的解碼和自測試設(shè)置。初始化流程圖如圖5(a)所示。

2)ARINC429數(shù)據(jù)發(fā)送模塊數(shù)據(jù)發(fā)送是首先向FIFO寫入數(shù)據(jù),然后經(jīng)HS-3182驅(qū)動發(fā)送到總線。在向FIFO寫操作過程中,PL1先于PL2有效,多次的寫PL1將會使先前的數(shù)據(jù)被覆蓋,PL1有效時(shí),低16位數(shù)據(jù)被發(fā)送到FIFO中。當(dāng)PL2有效時(shí),高16位數(shù)據(jù)被傳送到FIFO中。第1個(gè)數(shù)據(jù)字寫入后TX/R由高變低,然后通過置發(fā)送使能信號ENTX,HS-3282將數(shù)據(jù)字串行發(fā)送出去,并自動在相鄰兩個(gè)字之間插入4bit間隔。當(dāng)FIFO為空時(shí),TX/R由低變高,此時(shí)應(yīng)當(dāng)禁止發(fā)送使能信號ENTX,以便向FIFO重新寫入數(shù)據(jù)。當(dāng)HS-3282處于發(fā)送狀態(tài)時(shí),不能向FIFO寫入數(shù)據(jù)。發(fā)送模塊流程圖如圖5(b)所示。

3)ARINC429數(shù)據(jù)接收模塊 數(shù)據(jù)接收模塊被設(shè)計(jì)為中斷接收,由HS-3282的D/R1提供中斷信號。當(dāng)D/R1為0時(shí),進(jìn)入中斷,并表明ARIN-C429總線上有數(shù)據(jù)到來,此時(shí)選通EN1地址,再置SEL為0,接收低16位數(shù)據(jù);接著置SEL為1,再選通EN1地址,接收高16位數(shù)據(jù)。接收模塊流程圖如圖5(c)所示。

4 結(jié)束語

針對ARINC429總線的應(yīng)用,提出了TMS320F2812與ARINC429總線通信的軟硬件設(shè)計(jì)和實(shí)現(xiàn)方案。該設(shè)計(jì)硬件電路簡單,數(shù)據(jù)通信程序可讀性好,編寫容易,數(shù)據(jù)傳輸準(zhǔn)確可靠。在設(shè)計(jì)TMS320F2812數(shù)據(jù)總線讀寫的邏輯控制時(shí),XRD和XWE信號必須參與邏輯控制,保證順利讀寫總線數(shù)據(jù)。經(jīng)驗(yàn)證該系統(tǒng)能夠有效地完成2個(gè)16位并行數(shù)據(jù)到32位串行數(shù)據(jù)的轉(zhuǎn)換,實(shí)現(xiàn)了TMS320F2812 DSP與ARINC429總線之間的數(shù)據(jù)通信,且傳輸速率為100 kb,達(dá)到了系統(tǒng)的設(shè)計(jì)要求。該系統(tǒng)可廣泛借鑒并應(yīng)用于ARINC429總線數(shù)據(jù)傳輸系統(tǒng)及ARINC429接口卡設(shè)計(jì)中。