1 引言

隨著芯片集成程度的飛速提高,一個電子系統(tǒng)或分系統(tǒng)可以完全集成在一個芯片上,IC產(chǎn)業(yè)中形成了以片上系統(tǒng)SOC(System-on-Chip)技術為主的設計方式。同時IC設計能力和EDA工具卻相對落后于半導體工藝技術的發(fā)展,兩者之間日益加劇的差距已經(jīng)成為SOC技術發(fā)展過程中一個突出的障礙。采用基于IP復用技術進行設計是減小這一差距惟一有效的途徑,IP復用技術包括兩個方面的內(nèi)容:IP核生成和IP核復用。文中采用IP核復用方法和SOC技術基于AVR 8位微處理器AT90S1200IP Core設計專用PLC微處理器FSPLCSOC模塊。

2 IP核復用

IP核復用(IP Core Reuse)是指在集成電路設計過程中,通過繼承、共享或購買所需的知識產(chǎn)權(quán)內(nèi)核(第三方IP核),然后再利用EDA工具進行設計、綜合和驗證。IP核是IP復用的載體和核心內(nèi)容,基于應用需求、規(guī)范協(xié)議和行業(yè)標準的不同,IP核的內(nèi)容也是千差萬別的。在IC產(chǎn)業(yè)中,IP核被定義為用于ASIC, ASSP, PLD等芯片中,且預先定義好功能、經(jīng)過驗證的、可重復利用的電路功能模塊,如PCI接口核、ADC核,F(xiàn)IR濾波器核、SDRAM控制器核等。根據(jù)IC設計層次的不同。IP核分為以下三類:軟IP(Soft IP)、硬IP(Hard IP),固IP (Firm IP)。文中主要涉及到軟IP核設計和復用。軟IP是可類比、綜合的硬件描述語言(HDL)模型,通常是可綜合的RTL模型,包括邏輯描述、網(wǎng)表和測試的文檔(Testbench)。軟IP設計周期短、投人少,與工藝無關,可靈活修改,在設計中只須對時序、面積和功耗進行修正,可復用性最高。基于軟核的設計(Soft Core-based design)是一種非常實用的SOC設計方法。它將系統(tǒng)的功能劃分為不同的軟核,包括微處理器、ALU、ROM、PC、ROM、I/0等。由于軟IP核僅提供能夠綜合的HDL描述,因此復用前需要深人地了解HDL文件描述的RTL模型,采用適當工藝技術的標準單元庫,再重新進行綜合、布局布線、后仿真提取網(wǎng)表、驗證時序等反復工作,最后集成到SOC設計中,因此SOC設計即生成的IP核和第三方復用IP核集成整合。

3 FSPLC微處理器IP核設計

3.1 IP軟核生成

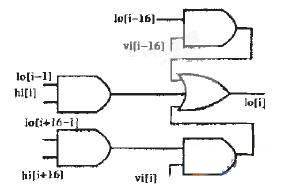

文中基于AVR8位微處理器分析實際PLC梯形圖及其指令表,設計邏輯處理器LP、布爾處理器BP、存儲器位接口MBI等3個模塊用于提高PLC執(zhí)行速度,下面以邏輯處理器LP單元模塊為例,描述IP軟核生成。PLC梯形圖包括8種基本電路:左分支觸點LBC/非觸點LBCN,右分支觸點RBC/非觸點RBCN,雙分支觸點DBC/非觸點DBCN,不分支觸點NBC/不分支非觸點NBCN。文中根據(jù)這8種基本電路設計一個16xl6觸點矩陣電路,即邏輯處理器LP單元,矩陣中各個觸點由電子電路模擬PLC梯形圖基本電路。在任何一個觸點上包括橫線輸入、豎線輸入、引出輸出線圈。觸點矩陣中共有256個橫線輸入圈節(jié)點hi,240個豎線輸入圈節(jié)點vi,256個輸出線圈Io。當一行超過16時,轉(zhuǎn)向下一行,以此構(gòu)成矩陣電路,如hi[i],vi[i],lo[i]表示某個觸點的橫線輸入、豎線輸入、輸出,那么其同行的下一個觸點的橫線輸入、豎線輸入、輸出分別為hi[i+ 1]、vi[i+1]、lo[i+1],其同列的下一個觸點hi[i+16]、vi[i+16]、lo[i+16],那么輸出觸點的表達式為

I0[i]=I0[i-1]hi[i]+vi[i-16]lo[i-16]+vi[i]lo[i+16-1]hi[ i+16] 。

以此各個觸點彼此互相連接組成處理梯形圖的觸點矩陣。如圖1所示。

圖1 LP單元觸點電子電路模擬

邏輯處理器LP采用Verilog描述,借助Model-Sim進行功能仿真,驗證模塊功能的正確性。LP單元功能仿真波形如圖2所示。

圖2 LP單元功能仿真波形

驗證功能正確后,借助Synosys的綜合工具Synplify Pro對模塊進行綜合。綜合包括Compiling、Mapping、Optimization。綜合時將經(jīng)ModelSim。功能仿真驗證的源代碼調(diào)人Synplify Pro,執(zhí)行Compiler,編譯后,創(chuàng)建約束文件。sdc,編輯約束文件對模塊添加約束條件,包括時鐘、面積、扇人扇出、延時等,添加約束后執(zhí)行綜合,產(chǎn)生網(wǎng)表文件。EDF。根據(jù)綜合后給出的。log文件觀察Constraint文件中的約束條件是否滿足需要,例如按照給出的“Worst Path Information,修改約束以滿足Worst Path的要求。綜合完成后在Quartus Ⅱ4。0展開網(wǎng)表文件,布局布線后編譯形成。sof文件,將此文件下級到Alters Nios開發(fā)板進行驗證,驗證正確后再借助ModelSim進行時序驗證。

3.2 AVR IP核復用

AVR8位微處理器AT90S1200IP核由opencores。org提供。整個微處理器IP核包括ALU、PC、SRAM、IR、ROM、I/0,控制等”個模塊,可以分成3個單元;取指單元、執(zhí)行單元和I/0單元。指令執(zhí)行時,取指單元負責取出下一個指令,執(zhí)行單元負責執(zhí)行當前指令,而LO單元負資和外界的連接。取指單元和執(zhí)行單元組成微處理器的CPU。

整個AVRIP核包括許多寄存器:指令寄存器、指令備份寄存器、程序計數(shù)器、通用寄存器、存儲地址寄存器(MAR),1/O口控制寄存器等。整個系統(tǒng)的工作就是基于這些寄存器之間的數(shù)據(jù)傳輸。設計所有的寄存器以及它們之間的組合邏輯及其連接就是系統(tǒng)的數(shù)據(jù)通道設計。控制模塊決定怎樣進行寄存器傳愉。數(shù)據(jù)通道和控制單元組成了整個微處理器。

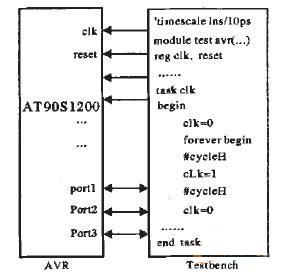

對于AT90S12001P核復用,考慮到IP核在SOC中集成整合,首先須徹底了解所復用核的架構(gòu)和指令集,借助ModelSim進行功能仿真,建立Testbench平臺測試波形驗證功能的正確性,如圖3所示。編譯無誤且功能正確后借助Synplify Pro對IP核飾代碼進行邏輯綜合,如果VHDL程序正確無誤并且其編程風格符合Synplify Pro綜合要求,Synplify Pro將產(chǎn)生一個網(wǎng)表文件(。EDF文件),再借助QuartusA4。0和ModelSim分別進行FPGA驗證和時序驗證,此過程不斷循環(huán),直至復用的微處理器IP核沒有任何錯誤。

圖3 AVRIP復用測試平臺Testbench框圖

4 FSPLC微處理器核SOC設計

4.1 SOC硬件結(jié)構(gòu)

根據(jù)FSPLCSOC系統(tǒng)功能定義,設計完成FSPLC微處理器硬件結(jié)構(gòu),如圖4所示。

圖4 FSPLCSOC硬件結(jié)構(gòu)框圖

FSPLCSOC由AT90S1200、布爾處理器BP、存儲器位接口MBI、邏輯處理器LP,CAN總線1。0接口CBI、底板總線接口BBI等6個模塊組成。AT90S1200模塊是SOC的核心,實現(xiàn)PLC指令的執(zhí)行;BP模塊由兩個位累加器和一個位邏輯堆淺BLS組成,該結(jié)構(gòu)可以有效處理IEC61131-3(國際電工委員會制訂的基于Windows編程語言標準)PLC指令表語句中復雜的嵌套邏輯運算,使運行頻率最高的位指令達到最大的執(zhí)行速度;存儲器位接口模塊由一個存儲器位尋址接口邏輯和一個8選1選擇器組成,為布爾處理器和數(shù)據(jù)存儲器之間的位訪間接口;CAN總線1。0接口CBI模塊和外部基于Atmega8515的USB-CAN適配器相連,通過此適配器FSPLC可以和其他帶有CAN接口的PLC實現(xiàn)CAN通訊;通過底板總線接口BBI模塊可以在FSPLC片外擴展模塊,最多可以達到8個,包括I/0擴展模塊、AID模塊、D/A模塊、計數(shù)模塊等。其中AT90S1200,MBI,LP,CBI,BBI模塊通過內(nèi)部總線連接,BP通過MBI模塊轉(zhuǎn)換實現(xiàn)和其他模塊的連接。

4.2 FSPLCSOC仿真、綜合、驗證

由于SOC設計是一種面向IP核集成的設計,整合后的SOC模塊同第三方IP核復用一樣需要進行模塊的仿真、綜合和驗證。FSPLC SOC同復用AT90SI200核一樣借助ModelSim進行功能仿真和驗證后時序仿真,借助Synplify Pro進行綜合。

下面具體描述FSPLCSOC的驗證,SOC設計中包含了系統(tǒng)設計和模塊設計,因此SOC驗證一般包含了模塊驗證、芯片驗證和系統(tǒng)驗證三個部分。由于FSPLCSOC涉及到的主要是數(shù)字IP核,文中采用Altera NioslI開發(fā)板作為設計的驗證平臺,該開發(fā)板帶有一個20多萬門的Altera EP20K200EFC484-2的FPGA芯片、撥碼開關、數(shù)碼顯示器等,用一個實際PLC應用程序在此開發(fā)板上對FSPLCSOC進行了可行性驗證,同時通過對AVR編譯器Avral。0的編譯代碼變量中增加PLC指令代碼,使之能夠?qū)L(:指令進行編譯。圖5,圖6分別為PLC控制程序的梯形圖及其匯編程序。

圖5 PLC控制程序的梯形圖

開發(fā)板的撥碼開關SWl的1、2、3、4來模擬上述開關的閉合,觀察數(shù)碼顯示器Dl數(shù)碼段明暗,驗證設計的可行性。FSPLCSOC在Altera Nios開發(fā)板的FPGA芯片上進行了可行性驗證,獲得了理想的運行效果:在33MHz晶振下,執(zhí)行基本邏輯指令速度為0。09μ/條,達到了國際上大中型PLC的處理速度。

圖6 PSPLC匯編程序

5 結(jié)束語

目前IC產(chǎn)業(yè)中,SOC已成為最主要的集成電路設計方法8位RISC微處理器芯片設計正在向SOC化發(fā)展,通過IP核復用方法以縮短周期、降低成本、提高效率。文中基于IP核復用和SOC技術借助ModelSim、Synplify Pro、QuartusⅡ等EDA軟件設計了擁有自主知識產(chǎn)權(quán)的專用PLC微處理器SOC模塊FSPLC,在復用了第三方AVRAT90SI200IP核基礎上集成了自行設計的LP、BP、MBI、CBI、BBI等模塊,具有快速處理PLC梯形圖程序、快速處理IL語句表中復雜的嵌套邏輯運算、PLC之間CAN總線通訊等優(yōu)點。最后采用Altera NiosII作為驗證平臺,對實際的PLC應用程序做了可行性驗證,獲得了理想的效果。