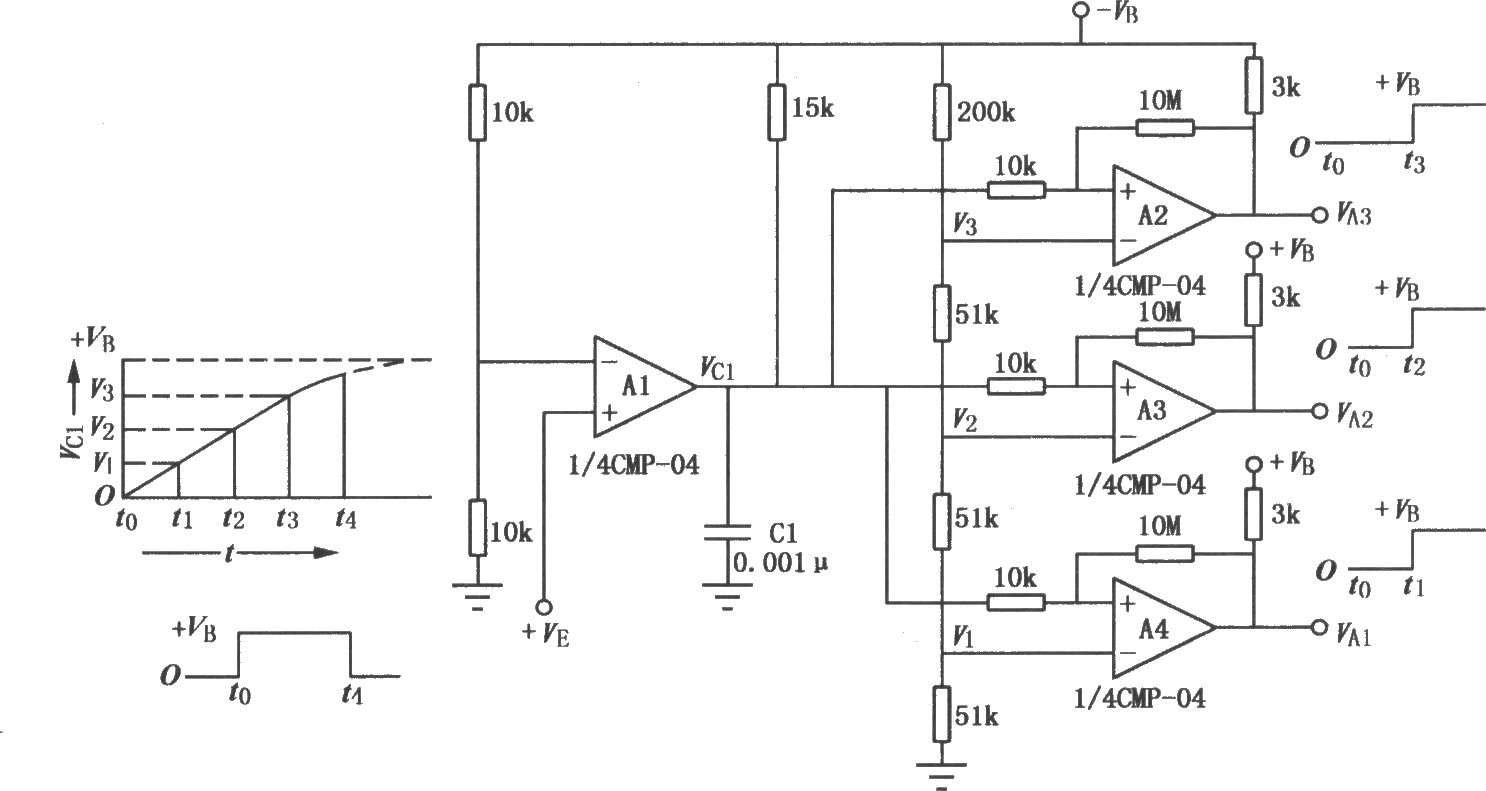

如圖是具有多級輸出的延遲電路,。電路中采用了運算放大器作比較器,,當運算放大器A1的同相輸入端加電壓 VE后,,在運算放大器A2,、A3、A4同相輸入端上的電壓VC1將沿著指數(shù)曲線規(guī)律上升,。運算放大器的反相輸入端加入由分級分壓器提供的電壓。因此各運算放大器輸入在Vc1由零變?yōu)?VB(電源電壓)的t1,、t2,、t3時刻,分別使各輸出信號翻轉(zhuǎn),,從而實現(xiàn)了VA1,、VA2、VA3逐級延時的目的,。注意本電路使用了雙電源,,即正電源 VE、 VB與負電源-VB,。