傳真通信不僅能傳送圖像/ 圖形信息,而且可以保留其具體的形式,因此,真跡傳送是傳真通信又一主要特點,也是最具魅力的特點。隨著因特網(wǎng)的發(fā)展,收發(fā)電子郵件已經(jīng)成為大部分公司與個人或其他公司進行通信聯(lián)系的主要方式。在公司內(nèi)部,相比使用電話進行通信,人們更愿意使用電子郵件,電子郵件已經(jīng)成為大多數(shù)人的第二種主要通信手段。相比傳統(tǒng)傳真,電子郵件有一個顯著的優(yōu)點: 成本很低。基于這種原因,人們自然會聯(lián)想到通過因特網(wǎng)發(fā)送傳真,這就是網(wǎng)絡(luò)傳真。

雙網(wǎng)數(shù)字傳真機與普通傳真機的最大區(qū)別是增加了網(wǎng)絡(luò)傳輸接口,具有普通電話網(wǎng)和因特網(wǎng)兩種傳輸模式,增強了傳真機的功能,擴展其適用范圍,提高了傳輸效率和傳輸可靠性,保證良好的圖像質(zhì)量,并大幅度地降低了傳真所帶來的長途通信費用。

雙網(wǎng)數(shù)字傳真機是一個雙處理器結(jié)構(gòu)( 主處理器是SCE214,從處理器是A RM S3C4510B) 的嵌入式系統(tǒng),要實現(xiàn)網(wǎng)絡(luò)傳真功能首先必須實現(xiàn)系統(tǒng)內(nèi)的雙機通信,即主處理器與從處理器的信息交換。

1 雙機通信的硬件實現(xiàn)

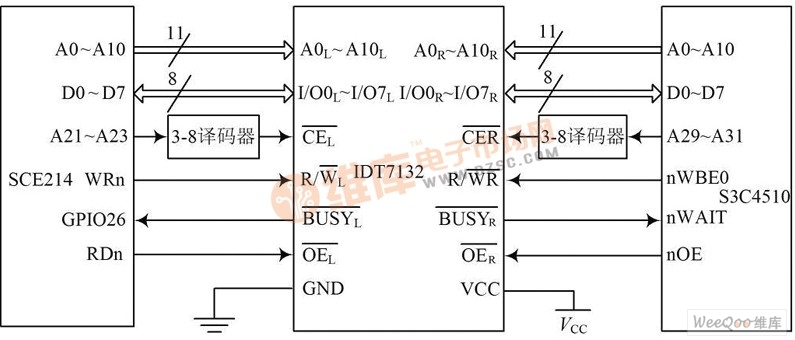

采用IDT 公司的2K ×8 b 的高速雙口RAMIDT7132 來實現(xiàn)雙機通信。雙口RAM 是常見的共享式多端口存儲器,如圖1 所示,雙口RAM 最大的特點是存儲數(shù)據(jù)共享,一個存儲器配備兩套獨立的地址、數(shù)據(jù)和控制線,允許兩個獨立的CPU 或控制器同時異步地訪問存儲單元。既然數(shù)據(jù)共享,就必須存在訪問仲裁控制。內(nèi)部仲裁邏輯控制提供以下功能: 對同一地址單元訪問的時序控制; 存儲單元數(shù)據(jù)塊的訪問權(quán)限分配;信令交換邏輯

( 例如中斷信號) 等。

圖1 雙口RAM 的功能框圖。

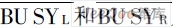

它允許兩個( 左、右) 端口同時讀寫數(shù)據(jù),每個端口具有自己獨立的控制信號線、地址線和數(shù)據(jù)線; 允許數(shù)據(jù)高速存取,最快存取時間為20 ns; 功耗低,工作在省電模式時,功耗為5 mW; 其數(shù)據(jù)保存電壓為2 V,便于用電池完成數(shù)據(jù)的掉電保護。IDT 7132 可以作為8 位雙口RAM 單獨使用,也可以與IDT7142 組成主從式系統(tǒng),將數(shù)據(jù)線擴展到16 位,甚至更寬。IDT7132 支持從其兩個端El 對器件的任何存儲空間進行完全異步的讀/ 寫操作。通過 的控制,IDT7132 自動工作在省電模式下,而且還可以通過接電池達(dá)到數(shù)據(jù)保護的目的。

的控制,IDT7132 自動工作在省電模式下,而且還可以通過接電池達(dá)到數(shù)據(jù)保護的目的。

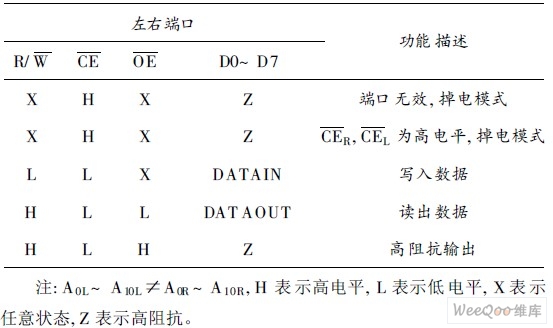

IDT7132 工作情況如下: 當(dāng)左右端口不對同一地址單元存取時, ,可正常存儲,其中: H 表示高電平,L 表示低電平。當(dāng)左右端口對同一地址單元存取時,有一端口的

,可正常存儲,其中: H 表示高電平,L 表示低電平。當(dāng)左右端口對同一地址單元存取時,有一端口的 = L,禁止數(shù)據(jù)的存取。此時,兩個端口中,哪個存取請求信號出現(xiàn)在前,則其對應(yīng)的

= L,禁止數(shù)據(jù)的存取。此時,兩個端口中,哪個存取請求信號出現(xiàn)在前,則其對應(yīng)的 = H,允許存取; 哪個存取請求信號出現(xiàn)在后,則其對應(yīng)的

= H,允許存取; 哪個存取請求信號出現(xiàn)在后,則其對應(yīng)的 = L,禁止其寫入數(shù)據(jù)。需要注意的是,兩端口間的存取請求信號出現(xiàn)時間要相差在5 ns 以上,否則仲裁邏輯無法判定哪一個端口的存取請求信號在前; 在無法判定哪個端口先出現(xiàn)存取請求信號時,控制線

= L,禁止其寫入數(shù)據(jù)。需要注意的是,兩端口間的存取請求信號出現(xiàn)時間要相差在5 ns 以上,否則仲裁邏輯無法判定哪一個端口的存取請求信號在前; 在無法判定哪個端口先出現(xiàn)存取請求信號時,控制線 只有一個為低電平,不會同時為低電平。這樣,就能保證一個對應(yīng)于

只有一個為低電平,不會同時為低電平。這樣,就能保證一個對應(yīng)于 =H 的端口能進行正常存取,對應(yīng)于

=H 的端口能進行正常存取,對應(yīng)于 = L 的端口不存取,避免雙端口存取出現(xiàn)錯誤。非競爭真值表見表1,競爭真值表見表2。

= L 的端口不存取,避免雙端口存取出現(xiàn)錯誤。非競爭真值表見表1,競爭真值表見表2。

表1 IDT7132 非競爭真值表。

表2 IDT7132 競爭真值表。

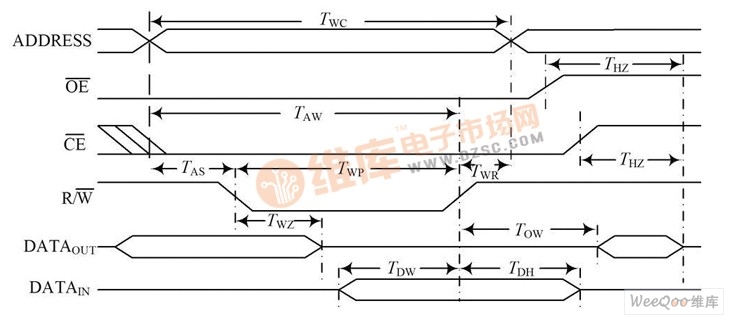

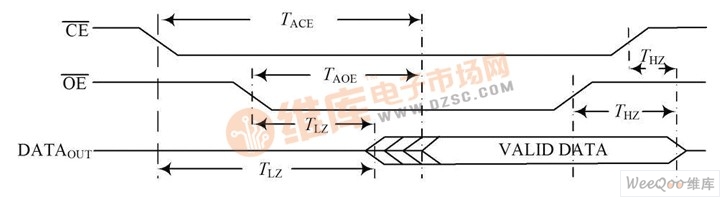

圖2 是IDT7132 在本系統(tǒng)中的連接框圖。IDT7132 的寫入時序圖和讀出時序如圖3,圖4 所示。

在寫入時序圖中,由 脈沖上升沿控制寫入操作,在讀出時序圖中,由

脈沖上升沿控制寫入操作,在讀出時序圖中,由 脈沖上升沿控制讀出操作。

脈沖上升沿控制讀出操作。

圖2雙口RAM 芯片IDT7132 連接框圖。

圖3 IDT7132 寫入時序圖。

圖4 IDT7132 讀出時序圖。

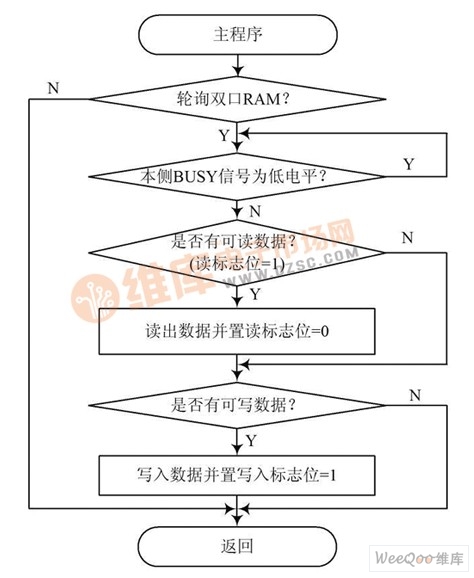

SCE214 和ARM 處理器間數(shù)據(jù)交換的軟件實現(xiàn)是采用輪詢方式分別讀/ 寫雙口RAM。它們的讀/ 寫操作過程基本相同,工作流程如圖5 所示。

圖5 主、從處理器讀/ 寫雙口RAM 流程圖。

SCE214 處理器采用匯編語言實現(xiàn)對雙口RAM 的讀/ 寫; ARM( S3C4510B) 處理器采用C+ + 語言編程,并基于嵌入式操作系統(tǒng)VxWorks 實現(xiàn)對雙口RAM 的讀/ 寫。

當(dāng)SCE214 與S3C4510B 同時向同一存儲單元( # 07FF) 寫入數(shù)據(jù)時,如果對側(cè)地址信號的穩(wěn)態(tài)先于本側(cè)的時,本側(cè) 信號輸出& L.,表示禁止本側(cè)處理器寫入,本側(cè)寫入脈沖中加入等待周期; 若對側(cè)地址信號的穩(wěn)態(tài)晚于本側(cè)時,本側(cè)

信號輸出& L.,表示禁止本側(cè)處理器寫入,本側(cè)寫入脈沖中加入等待周期; 若對側(cè)地址信號的穩(wěn)態(tài)晚于本側(cè)時,本側(cè) 信號輸出" H".,表示本側(cè)處理器可以執(zhí)行寫入操作;

信號輸出" H".,表示本側(cè)處理器可以執(zhí)行寫入操作; 不能同時為" L".。

不能同時為" L".。

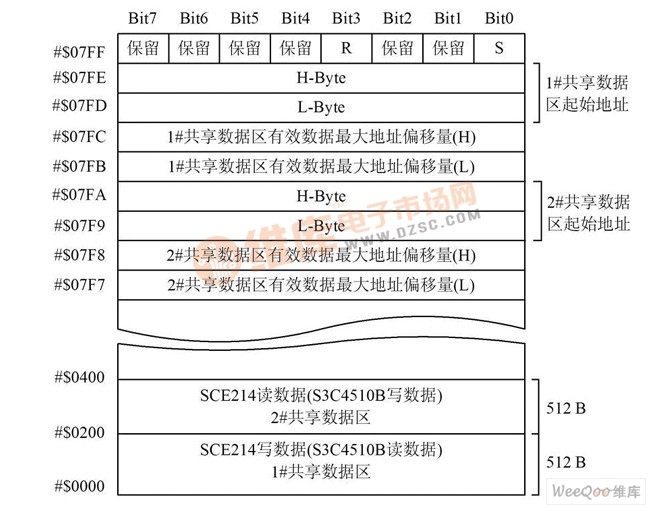

圖6 是雙口RAM IDT7132 存儲器映射圖,IDT7132 空間大小為2 KB,存儲空間劃分為兩部分: 控制區(qū)和數(shù)據(jù)區(qū)。數(shù)據(jù)區(qū)分又分為兩部分: 1# 區(qū)和2#區(qū),其空間均為512 B,1# 區(qū)用于實現(xiàn)SCE214 寫入數(shù)據(jù)和S3C4510B 讀出數(shù)據(jù),2# 區(qū)用于實現(xiàn)SCE214 讀出數(shù)據(jù)和S3C4510B 寫入數(shù)據(jù)。控制區(qū)包含讀/ 寫標(biāo)志、1 # 數(shù)據(jù)區(qū)起始地址及有效數(shù)據(jù)最大地址偏移、2#數(shù)據(jù)區(qū)起始地址及有效數(shù)據(jù)最大地址偏移。

圖6 雙口RAM IDT7132 存儲器映射圖。

處理器對雙口RAM 的操作過程如下:

( 1) SCE214 有寫入數(shù)據(jù)時,將數(shù)據(jù)寫入1# 區(qū),有效數(shù)據(jù)起始地址寫入$ 07FE、$ 07FD 存儲單元中( 按小端格式存放) ,有效數(shù)據(jù)地址最大偏移量寫入$ 07FC、$ 07FB,并將$ 07FF 的Bit0 置為1;( 2) S3C4510B 讀雙口RAM 時,先判斷$ 07FF 的Bit0 是否為1,若為1,從$ 07FE、$ 07FD 存儲單元中取出有效數(shù)據(jù)起始地址,從$ 07FC、$ 07FB 存儲單元中取出有效數(shù)據(jù)地址最大偏移量,根據(jù)有效數(shù)據(jù)起始地址和最大偏移量,讀出雙口RAM 中的數(shù)據(jù),并將$ 07FF 的Bit0 置為0;( 3) S3C4510B 讀雙口RAM 時,若判斷出$ 07FF的Bit0 為0,則S3C4510B 認(rèn)為SCE214 無數(shù)據(jù)發(fā)送來。這時S3C4510B 若有數(shù)據(jù)需要寫入雙口RAM,則將數(shù)據(jù)寫入2# 區(qū),有效數(shù)據(jù)起始地址寫入$ 07FA、$ 07F9存儲單元中( 按小端格式存放) ,有效數(shù)據(jù)地址最大偏移量寫入$ 07F8、$ 07F7,并將$ 07FF 的Bit3 置為1;( 4) SCE214 輪循到讀雙口RAM 操作時,先判斷$ 07FF 的Bit3 是否為1,若為1,從$ 07FA、$ 07F9 存儲單元中取出有效數(shù)據(jù)起始地址,從$ 07F8、$ 07F7 存儲單元中取出最后一個有效數(shù)據(jù)的地址偏移,根據(jù)有效數(shù)據(jù)起始地址和最大偏移量,讀出雙口RAM 中的數(shù)據(jù),并將$ 07FF 的Bit3 置為0;( 5) SCE214 輪循到讀雙口RAM 操作時,若判斷出$ 07FF 的Bit3 為0,SCE214 認(rèn)為S3C4510B 無數(shù)據(jù)發(fā)送來。

如此重復(fù)( 1) ~ ( 5) 的操作,即可完成SCE214 與S3C4510B 的雙向通信,最大一次可傳送512 B數(shù)據(jù)。

2 結(jié)論

雙機通信在嵌入式系統(tǒng)中應(yīng)用比較廣泛,本文介紹的設(shè)計方案主要用于速率要求高、成本適中的場合。

由于本系統(tǒng)采用的是雙處理器結(jié)構(gòu)設(shè)計,給系統(tǒng)的穩(wěn)定性帶來一定的隱患,有待于在以后的研發(fā)中能將雙處理器集成為單片處理器。雙網(wǎng)數(shù)字傳真機研發(fā)的亮點在網(wǎng)絡(luò)傳真,其網(wǎng)絡(luò)傳真實現(xiàn)的業(yè)務(wù)不是實時傳真,加之因特網(wǎng)本身的時延較大,有待用戶檢驗,但其市場前景仍比較樂觀。