UHF RFID" title="RFID">RFID技術(shù)將廣泛應(yīng)用于各個(gè)行業(yè)領(lǐng)域, 可靠的閱讀器是UHF RFID系統(tǒng)的重要組成部分,, 而基帶處理芯片能夠?yàn)殚喿x器設(shè)計(jì)提供基帶信號處理解決方案,。結(jié)合UHF RFID技術(shù)本身所固有的特點(diǎn), 本文的閱讀器設(shè)計(jì)采用了IQ 兩路正交調(diào)制解調(diào)的零中頻方案,。整個(gè)閱讀器由射頻前端和基帶處理兩個(gè)部分組成,, 射頻前端對發(fā)送基帶信號進(jìn)行上變頻和功率放大等處理后發(fā)射給電子標(biāo)簽, 然后在接收到標(biāo)簽的返回信號時(shí),, 對接收信號進(jìn)行放大,、濾波、下變頻等處理后將基帶信號傳輸給基帶處理芯片,。

本文介紹基于ISO / IEC 18000 6C 協(xié)議的UHF RF ID閱讀器基帶處理芯片接收端電路的設(shè)計(jì),, 該電路可以與基帶處理發(fā)送端、中央處理器( CPU )集成,, 共同構(gòu)成整個(gè)基帶處理芯片,。

1 電路總體結(jié)構(gòu)

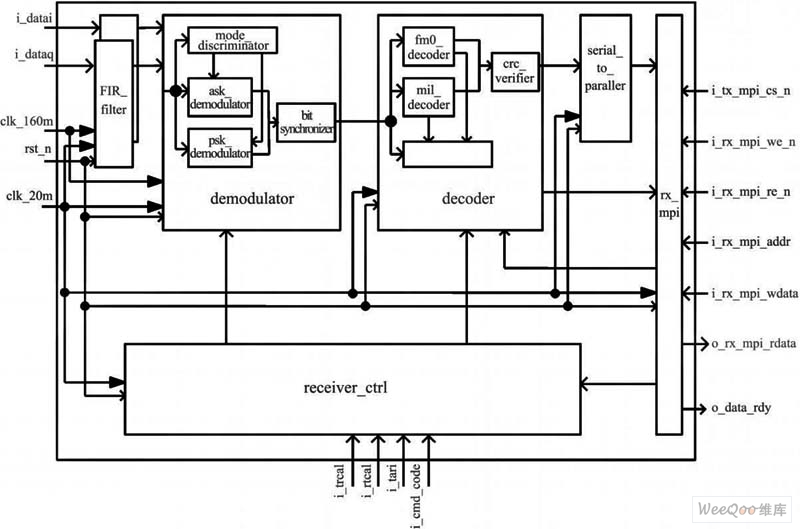

UHF RFID閱讀器" title="RFID閱讀器">RFID閱讀器基帶處理接收端電路的總體結(jié)構(gòu)如圖1所示, 主要包括輸入基帶信號低通濾波器,、解調(diào)器,、解碼器、數(shù)據(jù)串并轉(zhuǎn)換模塊,、信息傳遞接口(MPI)模塊和接收機(jī)控制模塊六個(gè)功能模塊,。

從ADC 采樣進(jìn)來的兩路基帶正交信號i_data i和i_dataq首先經(jīng)過低通濾波器FIR _ filter進(jìn)行濾波, 以便后級電路對信號進(jìn)行處理。

UHF RFID閱讀器基帶處理" title="RFID閱讀器基帶處理">RFID閱讀器基帶處理接收端電路框圖

圖1 UHF RFID閱讀器基帶處理接收端電路框圖

濾波后的I和Q信號進(jìn)入解調(diào)器demodu lator,, 調(diào)制方式自動識別子模塊mode_d iscrim inator首先識別接收信號的調(diào)制方式,, 之后選擇對接收信號進(jìn)行ASK或者PSK 解調(diào)得到?jīng)]有實(shí)現(xiàn)位同步的信號, 最后位同步子模塊bit_synchrono izer從該信號提取出位同步時(shí)鐘并判決得到同步二進(jìn)制數(shù)據(jù)流,。解調(diào)后數(shù)據(jù)流與提取出來的同步時(shí)鐘脈沖一起輸出到解碼器decoder,, 按照FM0或M iller編碼規(guī)則對數(shù)據(jù)進(jìn)行解碼,同時(shí)檢查編碼規(guī)則并對編碼規(guī)則錯(cuò)誤進(jìn)行計(jì)數(shù),。若沒有出現(xiàn)編碼規(guī)則錯(cuò)誤,, 還將在CRC 校驗(yàn)子模塊crc_verifier中對解碼后的數(shù)據(jù)進(jìn)行CRC 16校驗(yàn)。

解碼出來的信號是串行的,, 而在信息傳遞接口模塊rx_mp i中的接收緩存是并行輸入的,, 所以將數(shù)據(jù)存入緩存中之前由數(shù)據(jù)串并轉(zhuǎn)換模塊serial_to_para lle l完成串行數(shù)據(jù)轉(zhuǎn)換為并行數(shù)據(jù)。該模塊產(chǎn)生接收緩存的寫數(shù)據(jù),、寫地址和寫使能信號,, 并對接收到的數(shù)據(jù)進(jìn)行計(jì)數(shù), 計(jì)數(shù)結(jié)果放在rx_mp i中指定的寄存器中供CPU 查詢,。數(shù)據(jù)串并轉(zhuǎn)換模塊同時(shí)檢測緩存是否溢出并給出緩存溢出錯(cuò)誤標(biāo)志信號,,在每一幀數(shù)據(jù)結(jié)束處給出幀結(jié)束脈沖信號。

信息傳遞接口模塊rx_mp i主要負(fù)責(zé)基帶處理電路(包括接收端,、發(fā)送端)和CPU 之間的數(shù)據(jù)通信,。

該模塊首先把接收到的數(shù)據(jù)寫入接收緩存中, 并在結(jié)束時(shí)置數(shù)據(jù)準(zhǔn)備好標(biāo)志寄存器DATA _RDY 有效(在出現(xiàn)幀起始檢測發(fā)生超時(shí)錯(cuò)誤時(shí)也置數(shù)據(jù)準(zhǔn)備好標(biāo)志寄存器DATA _RDY 有效)以通知CPU 取走數(shù)據(jù),,同時(shí)寄存各種錯(cuò)誤標(biāo)志信號和錯(cuò)誤計(jì)數(shù)值到相應(yīng)寄存器供CPU 查詢,。除此, rx _mp i還負(fù)責(zé)接收來自CPU的指令信息并配置相應(yīng)的控制寄存器,。

接收機(jī)控制模塊receiver_ctrl是接收部分的中央控制模塊,, 根據(jù)控制寄存器中的配置信息輸出各個(gè)模塊需要的控制信號, 用以配置各個(gè)功能模塊的工作模式,。

2 解調(diào)器設(shè)計(jì)

解調(diào)器主要包括ASK 解調(diào),、PSK解調(diào)、解調(diào)模式識別和位同步四個(gè)子模塊,。解調(diào)模式識別子模塊根據(jù)CPU 的配置或接收信號的特征決定采用ASK 或PSK 解調(diào)方法對信號進(jìn)行解調(diào),, 位同步子模塊從接收數(shù)據(jù)中提取位時(shí)鐘信號用來重新同步接收數(shù)據(jù)。

2. 1 ASK解調(diào)子模塊

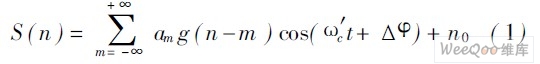

當(dāng)閱讀器接收來自電子標(biāo)簽的信號采用ASK調(diào)制時(shí),, 接收信號可以用如下表達(dá)式表示:

式中,, am 為輸入碼元,, 取0或1; g ( n - m )是幅度為1,、寬度為單個(gè)碼元持續(xù)時(shí)間的波形函數(shù); 接收信號的載波頻率ω‘c與接收機(jī)本地載波頻率ωc 存在頻率偏移, 且兩者之間還有相位差△φ, 與閱讀器發(fā)射天線和電子標(biāo)簽之間的距離有關(guān); n0 為接收到的加性噪聲,。

一般的ASK解調(diào)在對S ( n )進(jìn)行正交分解得同相和正交分量I 和Q 后,, 求其平方和與開方??傻茫?br />

即: 對A ( n )進(jìn)行抽取判決,, 便可以恢復(fù)出碼元信號。

本文根據(jù)UHF RFID 技術(shù)的特殊性,, 采用如下方法對ASK 調(diào)制信號進(jìn)行解調(diào): 雖然I’和Q‘隨著閱讀器與標(biāo)簽之間距離的改變而變化,, 變化時(shí)強(qiáng)時(shí)弱,但是I’和Q‘具有功率互補(bǔ)性,, 即在I’最弱的時(shí)候Q‘最強(qiáng)或者相反,。根據(jù)這個(gè)特點(diǎn), 本文在每幀標(biāo)簽返回信號的幀前導(dǎo)序列出現(xiàn)時(shí)比較I’和Q‘的強(qiáng)度,, 然后選擇信號比較強(qiáng)的一路分量進(jìn)行判決,。

ASK 解調(diào)示意圖

圖2 ASK 解調(diào)示意圖

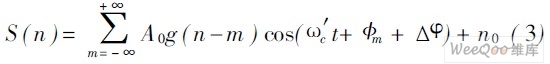

2. 2 PSK 解調(diào)子模塊

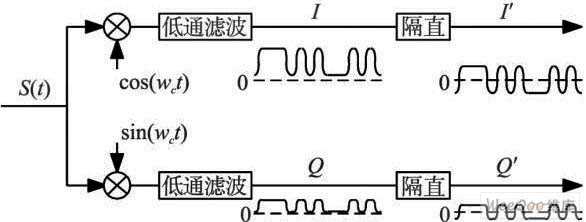

當(dāng)閱讀器接收來自電子標(biāo)簽的信號采用PSK調(diào)制時(shí), 接收信號可以用如下表達(dá)式表示:

式中A0 為信號穩(wěn)定幅度值,, Φm 為調(diào)制相位值(BPSK調(diào)制時(shí)取0或π),, g ( n - m )、頻率偏移,、相位差△φ ,、n0 與對式( 1)的描述相同。

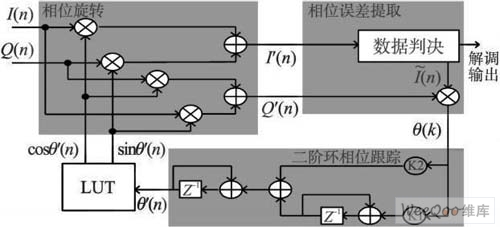

載波頻偏和相差將會影響PSK 信號的正確解調(diào),, 所以在對PSK 信號進(jìn)行解調(diào)時(shí)必須進(jìn)行載波同步,。PSK 解調(diào)的具體實(shí)現(xiàn)電路如圖3所示, 由相位旋轉(zhuǎn),、相位誤差提取和二階相位跟蹤環(huán)三部分組成,。

PSK解調(diào)示意圖

圖3 PSK解調(diào)示意圖

在相位旋轉(zhuǎn)過程中有四個(gè)乘法運(yùn)算, 而若在用硬件實(shí)現(xiàn)時(shí)直接調(diào)用四個(gè)硬件乘法器,, 將會消耗很大的硬件資源,。所以本文在設(shè)計(jì)中只使用一個(gè)乘法器, 然后用一個(gè)計(jì)數(shù)器來控制分時(shí)復(fù)用,, 從而節(jié)省資源,。

為實(shí)現(xiàn)相位跟蹤, 相位誤差提取部分根據(jù)MAP算法來估計(jì)得到相位誤差信號θe ( n ),。θe ( n )反映了環(huán)路跟蹤相位的程度,, 但不能直接用于相位旋轉(zhuǎn),因?yàn)? 1.存在噪聲干擾; 2.由于存在載波頻率偏移,,載波相位誤差會隨時(shí)間積累,。所以需要對θe ( n)進(jìn)行濾波和積分, 進(jìn)而實(shí)現(xiàn)相位跟蹤, 其實(shí)現(xiàn)如圖3中的二階相位跟蹤環(huán)部分所示,。

設(shè)計(jì)中,, K 1、K 2 分別取值1 /256,、1 /8,。用硬件實(shí)現(xiàn)時(shí), 乘K 1,、K 2 的運(yùn)算可以用簡單的右移運(yùn)算來完成,, 而不必調(diào)用復(fù)雜的硬件除法器。

3 解碼器設(shè)計(jì)

解碼器包括FM0解碼器,、M iller解碼器,、CRC 校驗(yàn)器、幀起始超時(shí)檢測和解碼結(jié)果同步輸出控制五個(gè)主要子模塊,。FM 0 /M iller解碼后的數(shù)據(jù)data 若需要進(jìn)行CRC 校驗(yàn),, 則進(jìn)入CRC 校驗(yàn)器進(jìn)行CRC校驗(yàn)并輸出校驗(yàn)結(jié)果。由于幀結(jié)束在有的情況下不能完全確定,, 而需要借助CRC 校驗(yàn)來確定幀的結(jié)尾,, 所以在解碼器r中還有一個(gè)解碼結(jié)果同步輸出子模塊用來控制同步解碼結(jié)果輸出。幀起始超時(shí)檢測模塊是用來進(jìn)行幀起始超時(shí)檢測的,, 當(dāng)輸入有效數(shù)據(jù)后超過規(guī)定時(shí)間沒有檢測到正確的幀起始序列,, 則輸出錯(cuò)誤標(biāo)志脈沖。

3. 1 FM0解碼子模塊

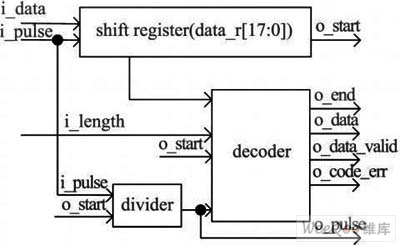

FM0解碼子模塊由幀起始檢測,、FM0 解碼/編碼規(guī)則檢測/幀結(jié)束檢測以及輸出同步脈沖產(chǎn)生三部分組成,, 如圖4所示。

FM0解碼子模塊框圖

圖4 FM0解碼子模塊框圖

幀起始檢測部分中設(shè)有一個(gè)十八位的移位寄存器data_ r[ 17: 0] ,, 當(dāng)檢測到幀起始序列(即data_ r[ 11: 0] = “ 110 100 100 011”) 時(shí),, 幀起始信號o _start輸出一個(gè)脈沖, 并置indecode有效,, 表示開始接收到新的幀數(shù)據(jù); FM0 解碼/編碼規(guī)則檢測/幀結(jié)束檢測部分,, 在indecode有效時(shí), 在解碼同步脈沖信號o_pu lse的同步下對data _r[ 2: 0]進(jìn)行分析判斷,, 若data_r[ 0]與data_r[ 1]相同則輸出o_data= ?1 ,, 反之則輸出o_data= “0”; 同時(shí)檢測da ta_r[ 1]與data_r[ 2] ,, 若兩個(gè)相同,, 則出現(xiàn)了不符合FM0編碼規(guī)則的情況, 輸出編碼規(guī)則錯(cuò)誤標(biāo)志信號o _code_err為“1”; 在o_start脈沖后對i_pu lse進(jìn)行二分頻得解碼輸出同步脈沖o _pulse,, o_pu lse 用于同步解碼過程和解碼后數(shù)據(jù)輸出,。

幀結(jié)束檢測采用計(jì)數(shù)檢測和幀結(jié)尾序列檢測結(jié)合的方法,, 當(dāng)data_r[ 7: 0] = “00 000 000”或接收到的數(shù)據(jù)比特?cái)?shù)到達(dá)幀數(shù)據(jù)長度length則表示檢測到了幀結(jié)尾。但是注意若采用后者的方法,, 由于結(jié)尾有一個(gè)比特的模糊,, 即可能會多接收一個(gè)多余的?1 ,。

3. 2 M iller解碼子模塊

密勒解碼子模塊包括幀前導(dǎo)序列檢測與副載波解調(diào)部分,、密勒解碼部分, 如圖5所示,。電子標(biāo)簽返回閱讀器的數(shù)據(jù)是突發(fā)傳輸?shù)模?每一次數(shù)據(jù)傳輸前有幀前導(dǎo)序列,, 所以在進(jìn)行解碼之前需檢測到該序列。幀前導(dǎo)序列檢測與副載波解調(diào)部分在檢測幀前導(dǎo)序列后,, 對信號進(jìn)行副載波解調(diào),, 得到密勒編碼基帶波形。密勒解碼部分根據(jù)密勒編碼規(guī)則,, 對密勒編碼基帶波形進(jìn)行解碼,, 并檢查傳輸數(shù)據(jù)是否違反編碼規(guī)則, 從而統(tǒng)計(jì)數(shù)據(jù)傳輸質(zhì)量,。

M iller解碼子模塊框圖

圖5 M iller解碼子模塊框圖

幀前導(dǎo)序列檢測與副載波解調(diào)部分首先對接收數(shù)據(jù)碼流進(jìn)行相位翻轉(zhuǎn)檢測,, 于相位翻轉(zhuǎn)(碼流中出現(xiàn)大凹槽或大凸槽)處在相位翻轉(zhuǎn)標(biāo)志信號phase_invert上輸出一個(gè)脈沖。在幀前導(dǎo)序列中,, 只有傳輸比特“1 ”時(shí)符號中間發(fā)生相位翻轉(zhuǎn),, 所以在進(jìn)行幀前導(dǎo)序列檢測時(shí)若檢測到phase_ invert上有一個(gè)脈沖, 便可認(rèn)為碼流中出現(xiàn)了一個(gè)“1” ,。為增強(qiáng)抗干擾能力,, 還需結(jié)合使用一個(gè)計(jì)數(shù)器cnt_ ipu l_sta對輸入數(shù)據(jù)同步脈沖i_pulse 進(jìn)行計(jì)數(shù)以計(jì)量相鄰兩個(gè)相位翻轉(zhuǎn)的時(shí)間間隔, 當(dāng)遇見phase _ invert脈沖或cnt_ipul_sta計(jì)數(shù)到2×M 時(shí)便清零重新計(jì)數(shù),。整個(gè)解調(diào)過程用一個(gè)有限狀態(tài)機(jī)控制,。

經(jīng)過副載波解調(diào), 得到密勒編碼基帶數(shù)據(jù)data及其同步脈沖信號data_pu lse,。在密勒解碼模塊,, 設(shè)置長度為10的移位寄存器data_r[ 9: 0], 在data_pulse的同步下將data 逐位移入data_r[ 9: 0],。隨后根據(jù)data_r[ 9: 0]的內(nèi)容進(jìn)行密勒解碼,。解碼過程中有一個(gè)計(jì)數(shù)器對解碼后的比特進(jìn)行計(jì)數(shù), 當(dāng)計(jì)數(shù)結(jié)果和幀數(shù)據(jù)長度相同或者檢測到幀結(jié)尾序列(即data _ r[ 7: 0] =8’b01 000 000或8’b10 111 111)時(shí),, 則輸出o_end脈沖表示解碼結(jié)束,, 停止解碼, 等待下一幀數(shù)據(jù)的到來,。

4 設(shè)計(jì)實(shí)現(xiàn)與仿真驗(yàn)證

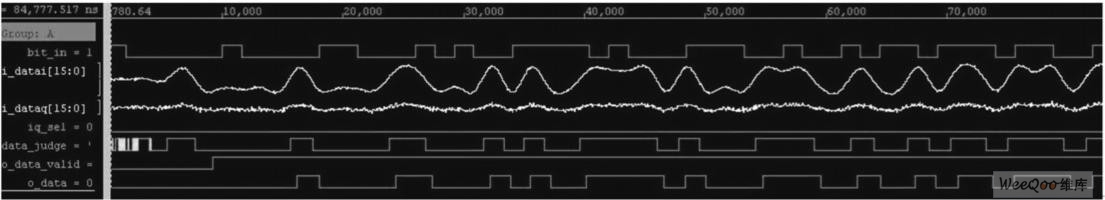

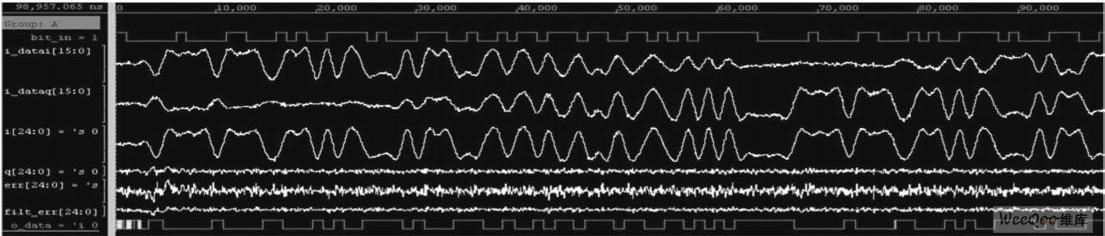

以上設(shè)計(jì)方案采用V er ilog HDL實(shí)現(xiàn),, 并在NCVerilog中進(jìn)行功能仿真,。對解調(diào)器模塊和解碼器模塊的仿真結(jié)果分別如下圖6、圖7,、圖8,、圖9所示。

ASK解調(diào)模塊仿真結(jié)果——相位偏移為10°

圖6 ASK解調(diào)模塊仿真結(jié)果——相位偏移為10°

PSK解調(diào)模塊仿真結(jié)果

圖7 PSK解調(diào)模塊仿真結(jié)果

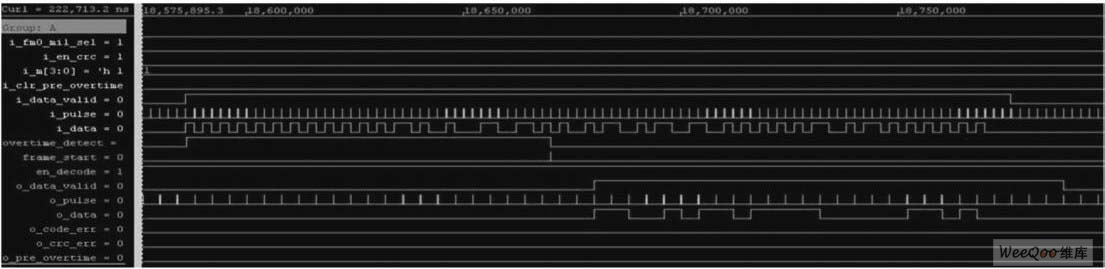

FM 0解碼模塊仿真結(jié)果—— 解碼正確

圖8 FM 0解碼模塊仿真結(jié)果—— 解碼正確

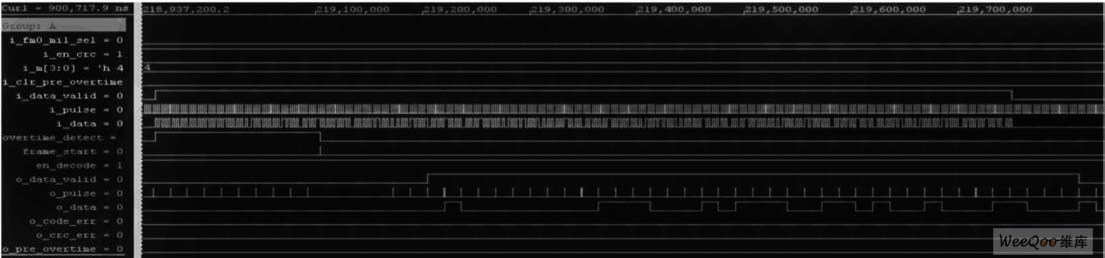

M iller解碼模塊仿真結(jié)果——解碼正確

圖9 M iller解碼模塊仿真結(jié)果——解碼正確

本文還選用A ltera的EP3C16Q240C8N FPGA,,根據(jù)具體應(yīng)用開發(fā)了閱讀器的基帶處理電路板,, FPGA 中包括了嵌入式處理器軟核N IOS II、基帶處理接收端電路RTL和發(fā)送端電路RTL代碼,, 由該基帶處理板與射頻前端電路一起組成UHF RFID 閱讀器的驗(yàn)證平臺,。通過該驗(yàn)證平臺本文完成了基帶處理接收端電路RTL設(shè)計(jì)的原型驗(yàn)證。

軟件仿真結(jié)果表明,, 解調(diào)器能在各種不同相位偏移情況下對接收到的ASK 信號進(jìn)行正確解調(diào),, 對頻率偏移量處于快捕帶內(nèi)的PSK 調(diào)制信號能夠很快實(shí)現(xiàn)載波相位跟蹤進(jìn)而實(shí)現(xiàn)正確解調(diào); 解碼器能夠?qū)φ_的FM0 /M iller輸入數(shù)據(jù)進(jìn)行解碼, 并且可以檢測到幀起始檢測超時(shí)錯(cuò)誤和違反FM0 /M iller編碼規(guī)則錯(cuò)誤的情況,。FPGA 原型驗(yàn)證結(jié)果表明,,整個(gè)閱讀器基帶處理電路包括其接收端電路可以滿足設(shè)計(jì)要求。