Multisim 9的數(shù)字電子鐘設(shè)計(jì)

摘要: 數(shù)字電子鐘是用數(shù)字集成電路構(gòu)成并有數(shù)字顯示特點(diǎn)的一種現(xiàn)代計(jì)數(shù)器,與傳統(tǒng)的機(jī)械計(jì)時(shí)器相比,它具有走時(shí)準(zhǔn)、顯示直觀、無(wú)機(jī)械磨損等,因而廣泛應(yīng)用于車站、碼頭、商店等公共場(chǎng)所。目前,數(shù)字電子鐘的設(shè)計(jì),主要是采用計(jì)數(shù)器等集成電路構(gòu)成,由于所用集成電路多。連線雜亂,不便閱讀。本文采用層次電路設(shè)計(jì),將各單元電路設(shè)計(jì)成層次電路,這樣每個(gè)單元電路和整體電路連線一目了然,既美觀也便于閱讀,還有利于團(tuán)隊(duì)設(shè)計(jì),因每一層次電路為一獨(dú)立電路,便于獨(dú)立設(shè)計(jì)和修改。

關(guān)鍵詞:

Multisim

數(shù)字電子鐘

Abstract:

Key words :

數(shù)字電子鐘是用數(shù)字集成電路構(gòu)成并有數(shù)字顯示特點(diǎn)的一種現(xiàn)代計(jì)數(shù)器,與傳統(tǒng)的機(jī)械計(jì)時(shí)器相比,它具有走時(shí)準(zhǔn)、顯示直觀、無(wú)機(jī)械磨損等,因而廣泛應(yīng)用于車站、碼頭、商店等公共場(chǎng)所。目前,數(shù)字電子鐘的設(shè)計(jì),主要是采用計(jì)數(shù)器等集成電路構(gòu)成,由于所用集成電路多。連線雜亂,不便閱讀。本文采用層次電路設(shè)計(jì),將各單元電路設(shè)計(jì)成層次電路,這樣每個(gè)單元電路和整體電路連線一目了然,既美觀也便于閱讀,還有利于團(tuán)隊(duì)設(shè)計(jì),因每一層次電路為一獨(dú)立電路,便于獨(dú)立設(shè)計(jì)和修改。

1 設(shè)計(jì)任務(wù)

(1)電子鐘能顯示“時(shí)”、“分”、“秒”;

(2)能夠?qū)崿F(xiàn)對(duì)“時(shí)”、“分”、“秒”的校時(shí)。

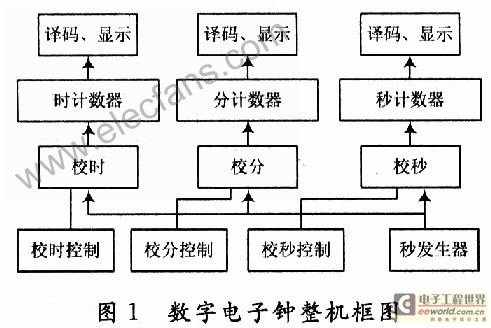

2 整機(jī)框圖

數(shù)字電子鐘主要由秒信號(hào)發(fā)生器、“時(shí)、分、秒”計(jì)數(shù)器、譯碼顯示器、校時(shí)電路等組成。秒信號(hào)發(fā)生器主要由石英晶體振蕩器或555振蕩器分頻后得到;秒、分都是60進(jìn)制,故由60進(jìn)制計(jì)數(shù)器構(gòu)成;時(shí)為24進(jìn)制,即由24進(jìn)制計(jì)數(shù)器構(gòu)成;顯示部分由譯碼和數(shù)碼顯示構(gòu)成;校時(shí)電路由門電路和開(kāi)關(guān)等構(gòu)成。整機(jī)框圖如圖1所示。

數(shù)字電子鐘主要由秒信號(hào)發(fā)生器、“時(shí)、分、秒”計(jì)數(shù)器、譯碼顯示器、校時(shí)電路等組成。秒信號(hào)發(fā)生器主要由石英晶體振蕩器或555振蕩器分頻后得到;秒、分都是60進(jìn)制,故由60進(jìn)制計(jì)數(shù)器構(gòu)成;時(shí)為24進(jìn)制,即由24進(jìn)制計(jì)數(shù)器構(gòu)成;顯示部分由譯碼和數(shù)碼顯示構(gòu)成;校時(shí)電路由門電路和開(kāi)關(guān)等構(gòu)成。整機(jī)框圖如圖1所示。

3 各部分電路設(shè)計(jì)

3.1 秒、分、時(shí)計(jì)數(shù)器

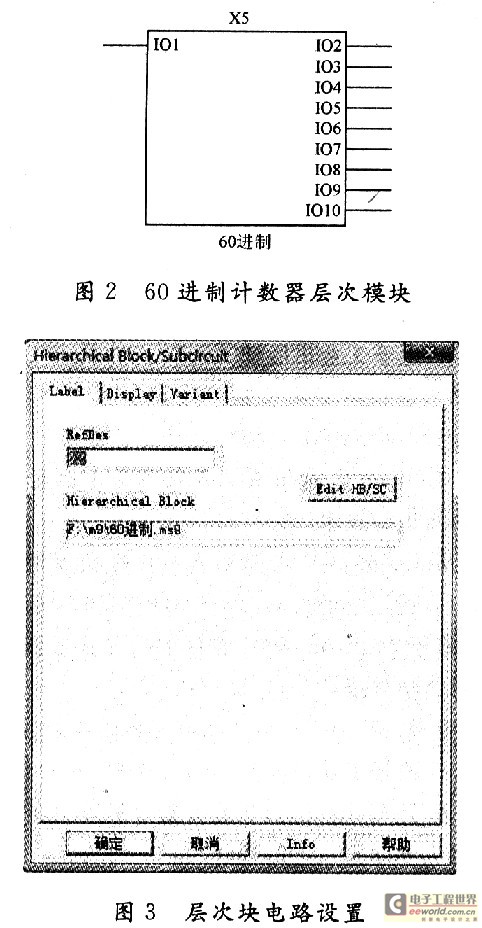

秒、分計(jì)數(shù)采用60進(jìn)制計(jì)數(shù)器,時(shí)采用24進(jìn)制計(jì)數(shù)器。它們都是8個(gè)BCD碼輸出,1個(gè)進(jìn)位輸出,1個(gè)時(shí)鐘脈沖輸入。在設(shè)計(jì)層次電路時(shí),皆可設(shè)計(jì)為1個(gè)輸入端,9個(gè)輸出端。在Multisim仿真軟件中,執(zhí)行Place/New Hierachical Block命令,在fiIe name of Hierachical Block中填入你要設(shè)計(jì)的電路名稱,如“60進(jìn)制計(jì)數(shù)器”等,再根據(jù)需要在輸入、輸出端口數(shù)中填寫所需數(shù)字,點(diǎn)“OK”后,即得如圖2所示電路層次模塊。雙擊它,得到圖3所示窗口,點(diǎn)Edit HB/SC對(duì)其內(nèi)電路進(jìn)行設(shè)計(jì)。若要進(jìn)行修改,同樣采用以上步驟。

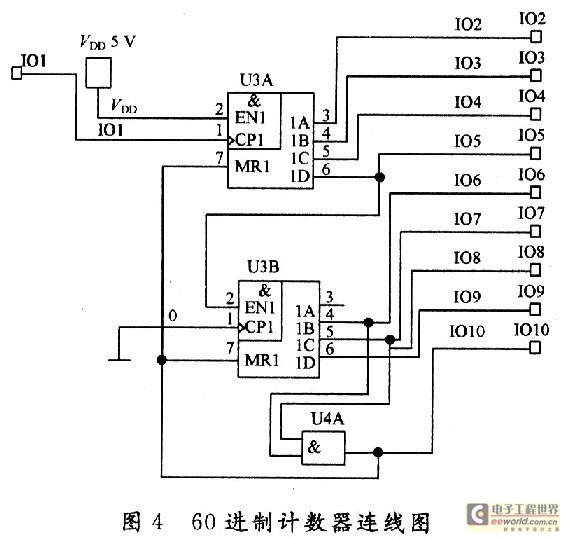

由此,采用4518十進(jìn)制計(jì)數(shù)器,設(shè)計(jì)了60進(jìn)制和24進(jìn)制的計(jì)數(shù)器,計(jì)數(shù)器的內(nèi)部電路分別如圖4、圖5所示。

3.2 校準(zhǔn)電路

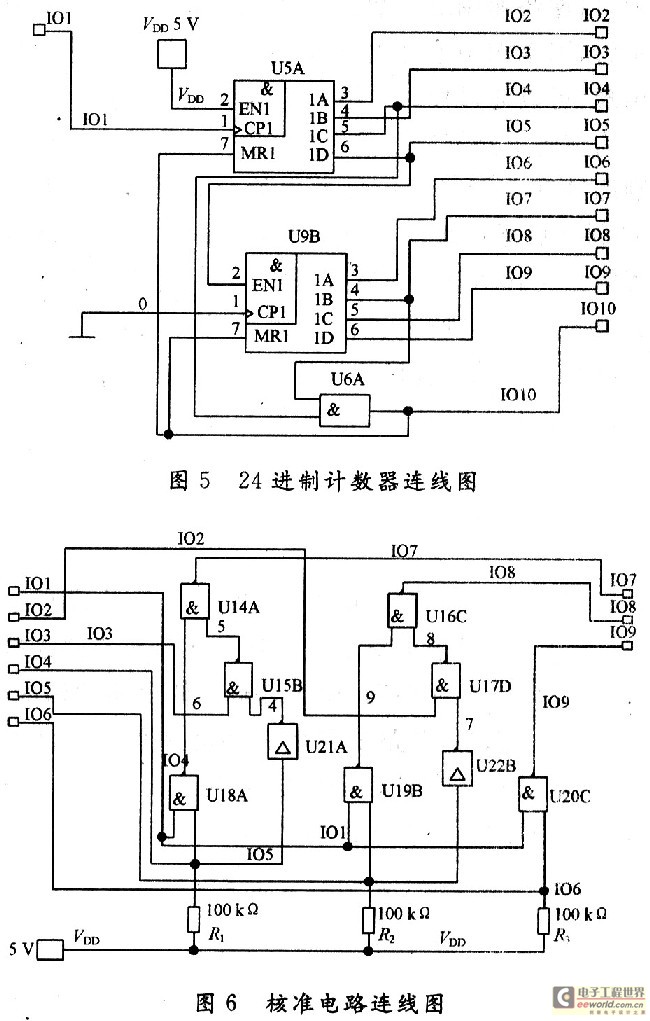

同樣的方法,設(shè)計(jì)校準(zhǔn)電路的層次電路時(shí),設(shè)計(jì)為6個(gè)輸入口、3個(gè)輸出口,其內(nèi)部電路如圖6所示。為便于使用,將校準(zhǔn)開(kāi)關(guān)外接。

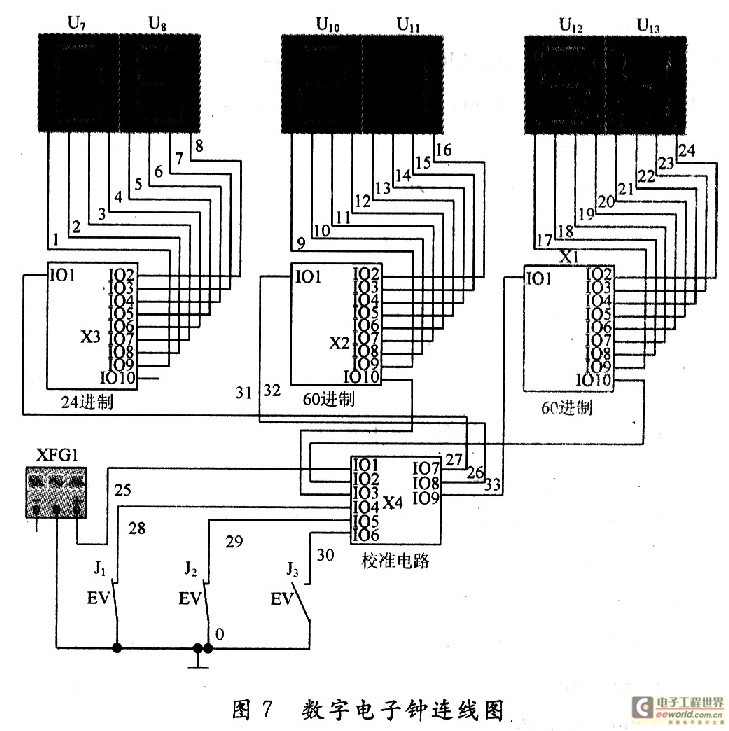

校時(shí)電路工作過(guò)程如圖7所示,正常工作情況下,J3斷開(kāi),J1,J2閉合,秒脈沖進(jìn)入計(jì)數(shù)器。當(dāng)需要對(duì)秒進(jìn)行校正時(shí),閉合和斷開(kāi)J3,直到需要的數(shù)字為止;需要對(duì)分校正時(shí),J3處于閉合的情況下,斷開(kāi)J2,秒脈沖進(jìn)入到分計(jì)時(shí),則分計(jì)數(shù)器快速計(jì)數(shù),直到顯示的時(shí)間為需要的數(shù)字為止,再閉合J2;同理,可以對(duì)時(shí)進(jìn)行校正。

同樣的方法,設(shè)計(jì)校準(zhǔn)電路的層次電路時(shí),設(shè)計(jì)為6個(gè)輸入口、3個(gè)輸出口,其內(nèi)部電路如圖6所示。為便于使用,將校準(zhǔn)開(kāi)關(guān)外接。

校時(shí)電路工作過(guò)程如圖7所示,正常工作情況下,J3斷開(kāi),J1,J2閉合,秒脈沖進(jìn)入計(jì)數(shù)器。當(dāng)需要對(duì)秒進(jìn)行校正時(shí),閉合和斷開(kāi)J3,直到需要的數(shù)字為止;需要對(duì)分校正時(shí),J3處于閉合的情況下,斷開(kāi)J2,秒脈沖進(jìn)入到分計(jì)時(shí),則分計(jì)數(shù)器快速計(jì)數(shù),直到顯示的時(shí)間為需要的數(shù)字為止,再閉合J2;同理,可以對(duì)時(shí)進(jìn)行校正。

4 整機(jī)電路安裝調(diào)試

在Multisim中,執(zhí)行Place/Hierachical Block命令,找到已存儲(chǔ)的層次塊,點(diǎn)打開(kāi)即可出現(xiàn)在電路模扳中,再在元件庫(kù)中找出信號(hào)發(fā)生器和數(shù)碼顯示器。本例中采用現(xiàn)成的信號(hào)發(fā)生器,可以將信號(hào)頻率設(shè)置為較高頻率,以便快速調(diào)節(jié)。數(shù)碼顯示器直接采用16位數(shù)碼顯示管,因本例中不會(huì)出現(xiàn)大于9的數(shù)碼,即使初始可能出現(xiàn),可以通過(guò)校時(shí)電路快速調(diào)節(jié)為所需數(shù)字。

為使各電路接線后能順利工作,對(duì)各層次塊可以先分別測(cè)試其功能。將信號(hào)發(fā)生器分別接入60進(jìn)制和24進(jìn)制計(jì)數(shù)器層次塊,其輸出接數(shù)碼管或示波器看其是否能完成其功能。對(duì)其校準(zhǔn)電路,只有當(dāng)整機(jī)電路接好后,按校準(zhǔn)電路所說(shuō)工作方式,看是否能起到時(shí)、分、秒的校準(zhǔn)。本例中各模塊皆能完成其功能,接好整機(jī)電路后,能完成所需功能,故本例數(shù)字電子鐘滿足設(shè)計(jì)任務(wù)。

5 結(jié)語(yǔ)

采用層次電路設(shè)計(jì)方法,對(duì)數(shù)字電子鐘進(jìn)行了設(shè)計(jì),較好地完成了該電路的設(shè)計(jì)任務(wù)。整機(jī)電路連線美觀,各部分電路功能明確,便于理解整體電路的構(gòu)成、工作原理等。在數(shù)字電路及其他更多的課程中都涉及到較復(fù)雜的電路設(shè)計(jì),若是采用層次電路設(shè)計(jì)方法,既便于對(duì)電路的理解,也便于團(tuán)隊(duì)協(xié)作,共同完成設(shè)計(jì)任務(wù),故而層次電路設(shè)計(jì)方法將會(huì)廣泛地應(yīng)用在大型復(fù)雜電,路系統(tǒng)的設(shè)計(jì)中。

采用層次電路設(shè)計(jì)方法,對(duì)數(shù)字電子鐘進(jìn)行了設(shè)計(jì),較好地完成了該電路的設(shè)計(jì)任務(wù)。整機(jī)電路連線美觀,各部分電路功能明確,便于理解整體電路的構(gòu)成、工作原理等。在數(shù)字電路及其他更多的課程中都涉及到較復(fù)雜的電路設(shè)計(jì),若是采用層次電路設(shè)計(jì)方法,既便于對(duì)電路的理解,也便于團(tuán)隊(duì)協(xié)作,共同完成設(shè)計(jì)任務(wù),故而層次電路設(shè)計(jì)方法將會(huì)廣泛地應(yīng)用在大型復(fù)雜電,路系統(tǒng)的設(shè)計(jì)中。

此內(nèi)容為AET網(wǎng)站原創(chuàng),未經(jīng)授權(quán)禁止轉(zhuǎn)載。