高速數(shù)字設(shè)計(jì)" title="高速數(shù)字設(shè)計(jì)">高速數(shù)字設(shè)計(jì)人員面臨的一個(gè)挑戰(zhàn)就是處理其電路板上的過沖、下沖、錯(cuò)配阻抗振鈴、抖動(dòng)分布和串?dāng)_問題。這些問題都可歸入信號完整" title="信號完整">信號完整性范疇。許多高速設(shè)計(jì)人員都使用輸入/輸出緩沖信息規(guī)范 (IBIS" title="IBIS">IBIS) 建模語言來預(yù)見并解決信號完整性問題。該建模語言自 20 世紀(jì) 90 年代以來便得到廣泛的運(yùn)用,并已發(fā)展成為一種正式的標(biāo)準(zhǔn):EIA-ANSI 656-B。IBIS 論壇2008 年 8 月發(fā)布的第 5 版標(biāo)準(zhǔn)仍然盛行。IBIS 使用電流-電壓 (I-V) 和電壓-時(shí)間 (V-t) 數(shù)據(jù)表來描述某個(gè)器件的 I/O 引腳特性。廠商們通過仿真或測量其器件 I/O 單元生成這些表。

對于那些現(xiàn)在高達(dá) 20 Gbits/秒時(shí)鐘頻率的高速設(shè)計(jì)來說,我能夠理解對于這類系統(tǒng)仿真工具的需求。IBIS 使得 SPICE 仿真選項(xiàng)顯得不那么重要,因?yàn)榉抡鏁r(shí)間大大縮短,并且擁有同樣的準(zhǔn)確度。我所說的 IBIS 仿真時(shí)間更短,是相對于一個(gè)大型 PCB 系統(tǒng)需要數(shù)天或數(shù)周時(shí)間來完成一次晶體管級 SPICE 仿真而言的,其執(zhí)行一次 IBIS 仿真只需數(shù)分鐘或幾小時(shí)的時(shí)間。通過一次 IBIS 仿真,您可以生成許多傳輸線響應(yīng)和眼圖。

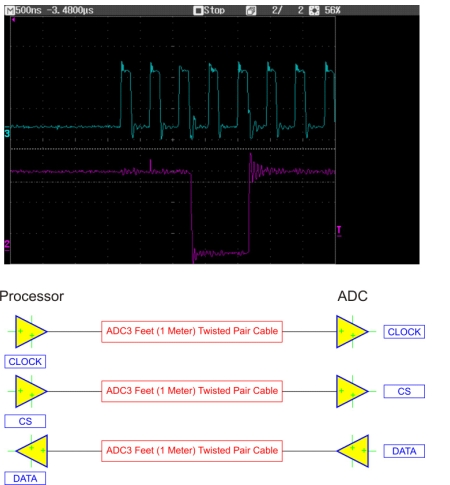

IBIS 格式已經(jīng)表明了其在高速應(yīng)用行業(yè)中的價(jià)值。然而,它讓我真正感到吃驚的地方是廣大客戶現(xiàn)在正要求提供對更低頻率器件(例如:低于 40 MHz 的時(shí)鐘器件)的 IBIS 支持。最初,我以為組件工程師們一直試圖標(biāo)準(zhǔn)化其校驗(yàn)表。現(xiàn)在,我并不那么確定了。即使在更低頻率下,我們也面臨許多信號完整性問題,這是因?yàn)閿?shù)字信號邊緣速率。這些快速邊緣速率負(fù)責(zé)振鈴的時(shí)鐘信號,從而引起一條命令甚至 ADC" title="ADC">ADC 突發(fā) 2 增益的錯(cuò)譯。IC 廠商擁有非常成熟的 SPICE 仿真宏模型,可用于精密器件,但是他們正緊跟我們的 IBIS 數(shù)字 I/O 模型庫。圖 1 描述了一個(gè) IBIS 模型仿真非常有效的例子。

圖1:ADC處理器時(shí)鐘信號(CH3)和處理器上ADC的數(shù)據(jù)信號(CH12)。

圖1中,設(shè)計(jì)人員并未注意線路阻抗。該圖顯示了系統(tǒng)中 ADC 的測得結(jié)果。ADC和處理器均位于其各自的板上,設(shè)計(jì)人員只是簡單地通過一條 1 米長的 CAT-5 雙絞線將兩塊板連接到一起。在圖 1 中,處理器的時(shí)鐘信號頻率 (CH3) 為 2.25 MHz。該 ADC 使用這一信號來將數(shù)據(jù)傳輸同步回處理器 (CH2)。

最初,設(shè)計(jì)人員認(rèn)為這兩個(gè)器件之間的慢時(shí)鐘速度不會引起端接問題。然而,時(shí)鐘和數(shù)據(jù)信號端接方法會形成許多超出規(guī)定高電平和低電平閾值(過沖和下沖)的信號,存在錯(cuò)誤邊緣(振鈴)的信號并降低操作余量(弱化眼圖)的信號。

IBIS 仿真來幫忙!在您將電路實(shí)現(xiàn)為硬件以前可節(jié)省時(shí)間并降低成本。在進(jìn)行原型設(shè)計(jì)以前,您對某種設(shè)計(jì)進(jìn)行仿真時(shí),廠商提供的 IBIS 模型以及您電路板的模型都是您工具箱中有用的東西。信號完整性問題對您的高速系統(tǒng)和低速系統(tǒng)都會產(chǎn)生影響。利用早期階段的仿真電路分析,您可以給您的系統(tǒng)施加許多不同的條件,以防止并檢測常見信號完整性問題。